# Troubleshooting Guide

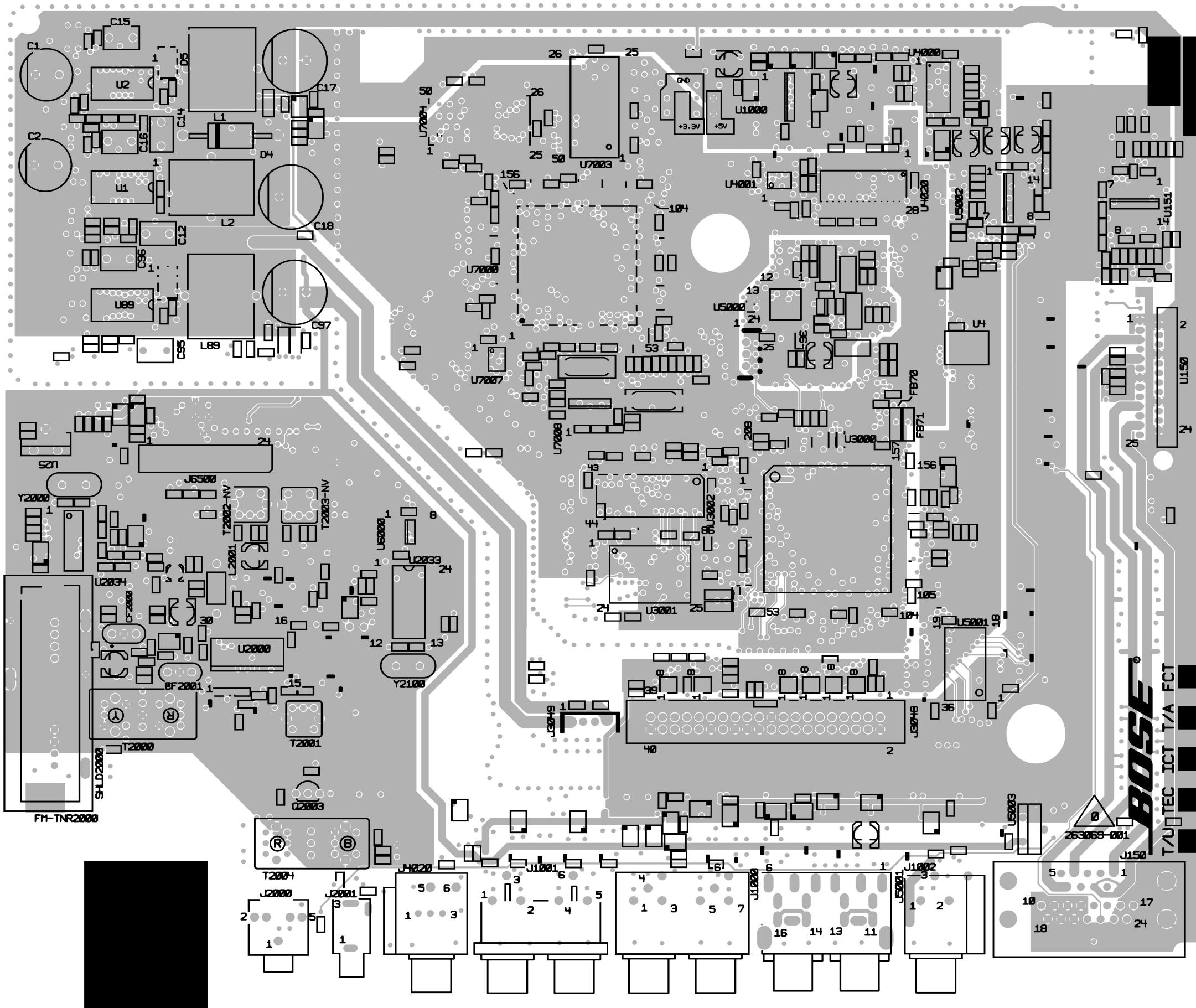

## 3.2.1 Home Entertainment System

## 3.2.1 GS Home Entertainment System

(US/Canada, European, UK, Australia, Japan

and Dual Voltage Versions)

# CONTENTS

|                                                                                 |              |

|---------------------------------------------------------------------------------|--------------|

| <b>3•2•1 and 3•2•1 GS Home Entertainment System Differences .....</b>           | <b>2</b>     |

| <b>Software Update Information .....</b>                                        | <b>2</b>     |

| <b>Safety Information .....</b>                                                 | <b>3</b>     |

| <b>Electrostatic Discharge Sensitive (ESDS) Device Handling .....</b>           | <b>3</b>     |

| <b>Theory of Operation .....</b>                                                | <b>4-21</b>  |

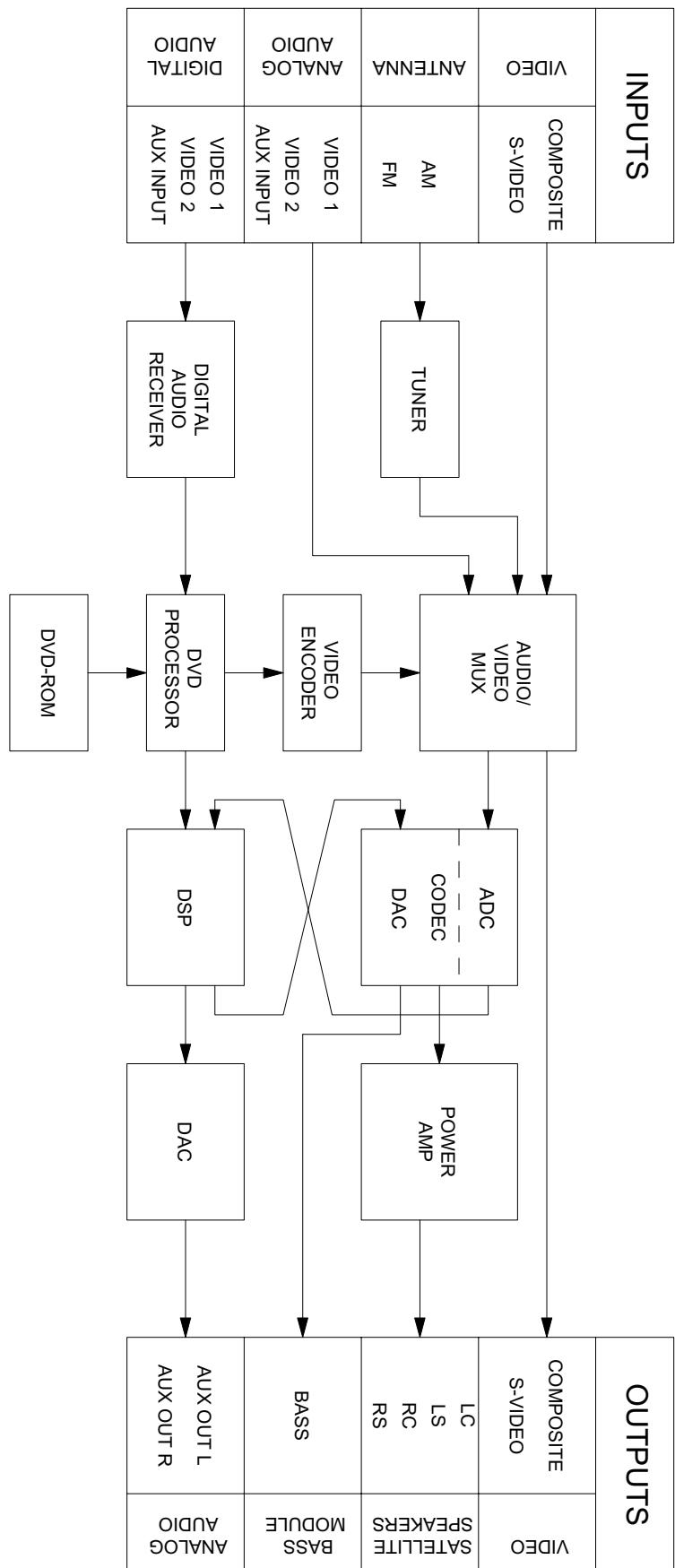

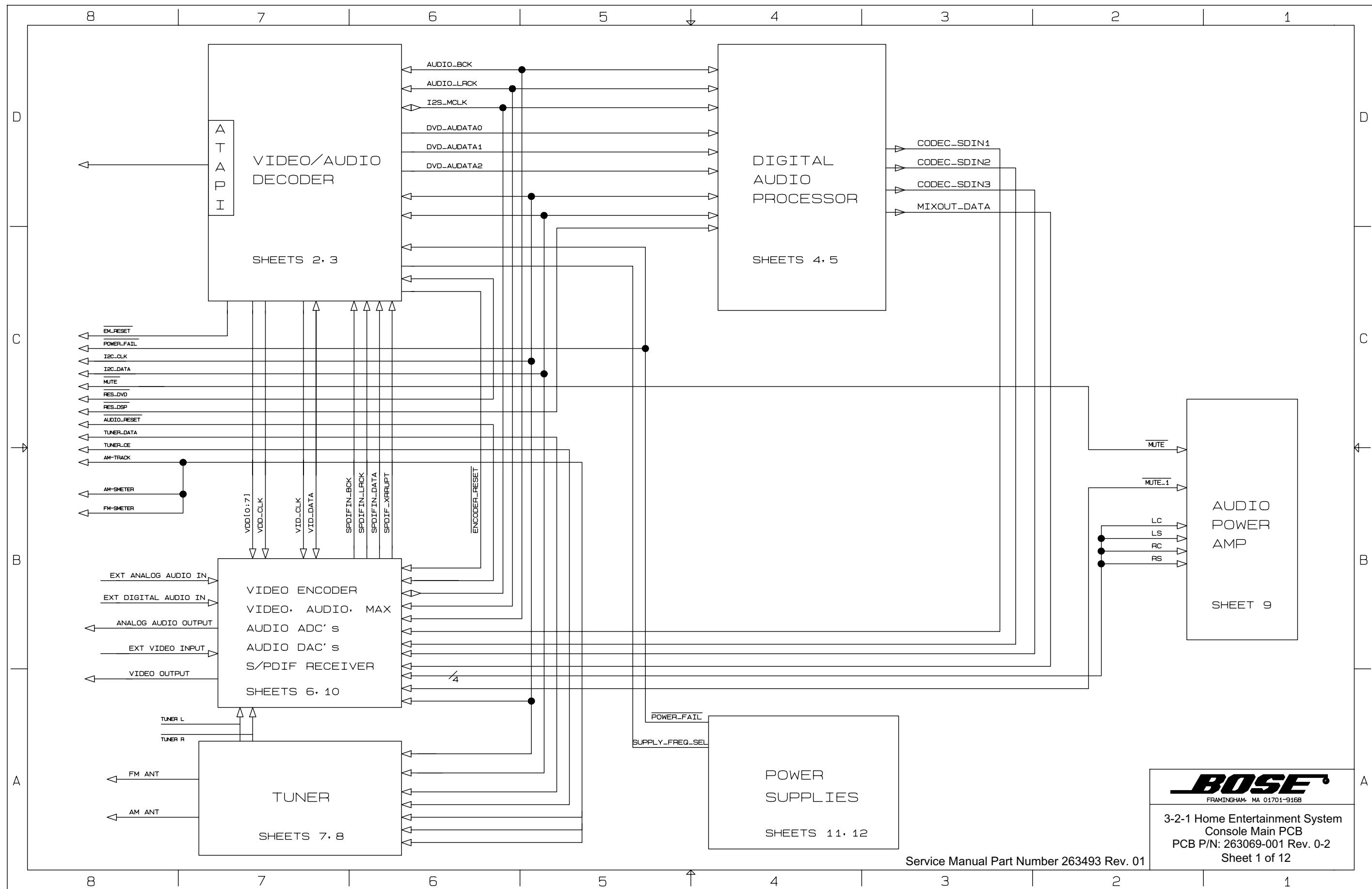

| Figure 1. 3-2-1 Console Block Diagram .....                                     | 22           |

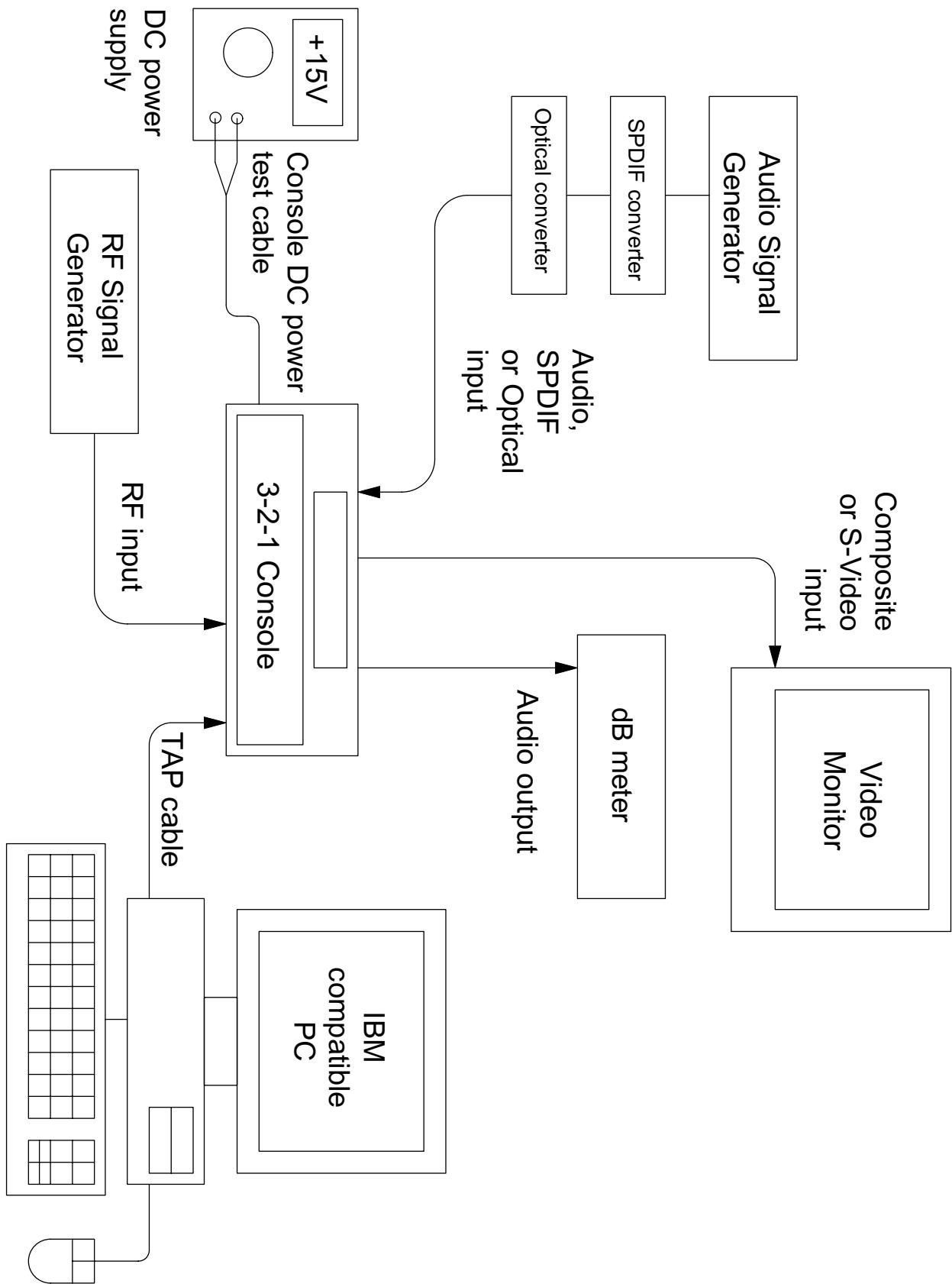

| Figure 2. 3•2•1 Console Test Setup Diagram .....                                | 23           |

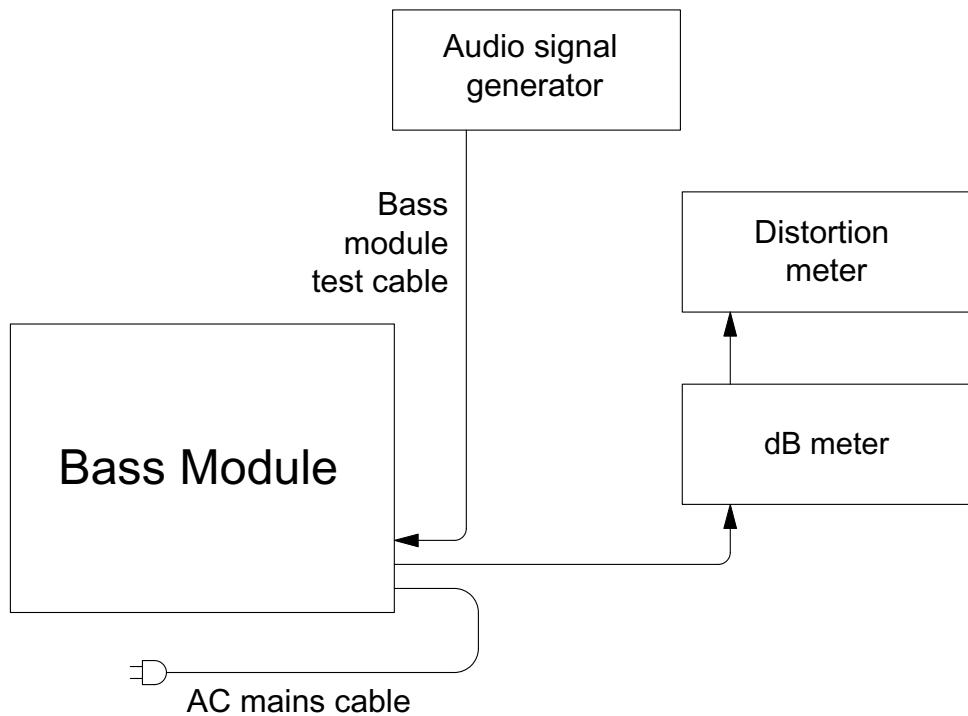

| Figure 3. 3•2•1 Bass Module Test Setup Diagram .....                            | 24           |

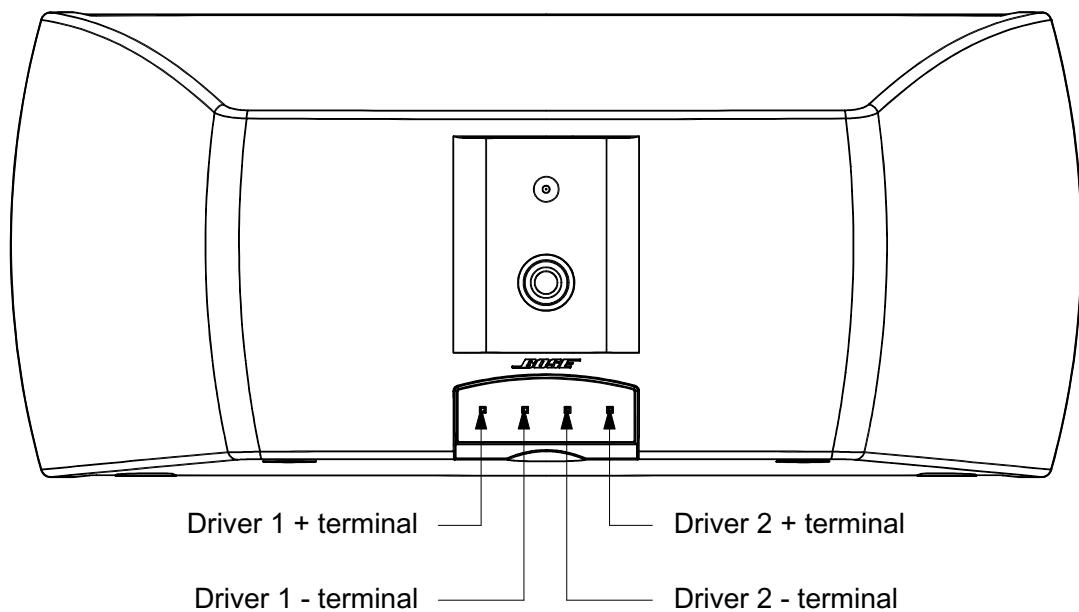

| Figure 4. 3•2•1 and 3•2•1 GS Satellite Speaker Wiring Diagram .....             | 24           |

| <b>Test Procedures .....</b>                                                    | <b>25-35</b> |

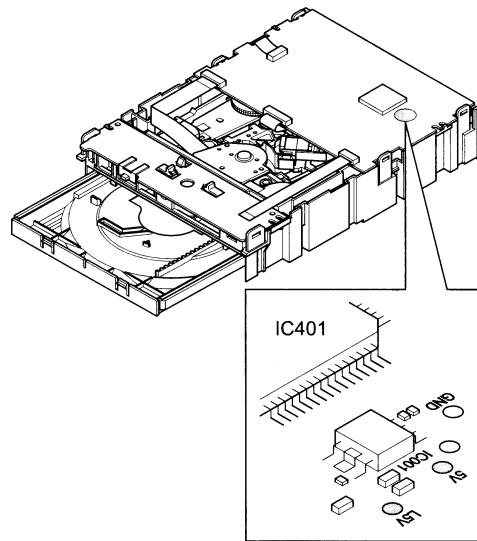

| Figure 5. Laser Voltage Test Points .....                                       | 27           |

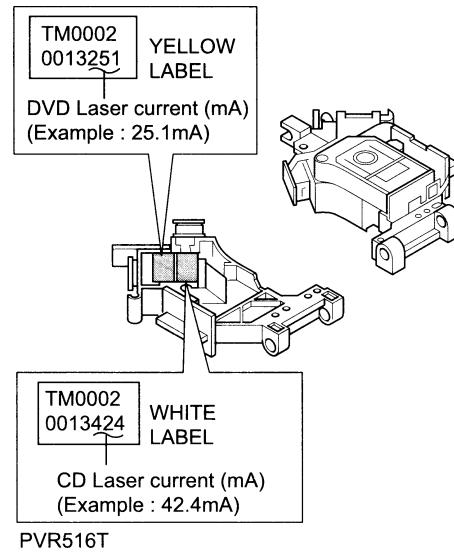

| Figure 6. Laser Current Rating Label .....                                      | 27           |

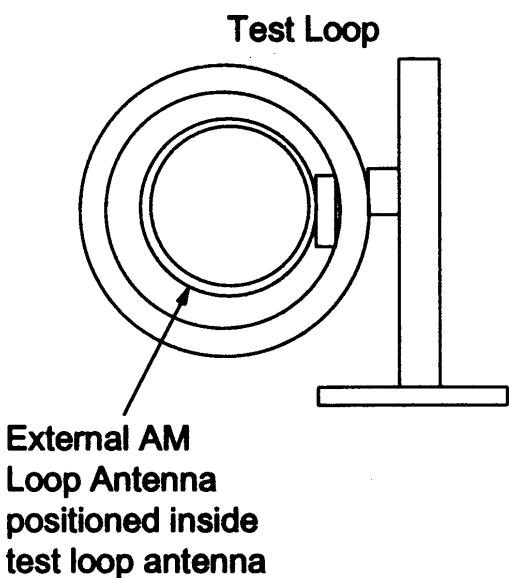

| Figure 7. AM Loop Antenna Test Setup .....                                      | 28           |

| <b>Console Main PCB troubleshooting .....</b>                                   | <b>36</b>    |

| <b>Test Cables .....</b>                                                        | <b>36</b>    |

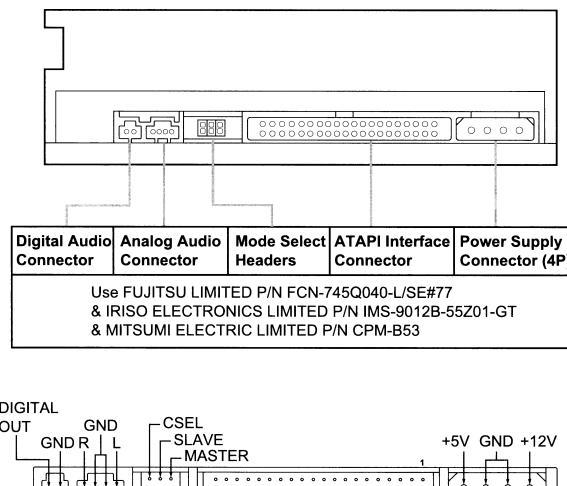

| Figure 8. DVD Mechanism Rear Panel .....                                        | 36           |

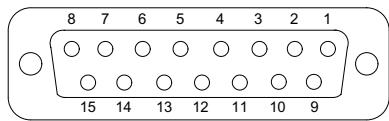

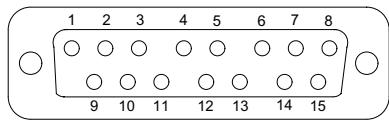

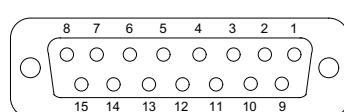

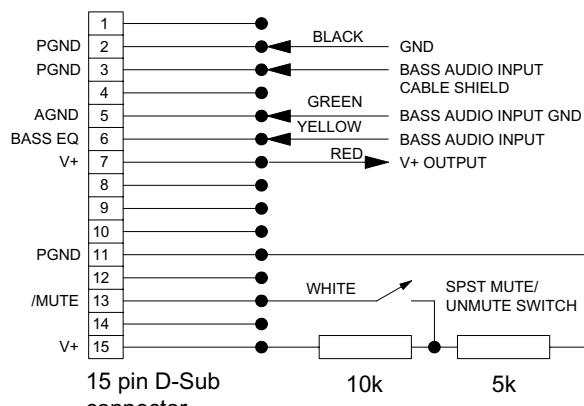

| Figure 9. Bass Module Test Cable Wiring .....                                   | 37           |

| <b>Bass Module Test cable .....</b>                                             | <b>37-38</b> |

| <b>3•2•1 System Date of Manufacture Information .....</b>                       | <b>38</b>    |

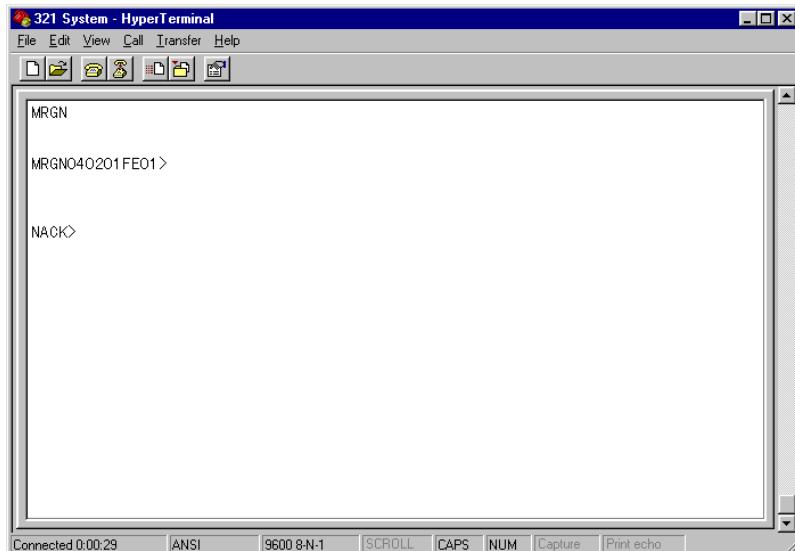

| <b>Checking Console Firmware Revisions .....</b>                                | <b>39</b>    |

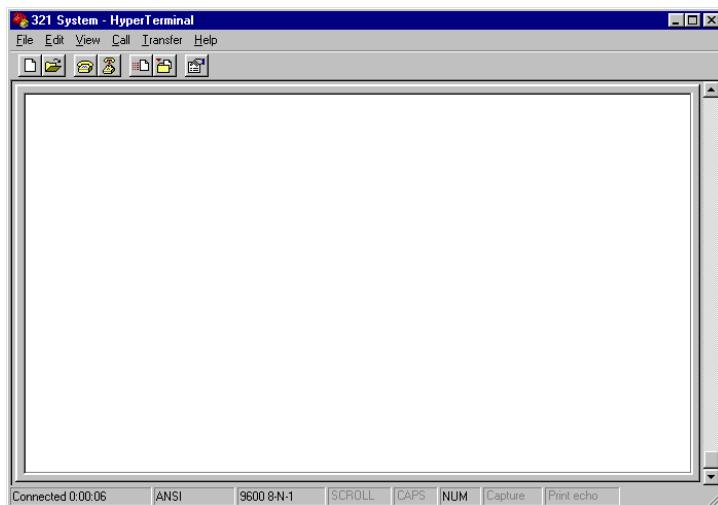

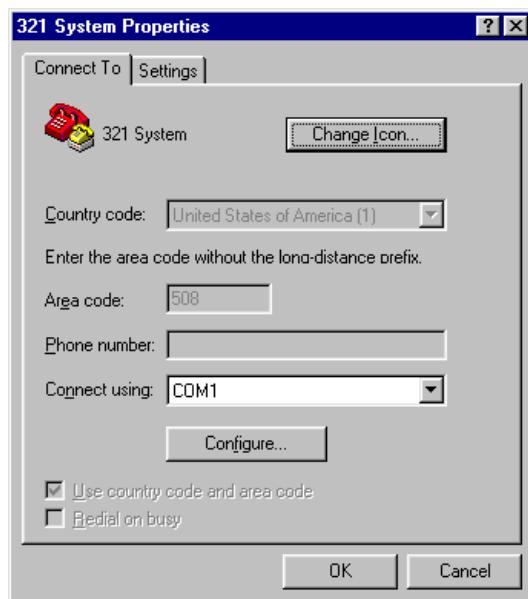

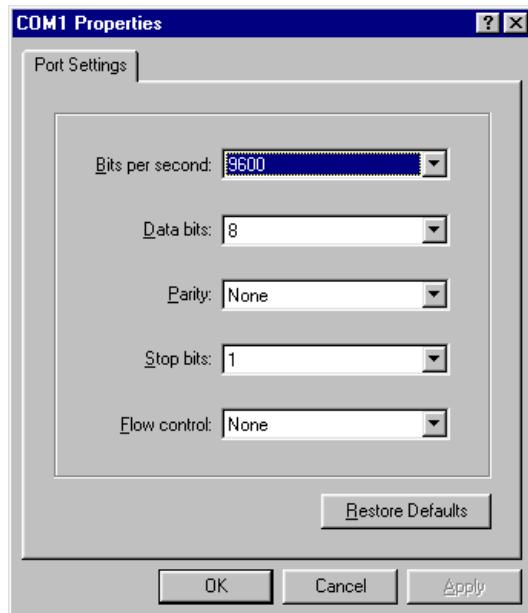

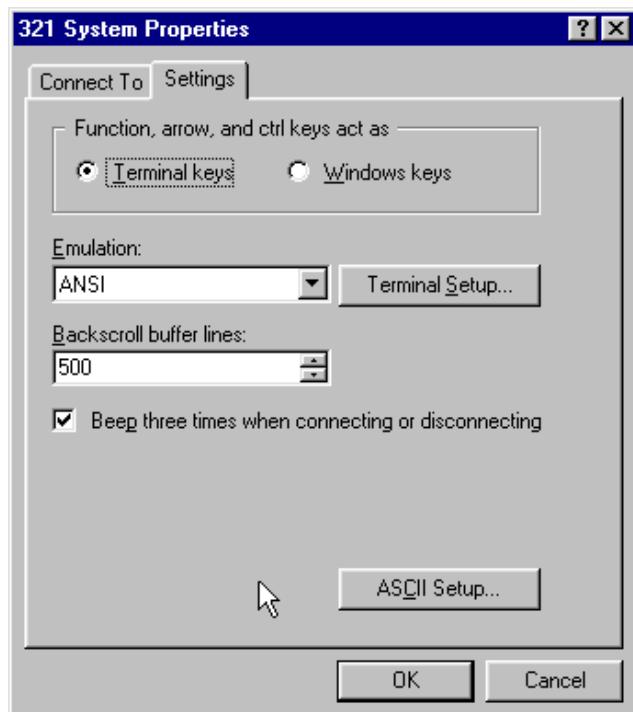

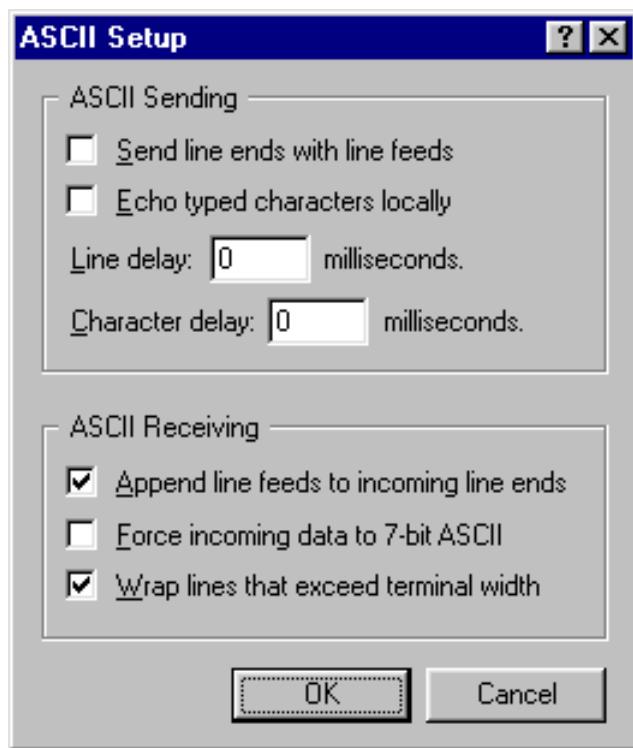

| <b>Computer Setup Procedure .....</b>                                           | <b>40-41</b> |

| <b>TAP Commands .....</b>                                                       | <b>43-51</b> |

| <b>Tuner S-Meter Hexidecimal to Decimal to Voltage Conversion Charts: .....</b> | <b>52-54</b> |

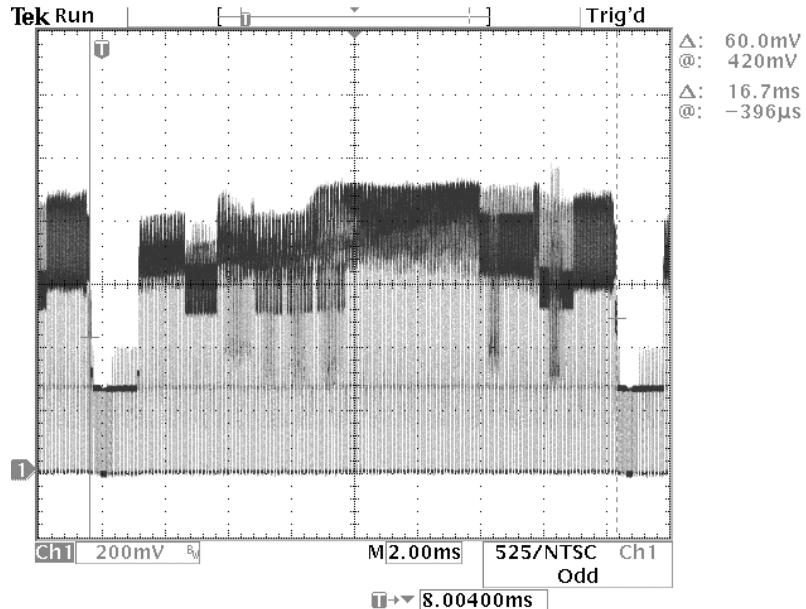

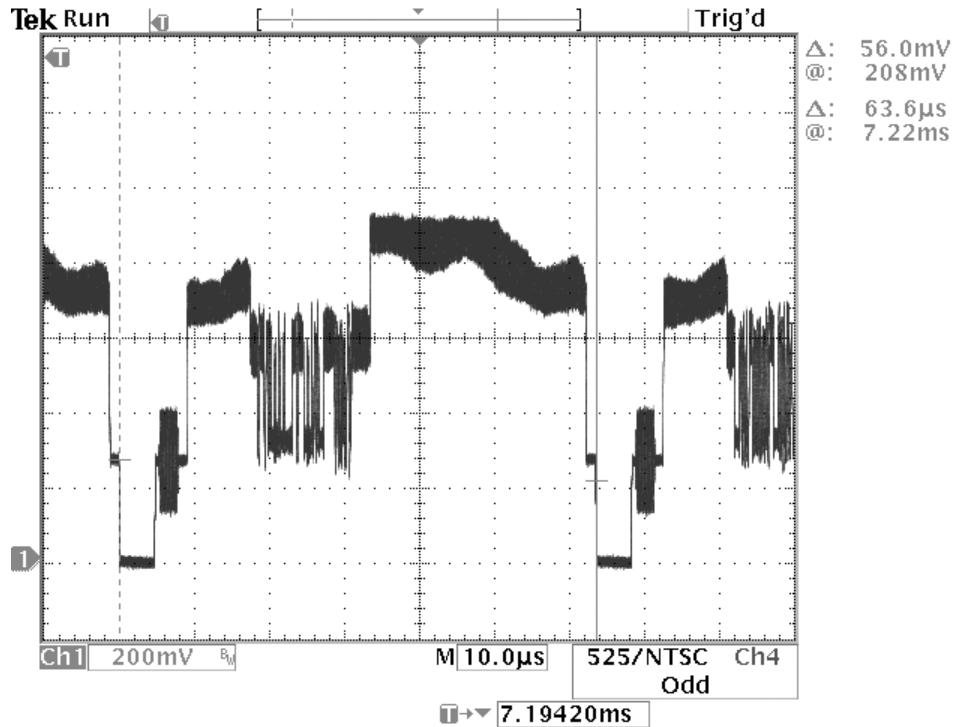

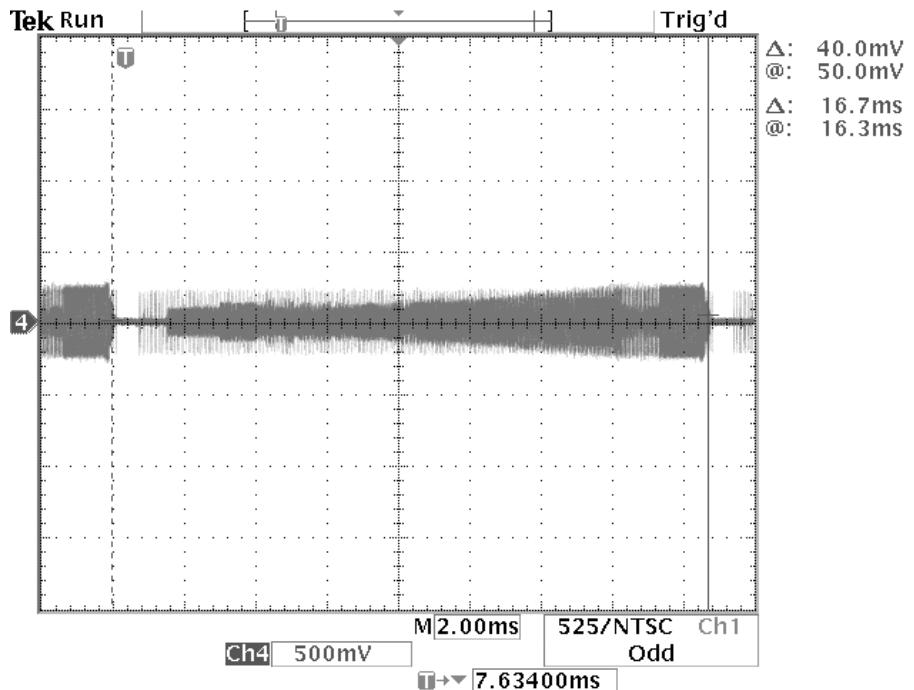

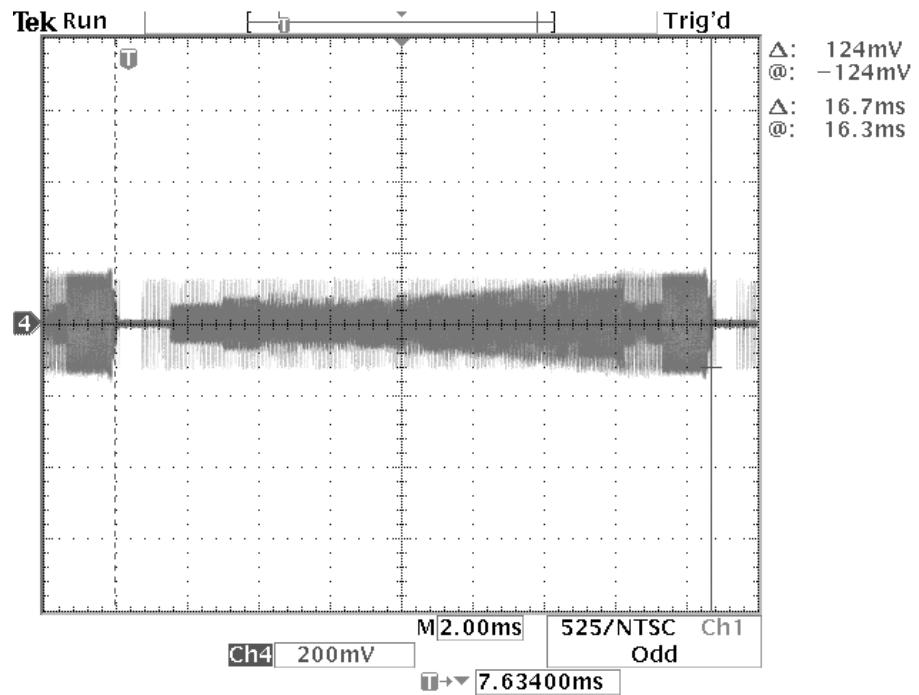

| <b>Console Main PCB Video Troubleshooting and Waveforms .....</b>               | <b>55-61</b> |

| <b>Bass Module Troubleshooting Information .....</b>                            | <b>62</b>    |

| <b>Changing the 3•2•1 Console Region Code .....</b>                             | <b>62-63</b> |

| Table 1. Region Code Tap Commands and Responses .....                           | 63           |

| <b>Parental Control Information .....</b>                                       | <b>64</b>    |

| Table 2. 3•2•1 Console DVD Parental Control Rating Codes .....                  | 64           |

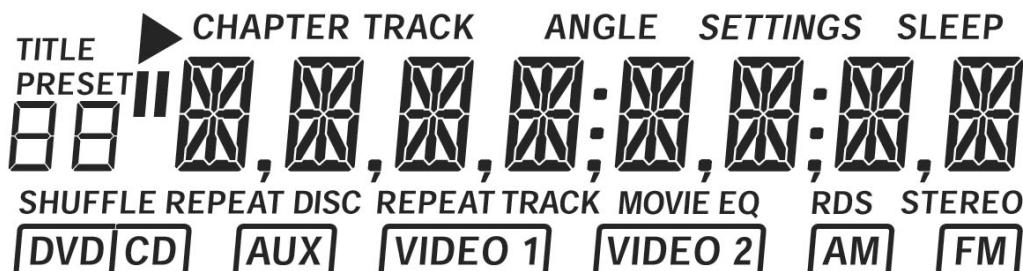

| <b>Console Display Test .....</b>                                               | <b>64</b>    |

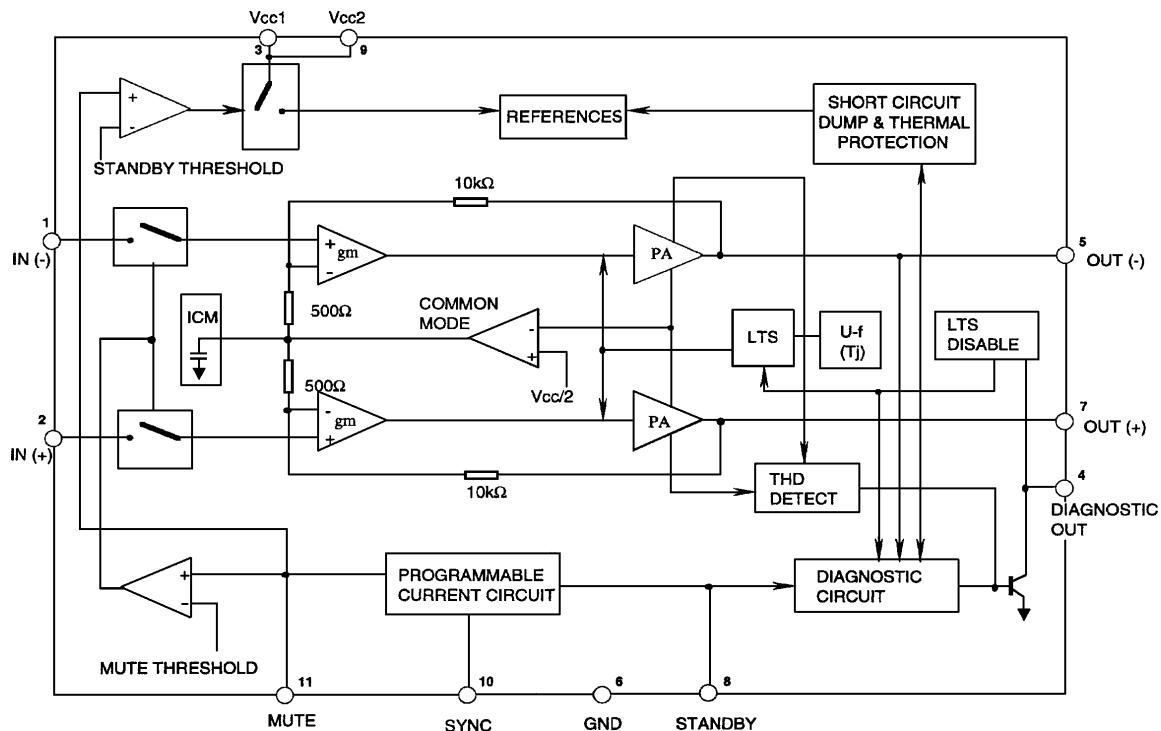

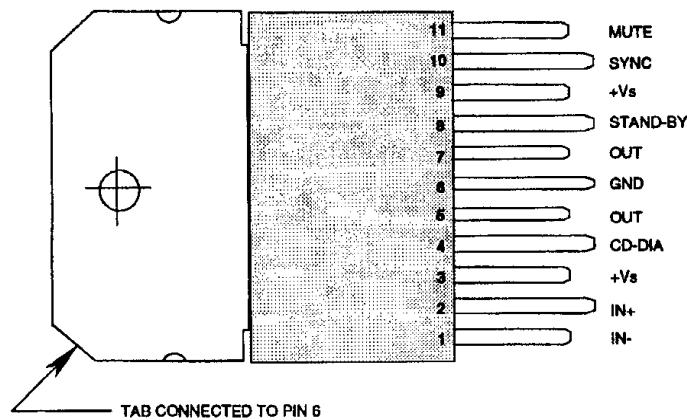

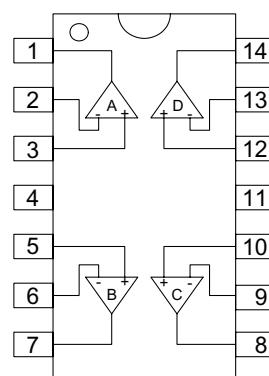

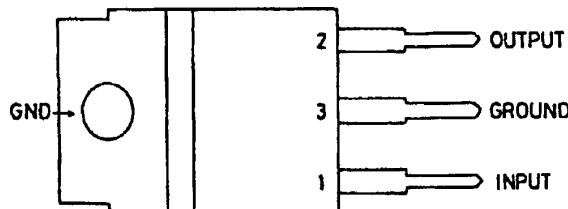

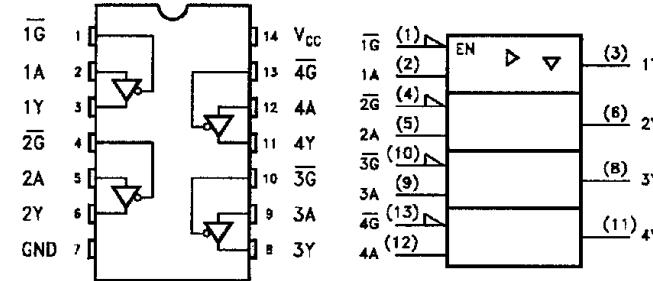

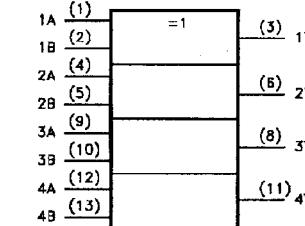

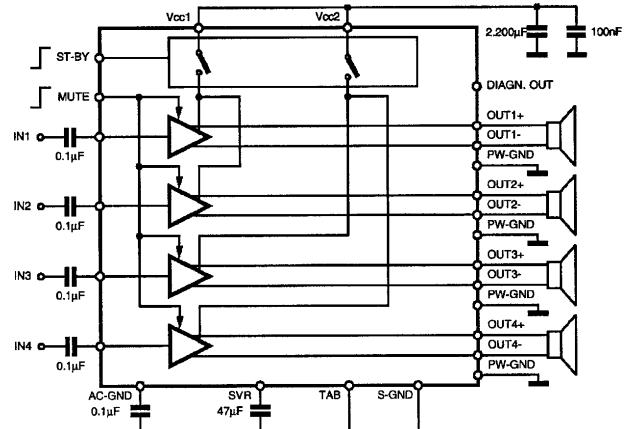

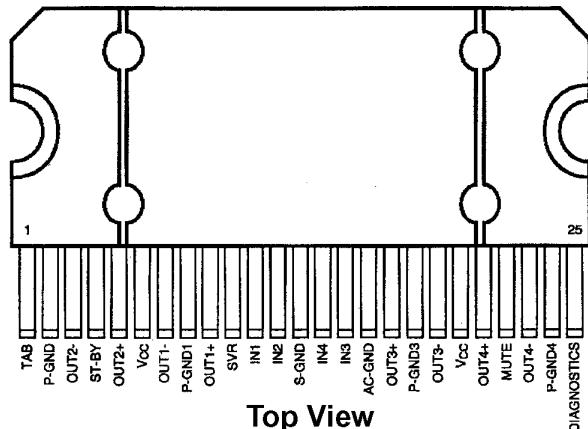

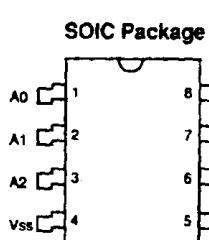

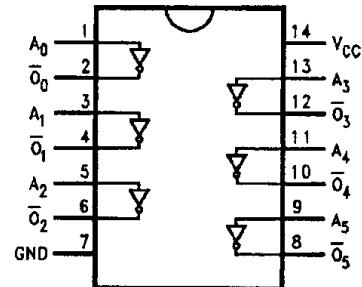

| <b>Integrated Circuit Diagrams .....</b>                                        | <b>65-79</b> |

### **3•2•1 and 3•2•1 GS Home Entertainment System Differences**

The 3•2•1 and 3•2•1 GS (Gemstone) home entertainment systems share the same basic components. The bass module and bass module cable are identical. The console uses the same electronic parts and most of the same chassis parts. The differences in the console are the console firmware and the color of the silver front bezel and DVD drawer bezel. The arrays used on the two systems are different. The standard 3•2•1 system uses the larger 60mm driver arrays, and are only available in graphite. The 3•2•1 GS arrays utilize the smaller 50mm Jewel Cube® driver. These arrays are available in graphite and silver.

### **Software Update Information**

The firmware located in the main PCB and display PCB's microprocessors can be updated by means of an update CD. These update CDs are available from Bose® Product and Technical Support at 800-233-4408 (Bose service centers only) or 800-367-4008 (Bose system owners) and are automatically sent out to customers who have purchased the 3-2-1 system, filled out and returned the software update card that came with their system literature. Service centers can also download an ISO image of the latest firmware update file from the Service web site at <http://serviceops.bose.com> and burn it onto a CD for use as an update disc.

Once you have the CD, simply power up the console, press the stop/eject button on the console, place the update CD into the drawer and close it and the update process will begin. When the process is complete you may remove the update CD.

Check to verify that both the display PCB firmware and the main PCB firmware have updated properly. You can do this by using the TAP commands or by a series of button presses on the console front panel. Both of these methods are outlined in the Appendix.

**CAUTION: The Bose 3•2•1 and 3•2•1 GS Home Entertainment Systems

contain no user-serviceable parts. To prevent warranty infractions,

refer servicing to warranty service stations or factory service.**

#### **PROPRIETARY INFORMATION**

THIS DOCUMENT CONTAINS PROPRIETARY INFORMATION OF

BOSE CORPORATION WHICH IS BEING FURNISHED ONLY FOR

THE PURPOSE OF SERVICING THE IDENTIFIED BOSE PRODUCT

BY AN AUTHORIZED BOSE SERVICE CENTER OR OWNER OF

THE BOSE PRODUCT, AND SHALL NOT BE REPRODUCED OR

USED FOR ANY OTHER PURPOSE.

# SAFETY INFORMATION

1. Parts that have special safety characteristics are identified by the  symbol on schematics or by special notes on the parts list. Use only replacement parts that have critical characteristics recommended by the manufacturer.

2. Make leakage current or resistance measurements to determine that exposed parts are acceptably insulated from the supply circuit before returning the unit to the customer. Use the following checks to perform these measurements:

**A. Leakage Current Hot Check**-With the unit completely reassembled, plug the AC line cord directly into a 120V AC outlet. (Do not use an isolation transformer during this test.) Use a leakage current tester or a metering system that complies with American National Standards Institute (ANSI) C101.1 "Leakage Current for Appliances" and Underwriters Laboratories (UL) 6500 / IEC 60056 paragraph 9.1.1. With the unit AC switch first in the ON position and then in OFF position, measure from a known earth ground (metal waterpipe, conduit, etc.) to all exposed metal parts of the unit (antennas, handle bracket, metal cabinet, screwheads, metallic overlays, control shafts, etc.), especially any exposed metal parts that offer an electrical return path to the chassis. Any current measured must not exceed 0.5 milliamp. Reverse the unit power cord plug in the outlet and repeat test. ANY MEASUREMENTS NOT WITHIN THE LIMITS SPECIFIED HEREIN INDICATE A POTENTIAL SHOCK HAZARD THAT MUST BE ELIMINATED BEFORE RETURNING THE UNIT TO THE CUSTOMER.

**B. Insulation Resistance Test Cold Check**-(1) Unplug the power supply and connect a jumper wire between the two prongs of the plug. (2) Turn on the power switch of the unit. (3) Measure the resistance with an ohmmeter between the jumpered AC plug and each exposed metallic cabinet part on the unit. When testing 3 wire products, the resistance measured to the product enclosure should be between 2 and infinite M<sub>Ω</sub>hms. Also, the resistance measured to exposed input/output connectors should be between 4 and infinite M<sub>Ω</sub>hms. When testing 2 wire products, the resistance measured to exposed input/output connectors should be between 4 and infinite M<sub>Ω</sub>hms. If it is not within the limits specified, there is the possibility of a shock hazard, and the unit must be repaired and rechecked before it is returned to the customer.

## ELECTROSTATIC DISCHARGE SENSITIVE (ESDS) DEVICE HANDLING

This unit contains ESDS devices. We recommend the following precautions when repairing, replacing or transporting ESDS devices:

- Perform work at an electrically grounded work station.

- Wear wrist straps that connect to the station or heel straps that connect to conductive floor mats.

- Avoid touching the leads or contacts of ESDS devices or PC boards even if properly grounded. Handle boards by the edges only.

- Transport or store ESDS devices in ESD protective bags, bins, or totes. Do not insert unprotected devices into materials such as plastic, polystyrene foam, clear plastic bags, bubble wrap or plastic trays.

# THEORY OF OPERATION

## 1.0 Overview

**Note:** Refer to console schematic sheets for the following information. The information inside the brackets [ ] is the grid location on the schematic sheet for the component.

The 3-2-1 Home Entertainment system is a single-zone system consisting of the following components:

- Bass module with woofer, bass amplifier and system power supply

- Console with display and controller, IR remote receiver, DVD Player, video and audio decoders, AM/FM tuner, external video and audio source select, Videostage® audio channel expansion, spatial and array speaker processing, speaker equalization, dynamic equalization, and amplifiers for the array elements

- Two two-driver satellite speaker arrays

- IR remote transmitter

The basic elements of the console are:

- Display and display controller assembly

- DVD loader mechanism and control electronics

- DVD manager, Video and Audio decode circuit (DVD back end)

- Video encoder (video DAC)

- AM/FM Tuner

- Audio, Video source select circuitry

- External Audio, Video Inputs, Line Out, Video Out

- Audio Processor (DSP)

- Array Power Amplifiers

- Power Conditioning Circuits

## 2.0 Power Supply Electronics

| Node Name | Voltage | Type      | Input  | Outputs                                                                                                                |

|-----------|---------|-----------|--------|------------------------------------------------------------------------------------------------------------------------|

| V_RAW     | +16     | ~Linear   | 120VAC | Power Amp, +12V, +10V, +5.1V, +3.3V                                                                                    |

| +12V      | +11.5   | Switching | V_RAW  | DVD drive motors, +9V                                                                                                  |

| +10V      | +10     | Linear    | V_RAW  | AM/FM tuner, FM front-end                                                                                              |

| +9V       | +9      | Linear    | +12    | Sallen-and-Key Filter opamps, Opamp package with "Codec_bias", Bass eq output buffer, and Analog input buffers, AV Mux |

| +5V       | +5      | Switching | V_RAW  | DVD drive logic, Display Board, CODEC, Stereo DAC, SPDIF IC, EEPROM, RDS IC                                            |

| +3.3V     | +3.3    | Switching | V_RAW  | DSP, CS98000 I/O, Flash, DRAM IC's, Quad Inverter, Quad XOR, CODEC, SPDIF, MUX, Tuner PLL IC, Video DAC, 2.5V          |

| +2.5V     | +2.5    | Linear    | +3.3   | CS98000 core, PLL circuits                                                                                             |

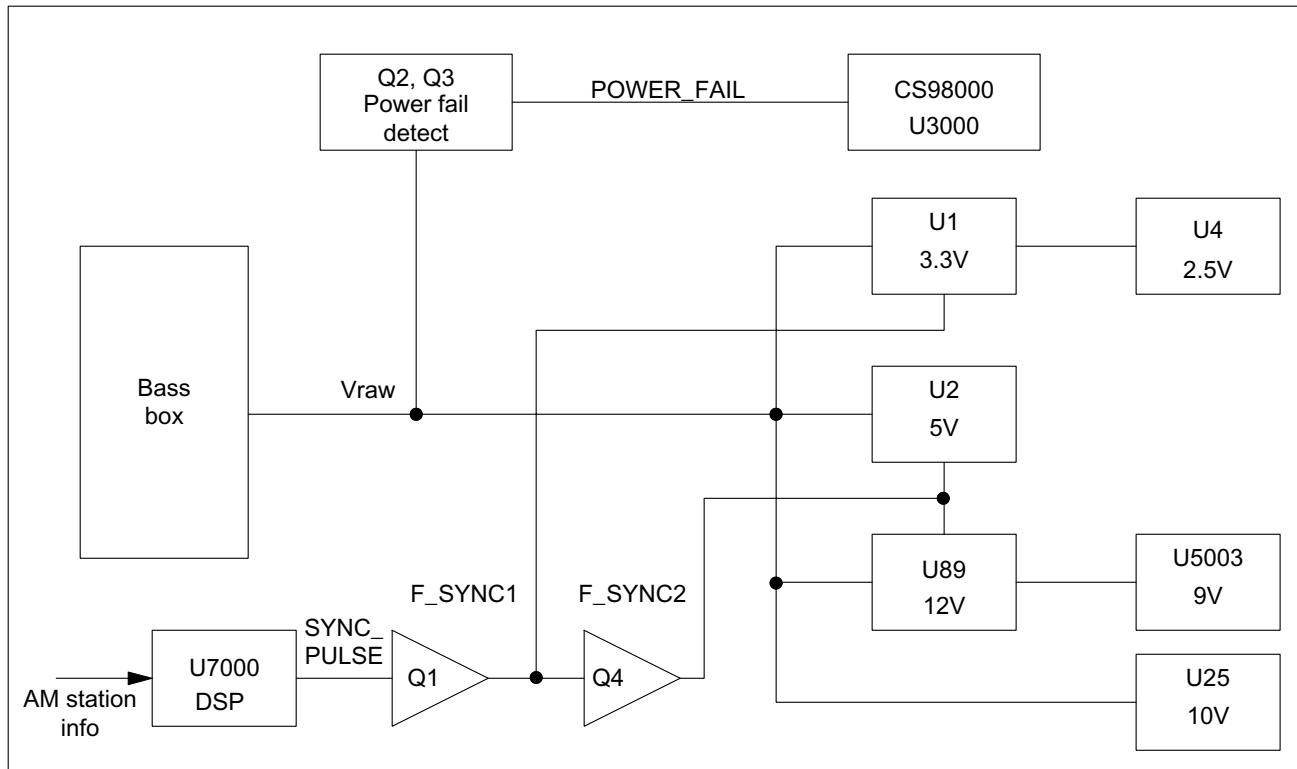

The power supply electronics are comprised of 4 main sections; switching power supplies, linear power supplies, power supply synchronization, and power fail detection. The console's input voltage, V\_RAW comes from the bass module and is nominally +16VDC. This voltage varies with load and line levels, but is limited to +18V maximum (the maximum rated operating voltage of the power amplifier). This voltage is always present whenever the bass module is plugged into the wall and so the console's power supplies are likewise active.

# THEORY OF OPERATION

Voltage on V\_RAW is modulated by the load placed on it and can temporarily dip well below +13V during audio playback at loud volumes. For this reason, the switching power supply labeled 12V is actually supplying 11.5V to maximize headroom and still comply with the DVD player's operating specifications.

The 2.5V linear regulator is connected to the 3.3V line to increase efficiency and, therefore, minimize heat dissipation. The 9V rail is derived from the +12V line for the same reason, as well as to reduce power supply ripple getting through the AV mux to its outputs. The 10V linear regulator is connected to V\_RAW to provide adequate headroom.

**Console Power Supply Architecture**

The power supplied by each rail varies depending on what mode the system is in. A summary of typical power drawn by rail is given below. Also included for reference is the power drawn by the bass box (120V).

| MODE           | RAIL  |       |      |      |      |       |     |      |

|----------------|-------|-------|------|------|------|-------|-----|------|

|                | 120V  | Vraw  | 12V  | 5V   | 3.3V | 10V   | 9V  | 2.5V |

| <b>Standby</b> | 21.8W | 12.5W | 1.3W | 2.3W | 3.2W | .6W * | .7W | 1.2W |

| <b>DVD</b>     | 25.4W | 15.2W | 1.9W | 4.0W | 3.4W | .6W * | .7W | 1.3W |

| <b>CD</b>      | 25.2W | 13.4W | 1.9W | 4.0W | 3.3W | .6W * | .7W | 1.2W |

| <b>FM</b>      | 22.2W | 12.7W | 1.3W | 2.5W | 3.2W | .6W * | .7W | 1.2W |

| <b>AM</b>      | 21.6W | 12.3W | 1.3W | 2.5W | 3.2W | .3W * | .7W | 1.2W |

| <b>AUX</b>     | 22.2W | 12.7W | 1.3W | 2.5W | 3.2W | .6W * | .7W | 1.2W |

\* The power supplied by the 10V rail is dependent on the last mode the tuner was in. Vraw, 120V, and the 10V rail all drop by approximately .3W if the tuner was in AM mode last as opposed to FM.

**Note:** Power supplied by rail (with system muted)

# THEORY OF OPERATION

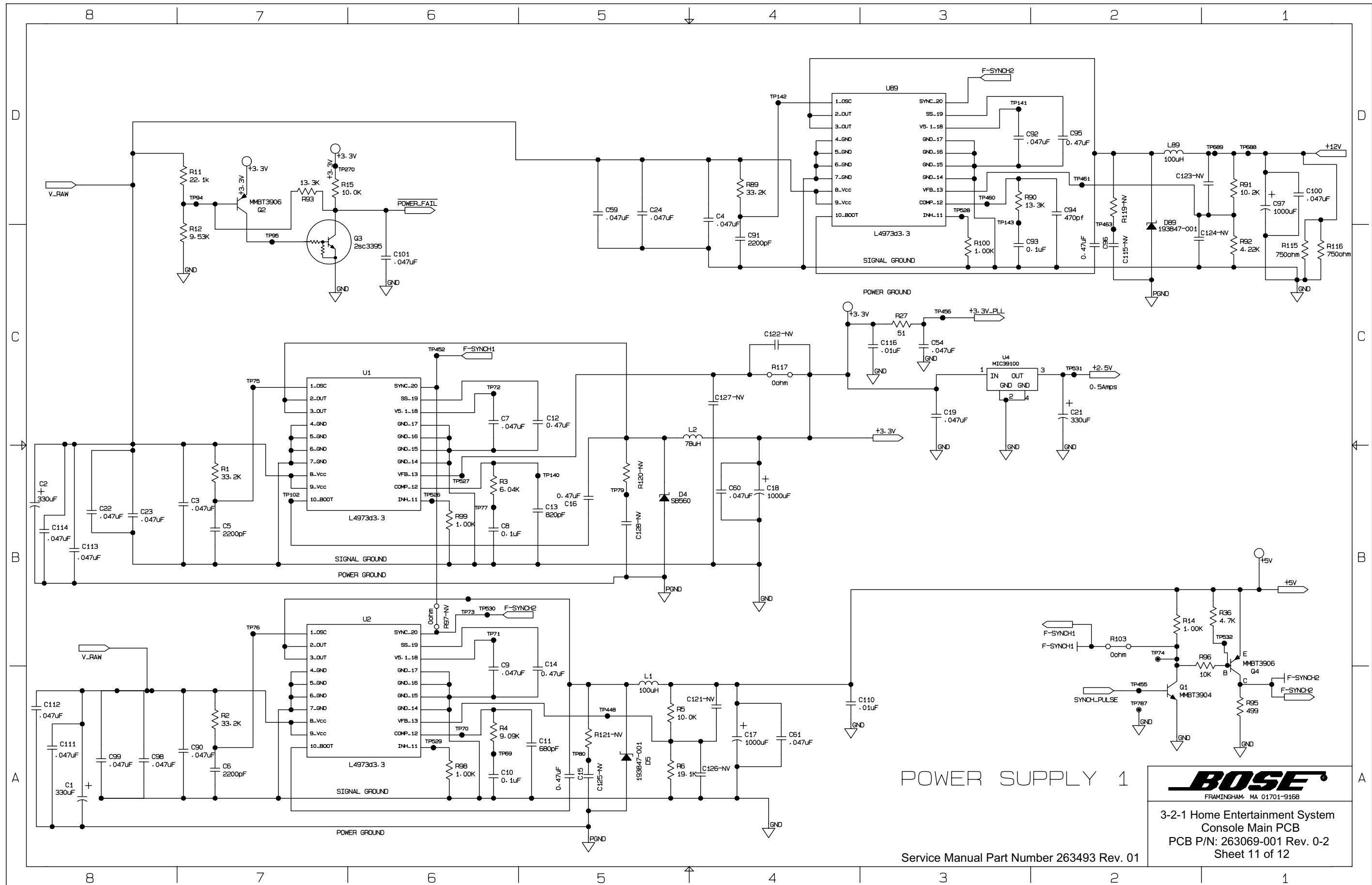

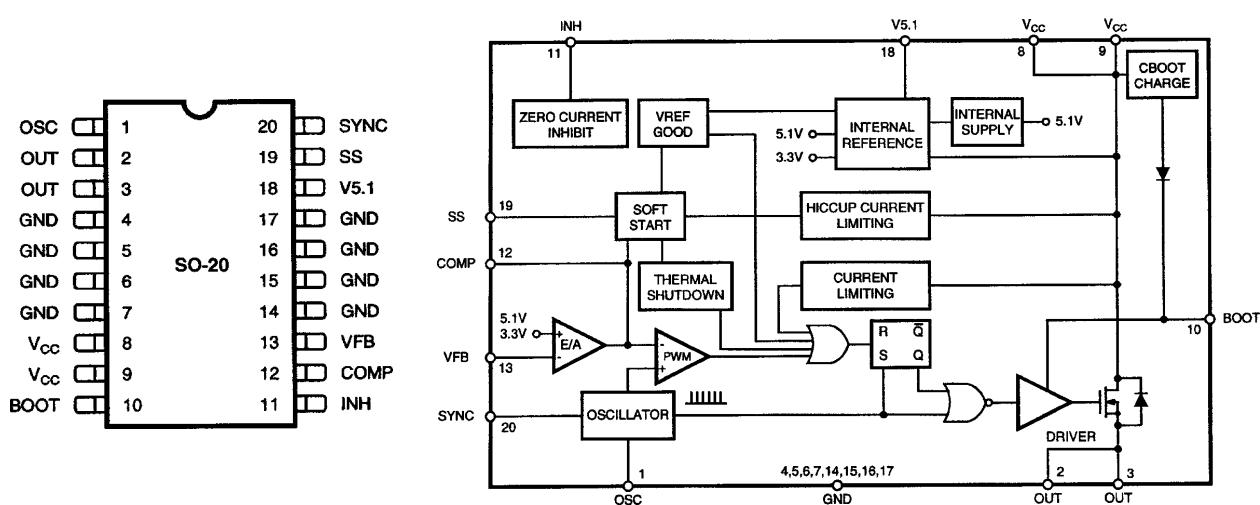

## 2.1. Switching Power Supplies

The switching power supplies use ST L4973D3.3 regulator ICs U1 [sheet 11, C6], U2 [sheet 11, A6], and U89 [sheet 11, D3]. The power supplies are designed as step-down Buck converters. The voltage fed back to the chip on pin 13 determines the output voltage; the chip's control circuitry will work to keep this voltage at +3.3V. The +5.1V and +12V supplies use resistor divide-down networks to obtain the +3.3V feedback voltage.

The reference designators listed below correspond to the +12V regulator on the tuner board; the designs of the +5.1V and +3.3V regulators are nearly identical.

| IC Pin | Components Connected | Function                                                           |

|--------|----------------------|--------------------------------------------------------------------|

| 1      | R89, C91             | Sets switching frequency (when not controlled externally)          |

| 10     | C96                  | Bootstrap to drive internal D-MOS                                  |

| 11     | R100                 | Inhibits supply                                                    |

| 12     | R90, C93, C94        | Lead-lag filter for compensation loop                              |

| 13     | R91, R92             | Voltage feedback for control                                       |

| 18     | C92                  | +5.1V for external reference                                       |

| 19     | C95                  | Sets supply soft-start time constant                               |

| 20     | None                 | Supply frequency switching synchronization (see section 2.3 below) |

A number of additional series inductors and parallel capacitors exist to provide filtering functions.

There are two 750 Ohm resistors (R115 and R116 [sheet11, C1]) tied between +12V and ground to keep the 12V switcher operating correctly under light load conditions. Without these ballast resistors, under light load, there is not enough current flowing to charge the bootstrap capacitor and the D-MOS does not turn on fully.

The compensation networks used for these switching power supplies have been chosen to provide stability under all conditions as well as to provide minimal RF interference to the tuner. The supplies function in both continuous and discontinuous mode depending on the load.

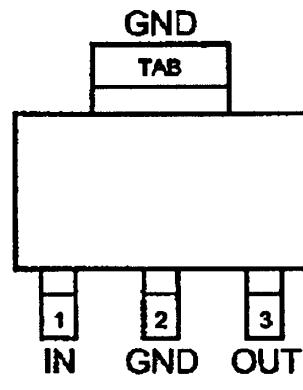

## 2.2. Linear Power Supplies

The linear power supplies are the standard 7800 series TO-220 packages with the exception of the 2.5V linear regulator (U4 [sheet 11, C3]). The 2.5V linear regulator is a low dropout surface mount with adequate topside copper to keep the IC at an acceptable temperature.

## 2.3. Supply Synchronization

In order to minimize input voltage ripple and EMI we have implemented a variable frequency alternate switching synchronization scheme. The DSP outputs a synchronization pulse based on the AM station to which the console is tuned. This 50% duty cycle signal is fed through two transistor stages (Q2 and Q3 [sheet 11, C/D 6/7]) which provide both buffering and inversion. The switching IC's synchronization inputs (pin 20 of U1,U2, and U89) are rising edge-triggered so duty cylce is not as important as switching frequency. When the switcher IC gets a rising edge on its synchronization input, it turns its internal D-MOS switch on. The duration of this on time relative to the switching period, or duty cycle, is directly related to input and output voltage (duty cycle =  $V_{out}/V_{in}$ ). The 3.3V switcher (U1) is fed an inverted synchronization pulse relative to the 12V and 5V switchers (U89 and U2 respectively). This switching scheme serves to flatten out the input current demanded.

# THEORY OF OPERATION

Since a Buck converter demands an input current equal to its output current while the D-MOS switch is on, and the 3.3V switcher outputs, approximately, the current of both the 12V and the 5V switcher, it makes sense to turn the 3.3V switcher on at a different time. By doing this the input current ripple is roughly halved. This switching scheme has the added benefit of improving the input capacitor's lifetime by reducing the self heating caused by ripple.

## 2.4. Power Failure Detection

It is important to detect a power failure and alert the microprocessor to save any relevant information and mute the power amplifiers so that no audio "pops" will be heard. The power failure detection circuit that we employ controls an edge-triggered interrupt to the CS98000 microprocessor (U3000's PIN 185 [sheet 3, C7]) to do just that. If the voltage on V\_RAW falls below roughly 9V, the microprocessor will be alerted that there is a power failure occurring. The interrupt will be unasserted (go high) when V\_RAW goes above 14V. This large hysteresis is set so that dips in V\_RAW caused by loud volumes will not inadvertently trip a power fail interrupt. In a brownout condition, the system will mute with the power dip and then recover gracefully when the normal line level is restored (V\_RAW goes above 14V).

# 3.0 Control Electronics

The majority of the control electronics are located on the Main PCB, the notable exception being the infrared transceiver module and the slave microprocessor located on the display board.

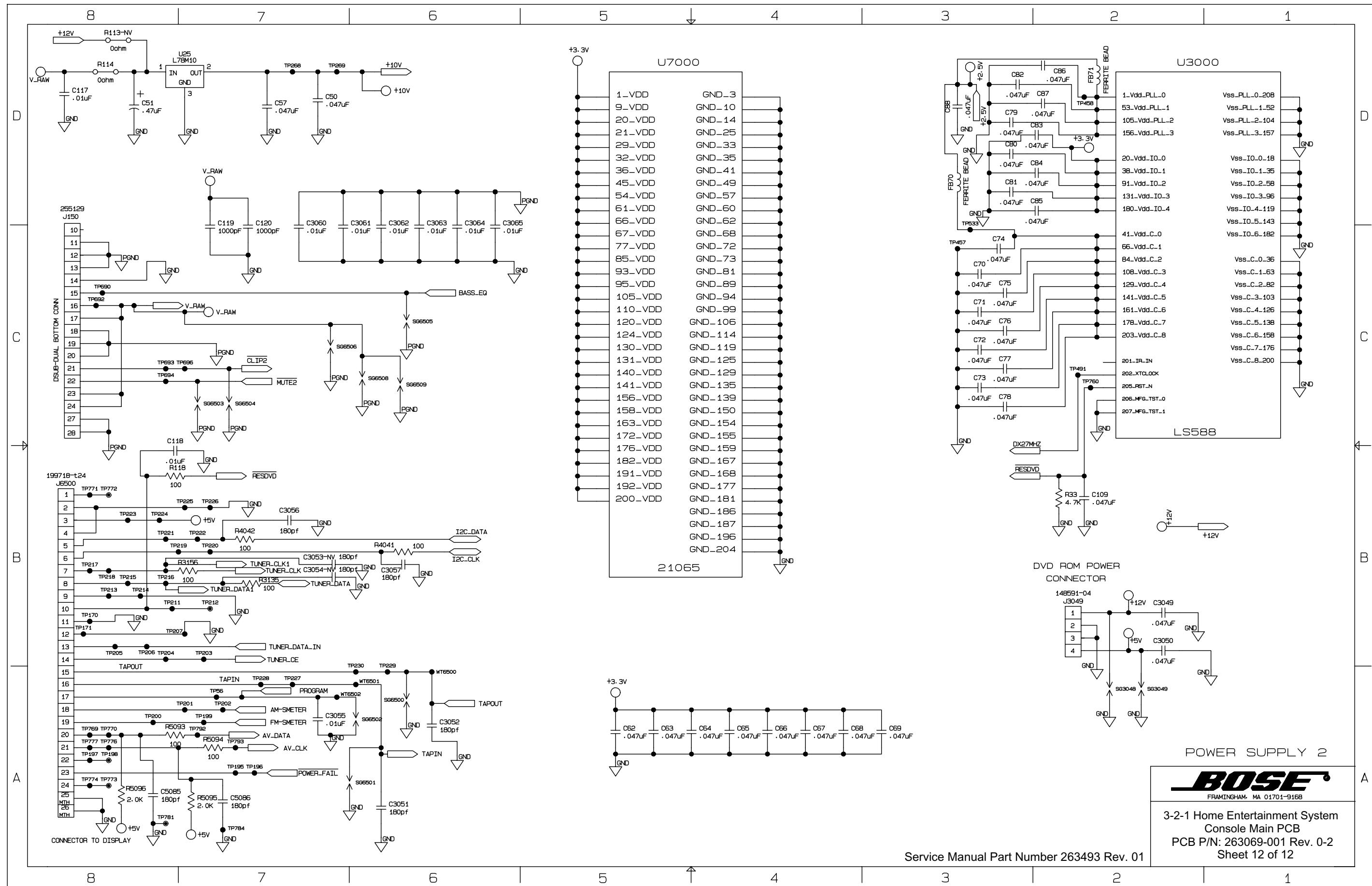

## 3.1 Microprocessor

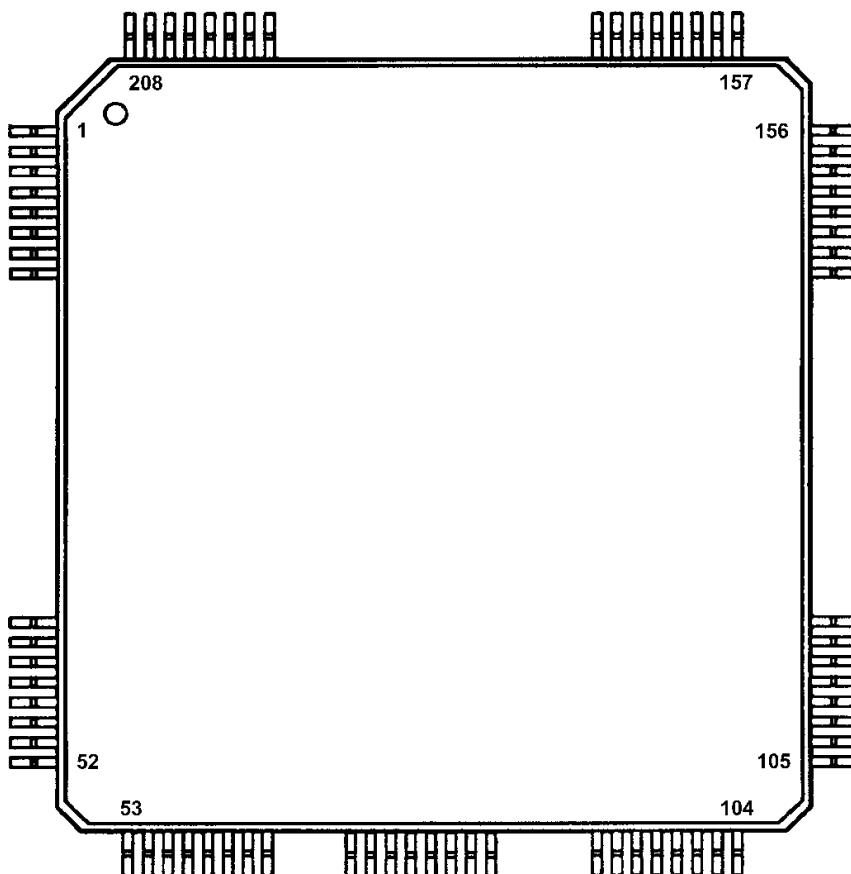

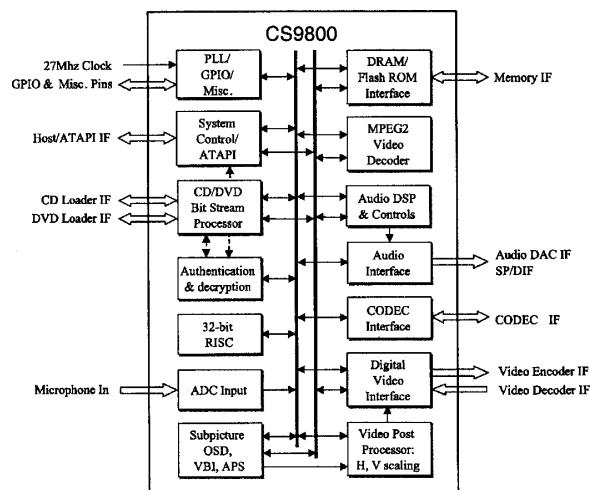

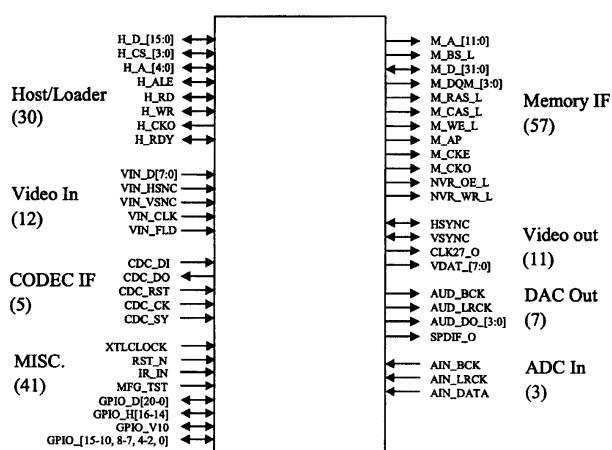

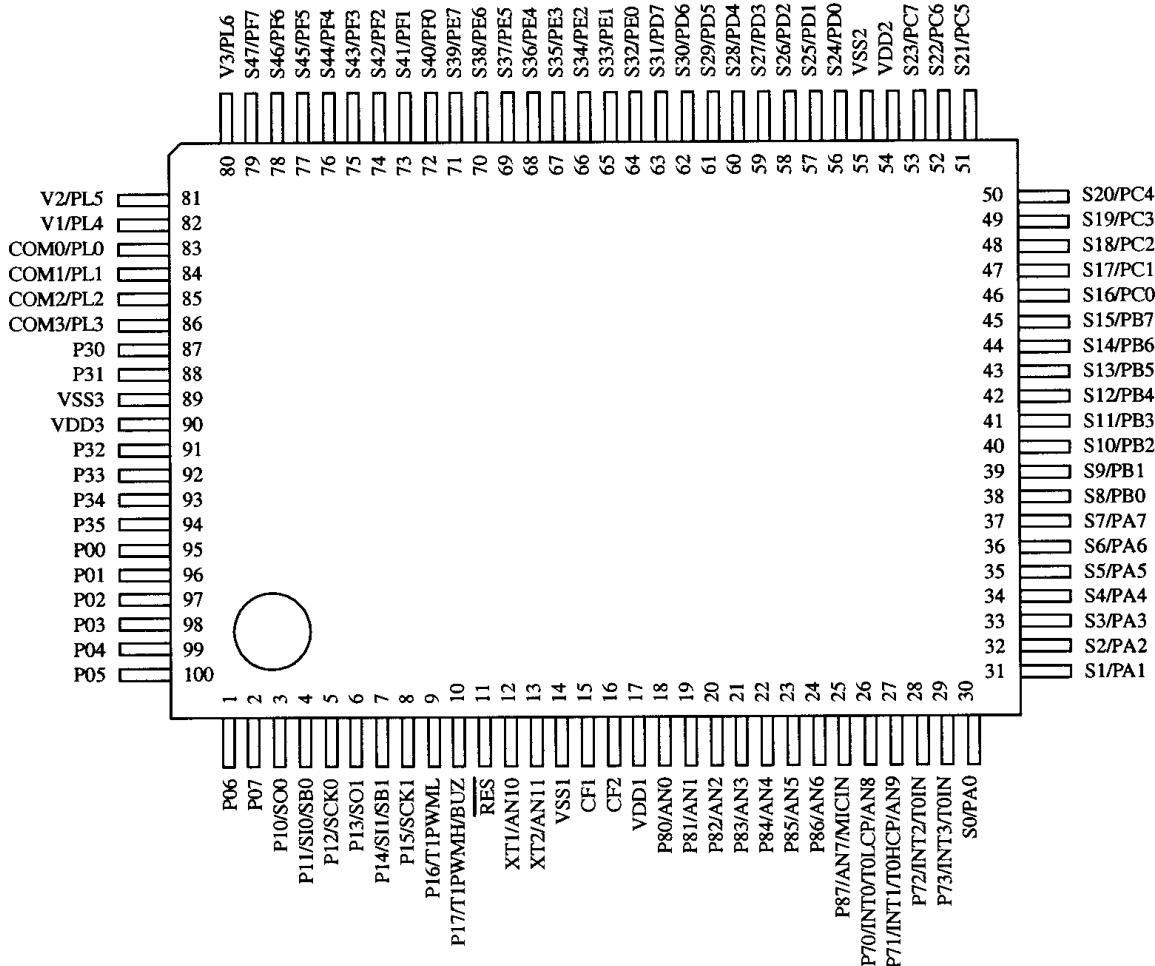

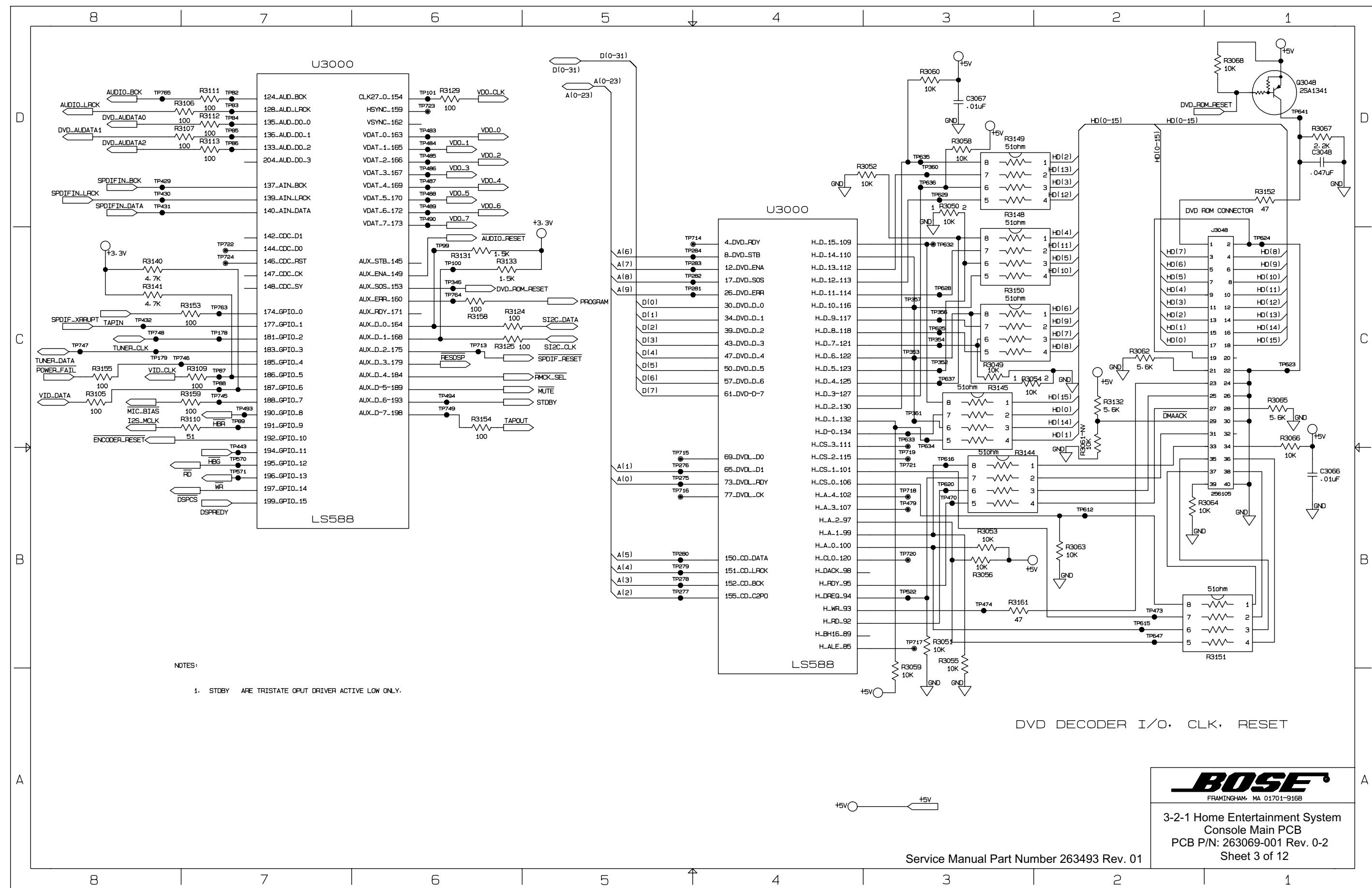

U3000 is a CS98000 DVD decoder IC that also functions as the Media Center's main processor.

U3000 contains two 32-bit RISC processors, a DSP core, a memory interface which supports SDRAM and FLASH ROM, an ATAPI interface, a DMA controller, an MPEG video decoder, a digital video interface, digital audio processing, and a general purpose interface.

The MPEG video decoder in U3000 decodes the MPEG information from the DVD-ROM drive on the ATAPI bus and stores the decoded video into SDRAM for later readout to the video interface. One RISC processor runs the navigator software to access the program material from the DVD/CD or external digital audio source and manages the Video and Audio decoders to present the material. The second RISC processor runs Bose® software that handles system control, the on screen display (OSD) functions, and I/O functions including reading the console buttons, receiving the IR remote control commands, driving the OSD and LCD display on the console. The DSP core in U3000 decodes the digital audio data as required, and sends it out the digital audio interfaces. The ATAPI interface connects to the DVD-ROM drive. U3000 sends standard ATAPI control commands to the drive and receives MPEG-compressed audio, video, and control information from the drives.

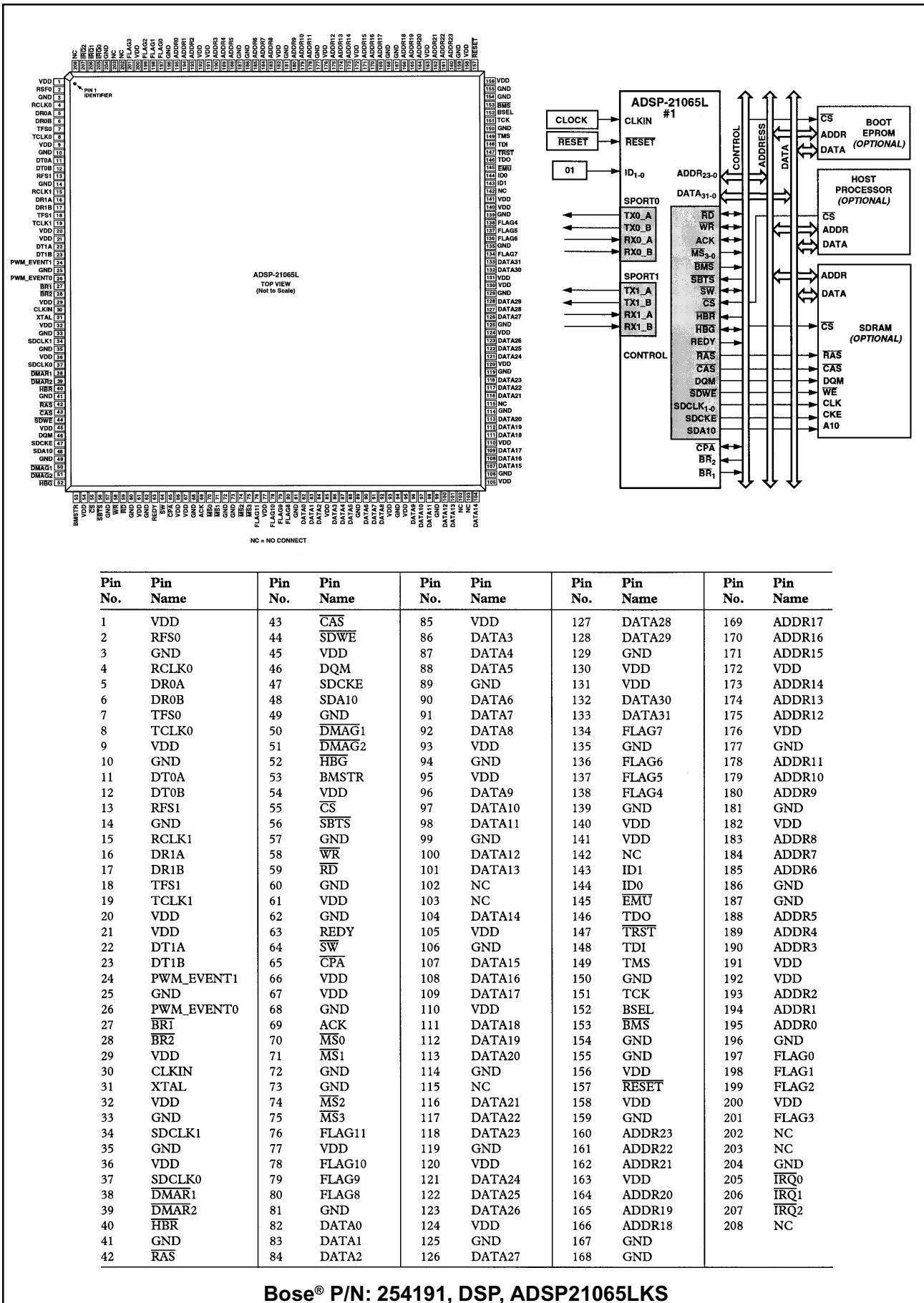

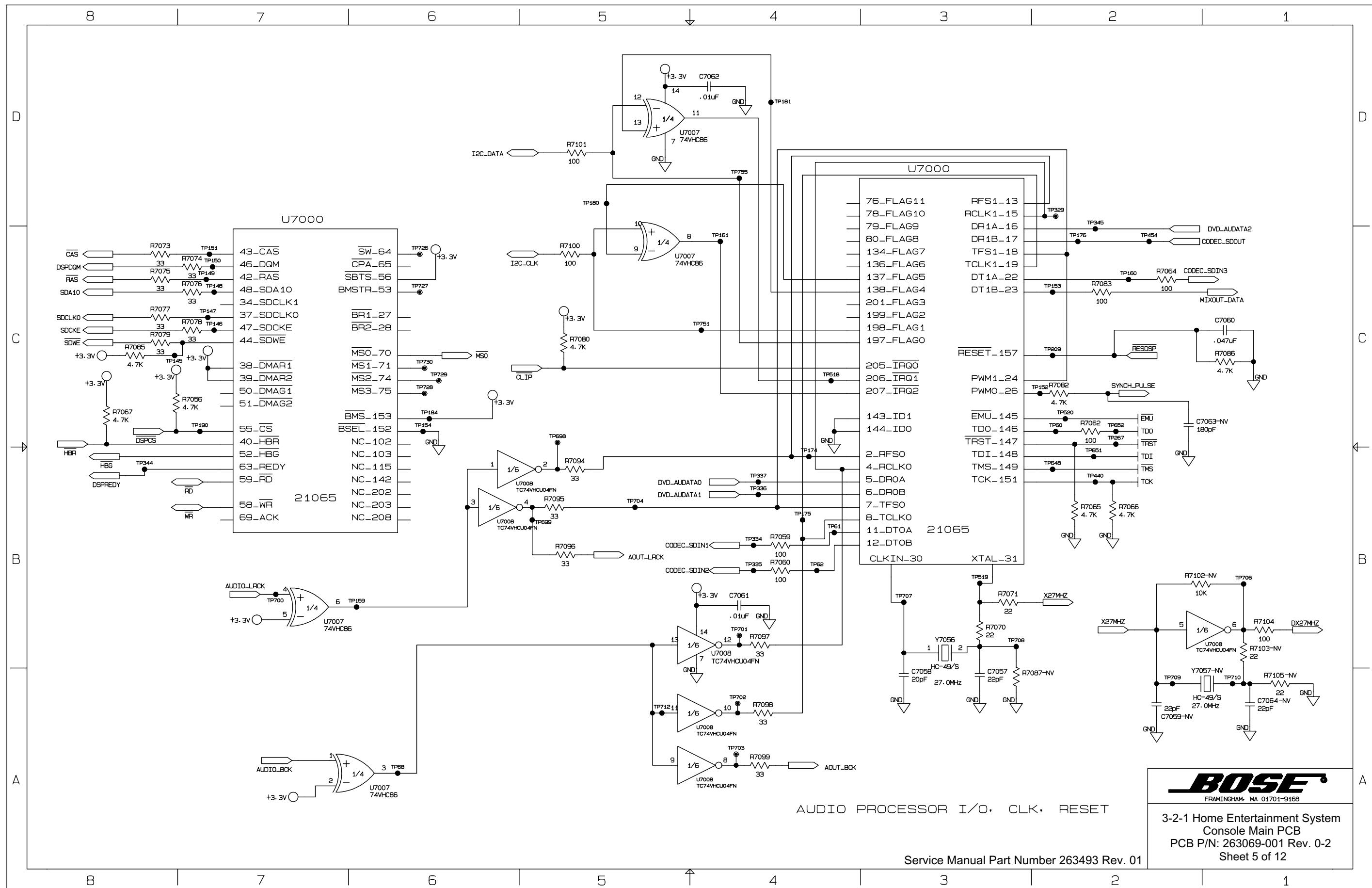

### 3.1.1 Microprocessor clock

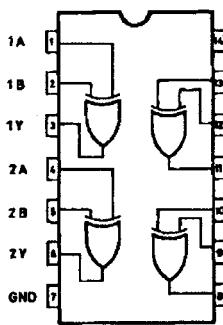

U3000 is clocked by a crystal inverter-oscillator whose nominal frequency is 27.000 MHz. The inverter used is internal to the DSP IC U7000 [sheet 5, C3] and is located between pins 30 and 31. An external bias resistor is not required, as an internal resistor of approximately 1M Ohm is also included internally. The crystal in the inverter's feedback path is designed for a 20pF load, achieved by the series combination of a 20pF and 22pF load capacitors C705 and C7057 and other stray board capacitance and input gate capacitance. R7070 sets the pole in the oscillator's loop response, and a 7404 inverter located in U7008 [sheet 5, B1] buffers the output between the oscillator and U3000.

# THEORY OF OPERATION

After the signal is buffered by U7008, the 27 MHz clock signal (DX27MHZ) enters U3000 at pin 202 [sheet 12, C2]. From there the buffered 27 MHz clock signal exits U3000 at pin 154 [sheet 3, D6] as the signal VDO\_CLK. From there VDO\_CLK is sent to the video DAC U5000 pin 29 [sheet 10, C7] to drive the video circuitry. Frequency accuracy within  $\pm 50\text{ppm}$  of this oscillator circuit is necessary for color video operation.

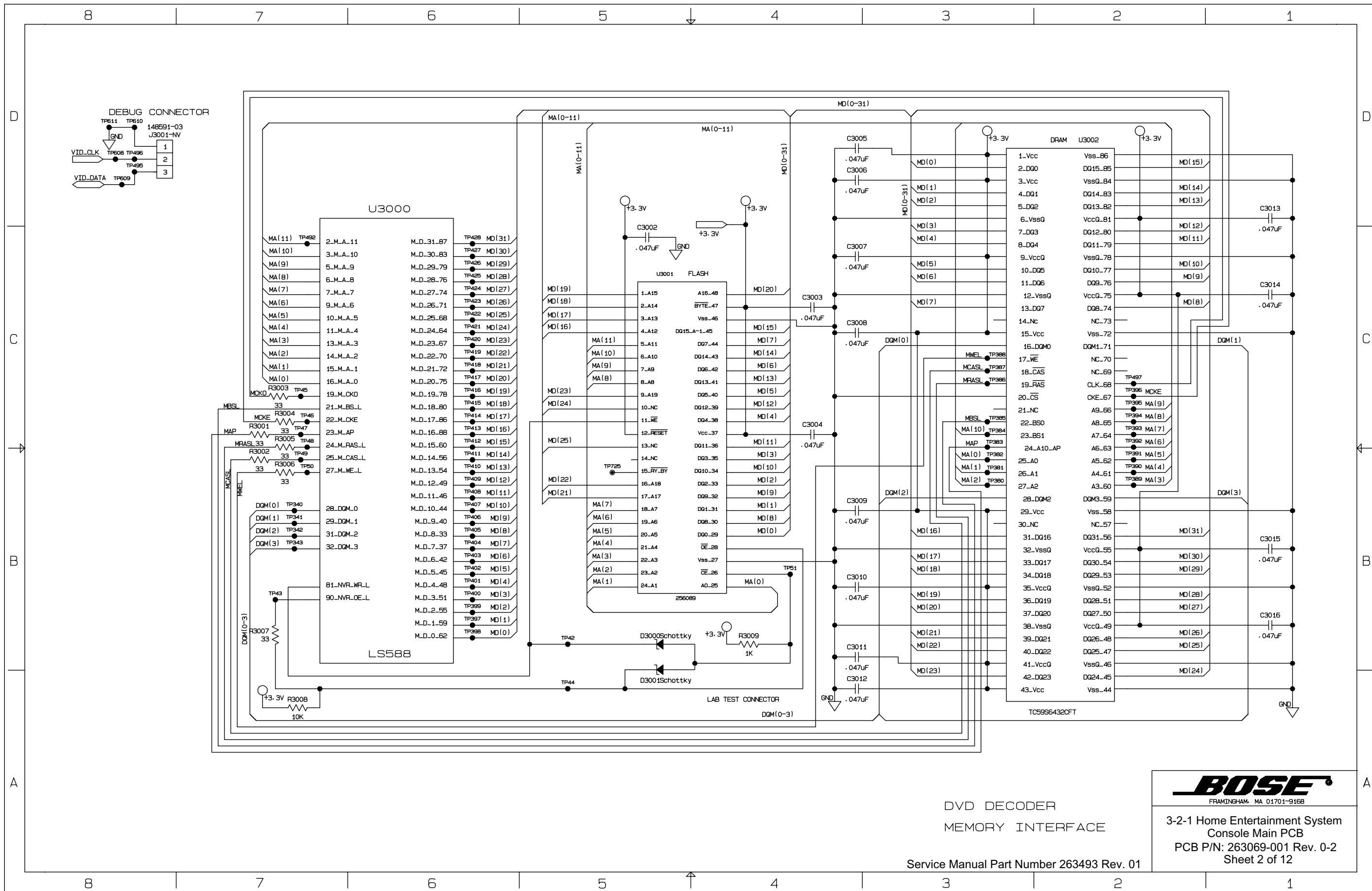

## 3.2 Memory

The U3000 memory interface supports both SDRAM and flash memory of various sizes. Both memory ICs are connected to the same bus, and a chip select chooses between the two devices. The type of memory cycle that is run depends on which address space is needed.

### 3.2.1 SDRAM

U3002 [sheet 2, C2] is a 2-megaword by 32-bit synchronous dynamic random access memory SDRAM IC. For SDRAM accesses, a memory clock of about 80-100 MHz that synchronizes data access is sent to the chip at pin 68. Data commands for accesses are coded in the /RAS and /CAS signals (pins 18 and 19), and data read/write selection is done by the /WE signal (pin 17). The address to be written or read is given on the address bus (pins 25-27 and 60-66). The 32-bit data bus contains the word to be written or read after the pipeline delay of the memory chip.

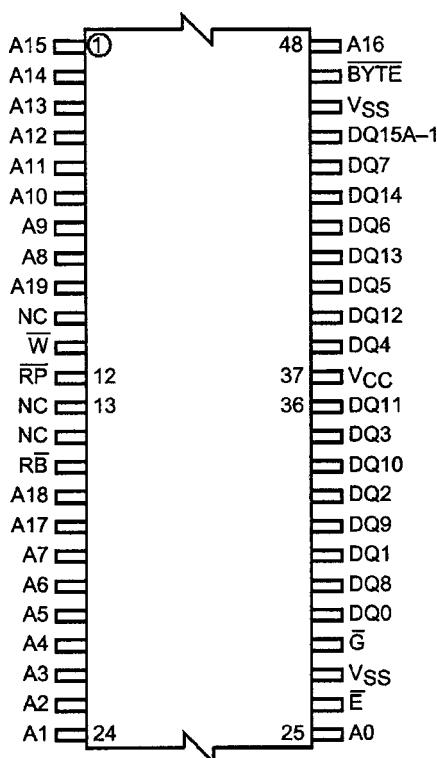

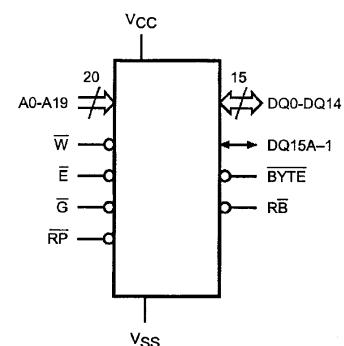

### 3.2.2 FLASH

U3001 [sheet 2, C5] is a 1-megaword by 16-bit Flash memory IC. U3001 shares the memory address and data bus with U3002, but its cycle is different from the SDRAM: flash access is asynchronous and does not use a memory clock. Address (pins 1-9, 18-24, and 48) and chip select (pin 26) is presented to the chip, and data appears 1 access time later on the data bus. The chip select input on pin 26 of U3001 is a wired OR gate that allows output enable or write enable of U3000, causing the chip select to be asserted, or pulled low at pin 2 of U3001. The flash chip only supplies 16-bit data to U3000; the other data bus lines are not driven during flash access.

U3001 can be programmed in-circuit by U3000; this allows software updates in the field via CD-ROM. During re-programming, the operating and new program are held in SDRAM. Power failures during field Flash update could result in the Media Center being made completely inoperable.

## 3.3 Remote Control

### 3.3.1 Display Controller assembly

The Display Controller assembly provides all user interface, power management, and source management functions.

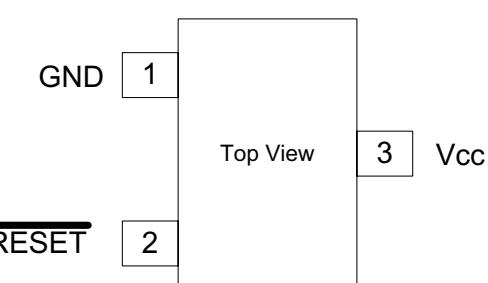

+5 volt voltage monitor. Holds the Display Controller and, indirectly, all other processing circuits in reset unless the +5 volt supply is above minimum threshold and stable.

# THEORY OF OPERATION

## 3.3.2 Display Controller

- Monitors the /POWER\_FAIL input and disables all other functions until false

- Drives the LCD Display

- Controls the Backlight LED

- Receives User commands from the IR detector and 8-button switch matrix

- Receives commands, code downloads from the TAP serial interface

- Serves as Master on both the TUNER I2C, CCB communications buss, and the 3.3v I2C communications buss

## 3.3.3 Communications Busses

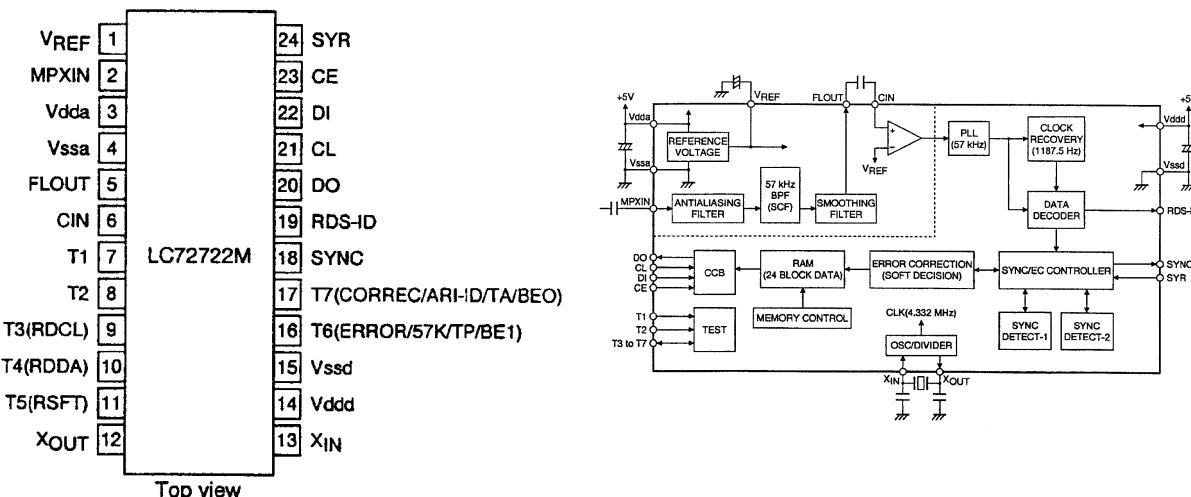

TUNER\_CLK, TUNER\_DATA and TUNER\_DATA\_IN form either an I2C or CCB buss among the display controller U3, DVD controller U3000, tuner PLL IC U2034, RDS decoder U2033 and the serial EEPROM U6000. The display controller U3 is permanent master for either I2C or CCB buss communications. All other devices function as slaves.

The display controller U3 also functions as permanent master controller on the I2C\_DATA, I2C\_CLOCK lines when communicating to the DSP U7000 and the audio codec U4000.

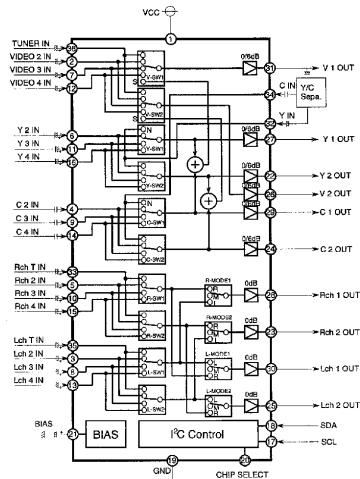

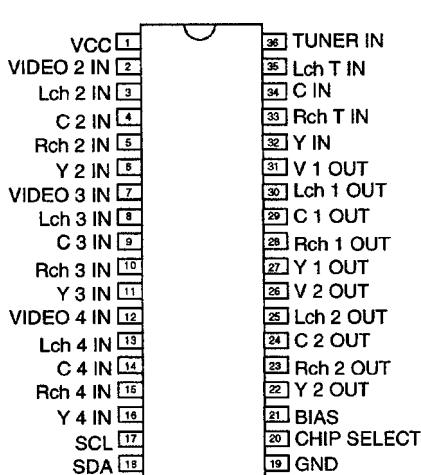

AV\_DATA and AV\_CLK provide a dedicated I2C buss from the display controller U3 to the audio/video MUX U5001.

VID\_DATA and VID\_CLK form a high-speed I2C buss from the DVD controller U3000 to the video encoder U5000.

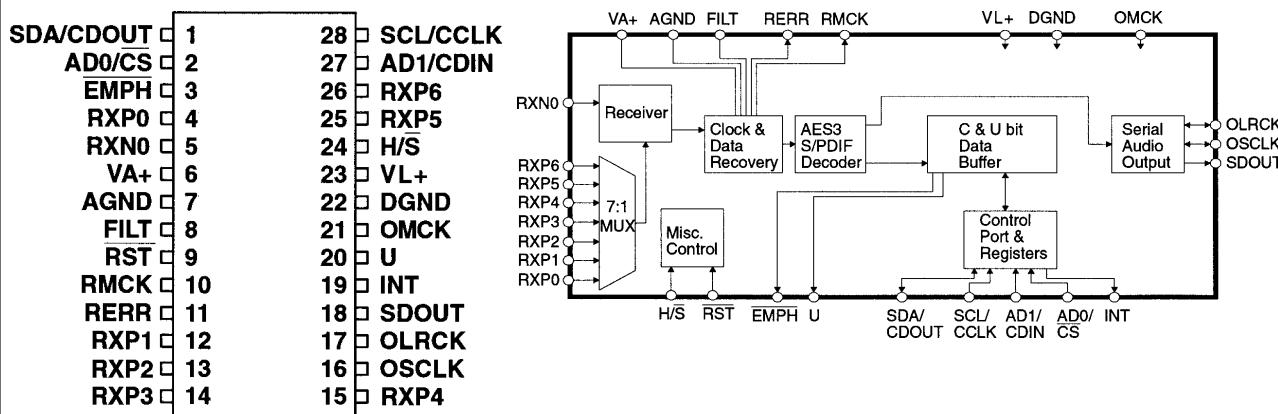

SI2C\_DATA and SI2C\_CLK form another dedicated I2C buss from the DVD controller U3000 to the S/PDIF decoder U4020.

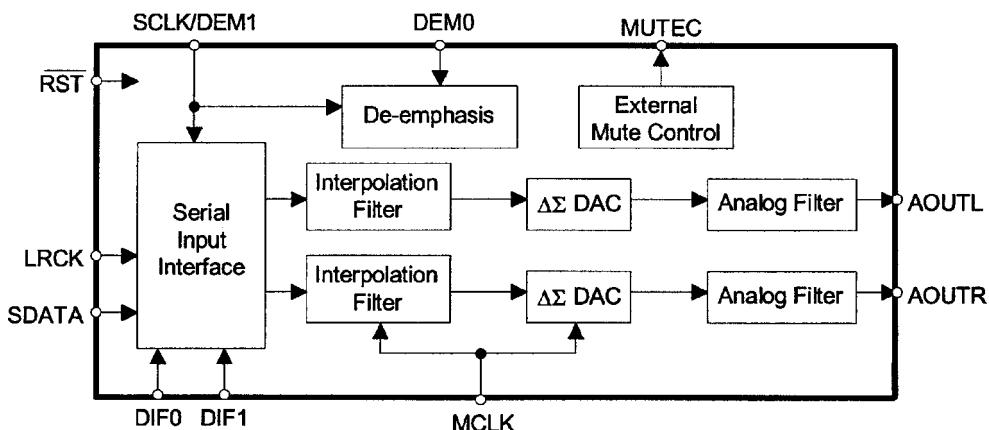

## 4.0 Audio Electronics

There are four sources of audio inputs available to the 3-2-1 console audio path...

- Disc Sources (DVD/CD)

- Internal Analog (Tuner)

- External Analog (Aux In, Video 1, and Video 2)

- External Digital Audio / S/PDIF (Aux D, Video 1 D, Video 2 D, Video 1 Optical)

...as well as two sets of outputs...

- Fixed "line level" outputs (Aux Out)

- Speaker outputs including 4 sets of array outputs on the 9-pin connector and a line level "bass\_eq" signal to the bass box amplifier.

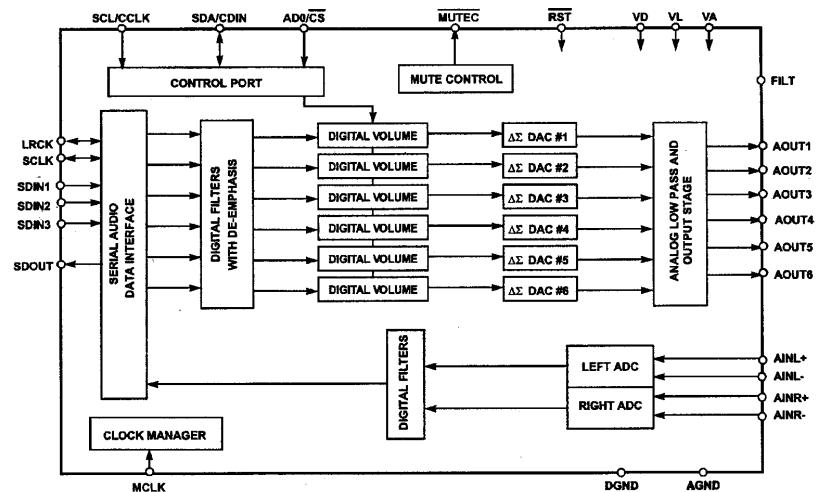

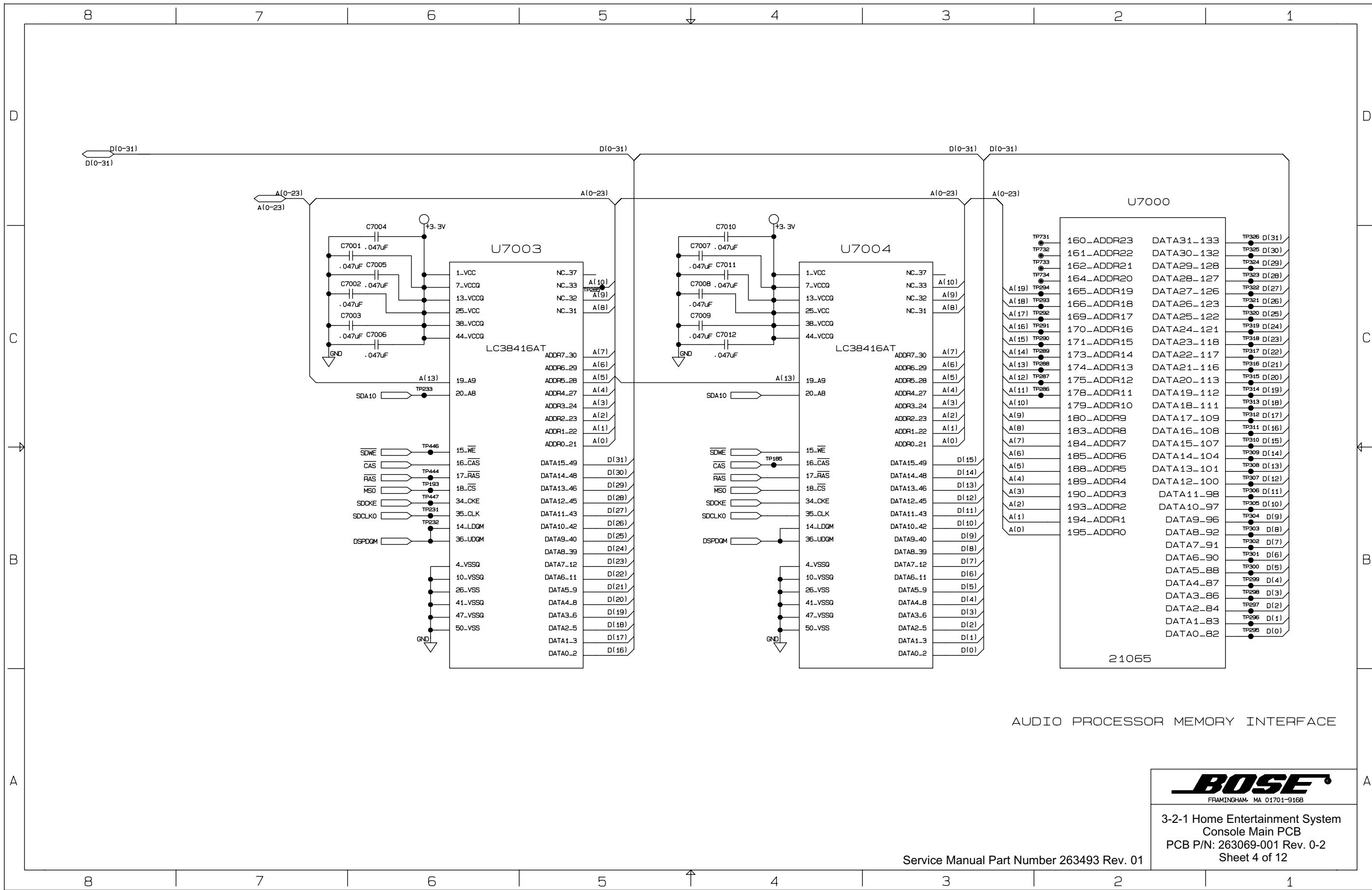

Being a one-zone system, it is only necessary to process one and only one audio input to both sets of outputs. However, the number of channels of input and output usually do not match (i.e. stereo input to 4 channel+bass main output or AC3 surround sound to the 2 channel Aux Output). To marry inputs to outputs, this and other processing (VideoStage®, array processing, compression, volume control, etc.) is accomplished in the digital domain by the Audio Processor DSP (SHARC AD21065, U7000). The audio path design is therefore centered on this IC, meaning all audio signals must ultimately pass through the DSP IC. The overall intent of the IC's of the audio path is fulfill these requirements.

# THEORY OF OPERATION

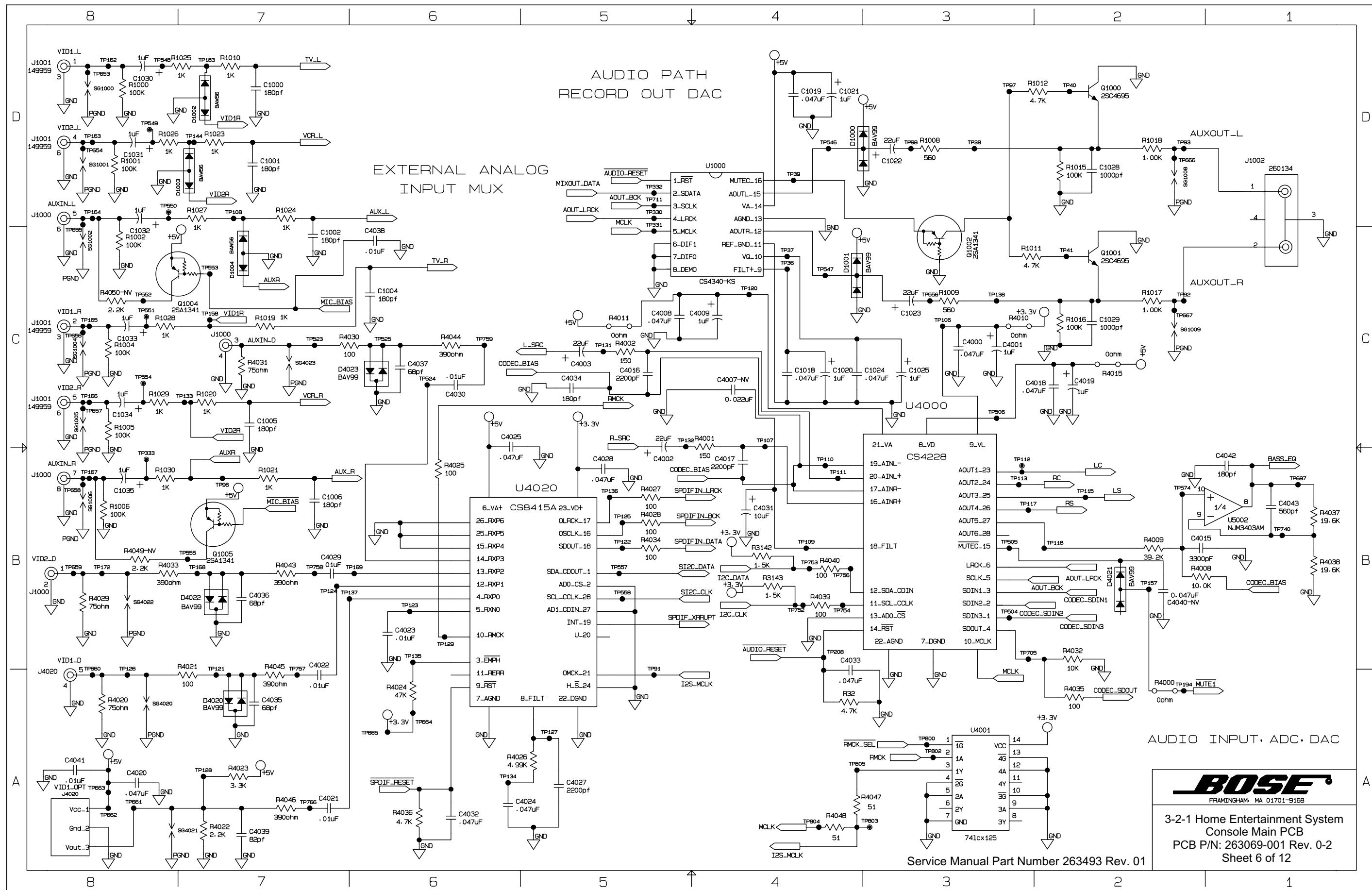

## 4.1 Input Audio Path

For analog audio input sources (Aux In, Video 1, Video 2, and Tuner) these L and R signals are selected by the Mitsubishi A/V Mux (M52790, U5001 [sheet 10, B4]), passed through attenuation (about  $-1.5$  dB) buffers (U5002) to the A/D portion of the CS4228 Surround sound “Codec” (U4000). These inputs are full 2Vrms line level capable where the small attenuation is necessary as distortion may occur in driving the A/D inputs single-ended with a full 2V input. These signals are converted to I2S digital audio format and sent to a dedicated input serial port (CODEC\_SDOUT) of the DSP IC U7000.

Internal Disc audio source data (DVD or CD) are fed to the CS98000 DVD Decoder IC U3000 via the ATAPI interface. External digital audio is also sent to the CS98000 DVD Decoder IC via I2S (SPDIF\_LRCK, SPDIF\_BCK and SPDIF\_DATA) from the S/PDIF receiver/mux (CS8415A, U4020). The CS98000 then can decode the desired input stream if it happens to be in a compressed audio format (AC-3, MP3, DTS, etc.). When an external source is selected with digital (S/PDIF) information available, the CS98000 queries the S/PDIF decoder IC (CS8415A) via I<sup>2</sup>C communication to determine if the receiver has locked to the appropriate input. When it has done so, the DVD\_AUDATA(0:2) path is muted while the CS8415A is reconfigured to output RMCK (see I2S communication section). The CS98000 reconfigures its master clock output to an input. It will decimate the input or decoded audio stream appropriately. After the CS8415A is properly configured for the stream rate the DVD\_AUDATA(0:2) path is un-muted.

After any decompression, the data is then presented to the DSP’s three other available input serial ports (DVD\_AUDATA0,1,2, AUDIO\_LRCK, AUDIO\_BCK) in I2S format. The data present on each of these channels is dependent on the type of audio being decoded.

| Format | Meaning                   | DVD_AUDATA 0 | DVD_AUDATA 1 | DVD_AUDATA 2 |

|--------|---------------------------|--------------|--------------|--------------|

| ACMOD0 | Dual mono                 | Mono/Mono    | None         | None         |

| ACMOD1 | 1/0 : C                   | None         | None         | C/None       |

| ACMOD2 | 2/0 : L, R                | L/R          | None         | None         |

| ACMOD3 | 3/0 : L, C, R             | L/R          | None         | C/None       |

| ACMOD4 | 2/1 : L, R, Sur           | L/R          | Sur/None     | None         |

| ACMOD5 | 3/1 : L, C, R, Sur        | L/R          | Sur/None     | C/None       |

| ACMOD6 | 2/2 : L, R, Ls, Rs        | L/R          | Ls/Rs        | None         |

| ACMOD7 | 3/2: L, C, R, Ls, Rs, LFE | L/R          | Ls/Rs        | C/LFE        |

| PCM    | Stereo/matrix encoded L,R | L/R          | None         | None         |

**Note:** data is LRCK L/H

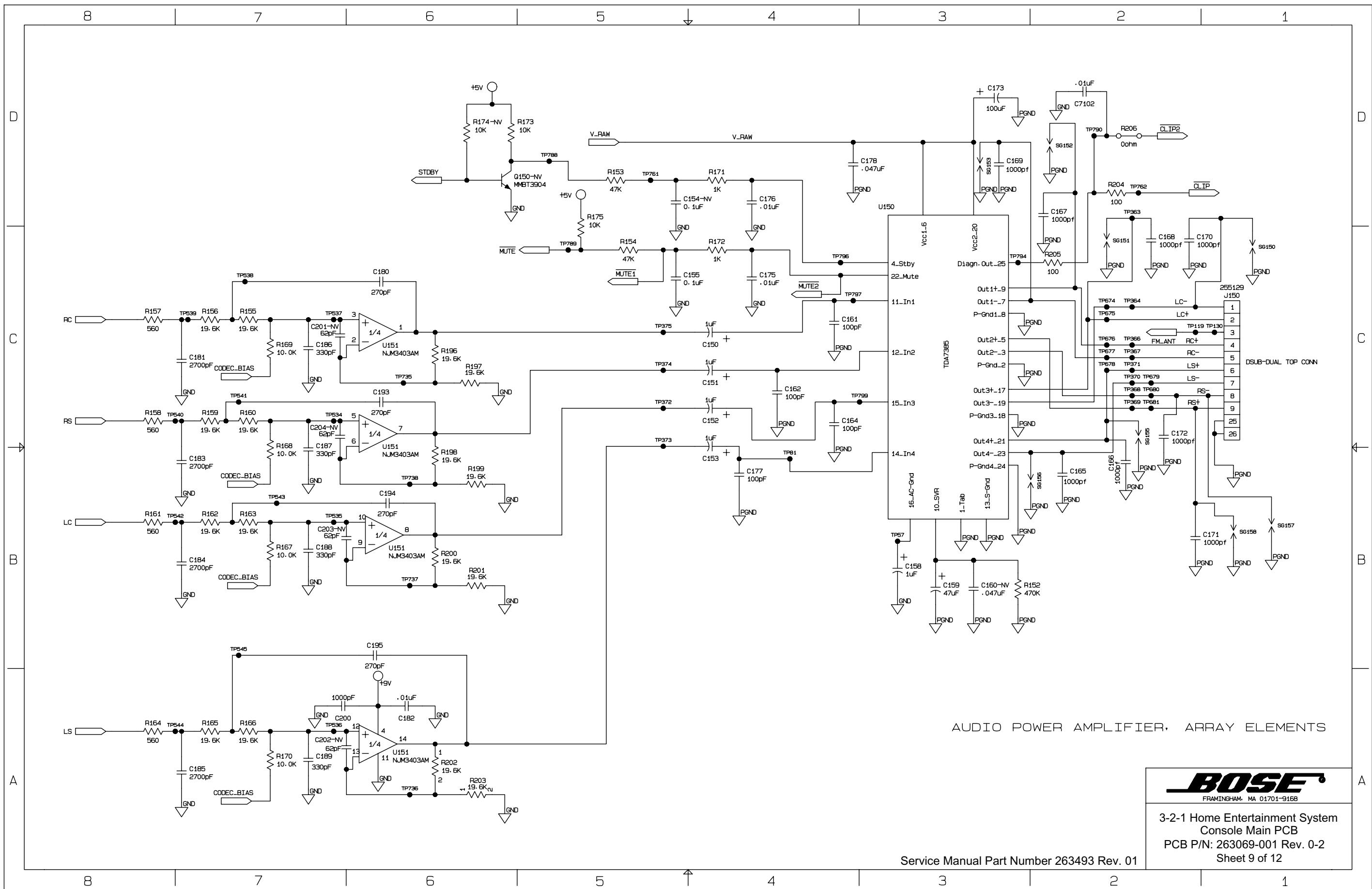

## 4.2 Output Audio Path

For the Aux Out output, the CS4340 stereo DAC U1000 [sheet 6, C4] takes MIXOUT\_DATA and generates the L and R output to a full scale value of about 1.25 Vrms at an output impedance of 1.56K Ohms. The large value for this output R is for ESD protection and EMI reasons. Note there is no volume control for this output. Components tied on the output (Q1000, Q1001, etc.) are used in muting the output when audio data isn’t there or errors are present in I<sup>2</sup>S communications.

# THEORY OF OPERATION

For speaker outputs the CS4228 U4000 [sheet 6, B3] is used again with its 6 D/A converters (5 are used) taking CODEC\_SDIN1:3 and generating the following output signals:

| Input signal | During “Left” LR clock (low) | During “Right” LR clock (high) |

|--------------|------------------------------|--------------------------------|

| CODEC_SDIN1  | LC (Left Center) – pin 23    | RC (Right Center) – pin 24     |

| CODEC_SDIN2  | LS (Left Surround) – pin 25  | RS (Right Surround) – pin 26   |

| CODEC_SDIN3  | Bass – pin 27                | None                           |

The CS4228 produces a substantial amount of out-of-audio-band (beyond 20kHz) noise (about 50mVrms) due the nature of the sigma-delta conversion DACs and lack of much filtering on the IC itself. This amount of noise was seen as serious enough to implement filtering on the outputs of the DACs before amplification. Without filtering, there would be a substantial amount of power dissipation in the amplifier stage as well.

The DAC outputs are biased to 2.3V and have a full scale output of 1.3Vrms. For the array outputs, these signals are sent through 3 orders low-pass filtering. These circuits comprise of a passive RC filter (i.e. R157, C181) and the Sallen-and-Key type 2<sup>nd</sup> order filters centered around U151 and related components. These together give a cutoff frequency of around 40kHz. These filters also attenuate the audio signals by (-)8dB before being AC coupled to the output amplifier. Thus the total gain after D-to-A conversion is 18dB (or about x8) which at full scale output can drive the speakers to 10.4Vrms. Note that for proper biasing of the op-amps a reference voltage (CODEC\_BIAS) is generated (2.3V) for the inputs with one of the op-amps in U5002. The voltage gain on the output of the filter is again mainly for DC biasing and sets it to nominally 4.6V. Also note that the input bias for the amplifier IC is set to half V<sub>raw</sub> or around 8V with no load. A similar gain structure is used for the bass output but a less complicated filter (single-pole) with a cutoff frequency of 6kHz is used to drive the BASS\_EQ output to the bass box.

The /MUTE signal controls both array and bass amplifier (on /MUTE2) inputs on any normal muting condition by Pulse Width Modulating the signal to get a longer time constant that would normally be achievable with the given components. Note the muting time constant of the bass amplifier is much longer than the array amplifier, meaning that sometimes with high bass content material, the bass can be heard for a little time after the arrays have muted. /MUTE1 bypasses the normal time constant and is used as an emergency mute from the CODEC IC in case there are errors in the digital data that might cause snaps or other harsh noises to be sent to the speakers.

## 4.3 Digital Audio Communication (I<sup>2</sup>S)

Digital audio data is transferred into and out of the DSP IC via 4 input and 4 output serial interfaces. The digital communication on the 3-2-1 is accomplished using the I<sup>2</sup>S protocol. All IC's that uses digital audio have the capability in either firmware or software to communicate with I<sup>2</sup>S. In I<sup>2</sup>S format each data line carries two “channels” of data, a “left” signal and a “right” signal. (see the input and output paths for what data signals are actually on each I<sup>2</sup>S line). I<sup>2</sup>S also uses an involved clocking scheme to keep everything straight.

**L/R CLOCK:** The sample clock (otherwise called the L/R clock) defines the sample rate (e.g. 44.1kHz) as well as which of the two channels is “active” depending on the level of the signal. The sample rate for AUDIO\_LRCK is determined by the input source and can be set to 32kHz, 44.1kHz, or 48kHz. The sample rate for SPDIF\_LRCK is determined by the external digital input stream.

# THEORY OF OPERATION

**BIT CLOCK:** There is also a bit clock that synchronizes each bit of each sample. The 3-2-1 console uses 16 bit audio. The frequency of AUDIO\_BCK is 32x the sample frequency (16 bits x 2 samples) whereas SPDIF\_BCK is set for 64x the sample rate. The difference here is due to the constraints of the two IC's driving the signals. The CS98000 can handle the fact that its input bit clock 64x while it is receiving data from the S/PDIF receiver while continuing to drive its output (AUDIO\_BCK) at 32x.

**MASTER CLOCK:** Finally, a “master clock” is necessary to drive the sigma-delta data converters (both A/D and D/A) in the system at integral rate greater than the bit clock. This clock is also necessary to drive the CS98000 input port when the S/PDIF receiver is active. I2S\_MCLK is set for 256x the sample rate.

**Special note on clocking:** If the S/PDIF decoder is recovering a sample rate greater than 50 kHz, the CS98000 must configure it to output RMCK at 128 times the recovered data sample rate. This will permit the AUDIO\_BCK, AUDIO\_LRCK to run at  $\frac{1}{2}$  the S/PDIF sample rate. The CS98000 will decimate a high input sample stream to the  $\frac{1}{2}$  speed output sample rate.

**DATA:** The actual audio data is timed with the bit clock. The data to the 4228 and 4340 is currently being clocked in a nonideal fashion. The DSP's output serial ports must be configured to change data on a rising edge of the AUDIO\_BCK whereas the 4228 and 4340 are reading the data on this edge. This means there is very little (<10ns) hold time for the data. There seems to have been no problems with this to date.

The following table is a summary of the various I2S clock and data signals...

| I2S Signal    | Output From               | Input To                               | Frequency        |

|---------------|---------------------------|----------------------------------------|------------------|

| AUDIO_LRCK    | 98000                     | DSP, 4228, 4340 <sup>*</sup>           | Sample rate (Fs) |

| AUDIO_BCK     | 98000                     | DSP, 4228, 4340 <sup>*</sup>           | 32xFs            |

| I2S_MCLK      | 98000, 8415 <sup>**</sup> | 4228, 4340 (MCLK), 98000 <sup>**</sup> | 256xFs           |

| SPDIF_LRCK    | 8415                      | 98000                                  | Fs               |

| SPDIF_BCK     | 8415                      | 98000                                  | 64xFs            |

| SPDIF_DATA    | 8415                      | 98000                                  | (data rate)      |

| DVD_AUDATA0:2 | 98000                     | DSP                                    | (data rate)      |

| CODEC_SDIN1:3 | DSP                       | 4228                                   | (data rate)      |

| CODEC_SDOOUT  | 4228                      | DSP                                    | (data rate)      |

| MIXOUT_DATA   | DSP                       | 4340                                   | (data rate)      |

**Note:** These signals are buffered to maintain signal integrity to the DSP. AOUT\_BCK and AOUT\_LRCK are the actual signals to the 4228 and 4340.

<sup>\*</sup>Which MCLK signal to use is selected by the RMCK\_SEL line that controls the 74125 tri-state output buffer (U4001). When the 98K is the master, it drives the “output” line (MCLK) directly. When the 8415 is the master, the input of U4001 is selected (RMCK) and the 98K line is changed to an input.

# THEORY OF OPERATION

## 4.4 IC Configuration

The following settings are required to set the audio/communication paths properly specifically for the 3-2-1.

### CS8415 (S/PDIF Receiver)

- Register 0x01 – 0x80 – I2S\_MCLK is switched through to RMCK when lock is lost, Interrupt is active high.

- Register 0x02 – 0x00 – RMCK rate at 256xFs

- Register 0x06 – 0x2? – SPDIF\_BCK set for 64xFs, 16-bit resolution

### CS4228 (Surround CODEC)

- Register 0x01 – 0x04(Default) – MCLK rate to 256xFs, base rate mode

- Register 0x0D – 0x04 – Serial port set to I2S, BCK rate set for 32xFs

- SDOUT (pin 4) – pulled low so that a rising edge of RST the serial registers are set for I<sup>2</sup>C.

### CS4340 (Stereo DAC)

- DIF1 and DIF0 – pulled low – sets for I2S data

- DEM1 and DEM0 – pulled low – disables emphasis (performed in the DSP)

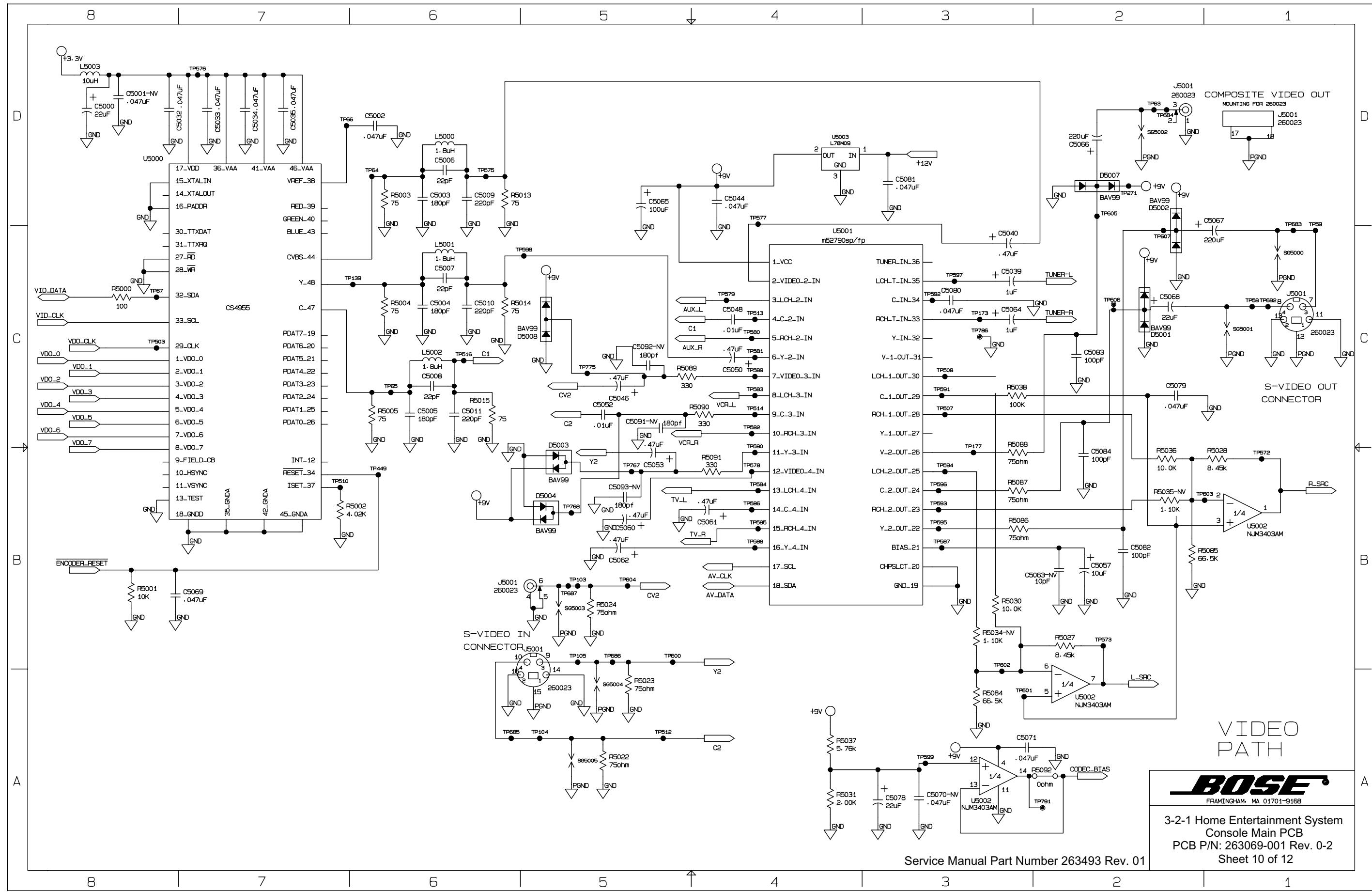

## 5.0 Video Electronics

Video signals may be generated internally or passed-through from a set of external (VIDEO INPUT) connectors. Internally-generated signals include DVD playback and On Screen Display (OSD) signals. OSD menus are accessed by pressing the SETTINGS button on the remote. When not playing back a DVD or generating an OSD, the Media Center defaults to passing-through external video signals. The Media Center provides both Composite and S-Video outputs for both internal and external video paths.

The video interface drives several kinds of video digital to analog converters to generate the analog video monitor drive signals. U3000 (CS98000) generates a standard ITU R.BT656 digital video data stream with embedded synchronization shown as signals VDO1:8 and VDO\_CLK. This standard uses an 8 bit bus, with interleaved Y, Cr, Cb data. Synchronization information is embedded in the data stream, and exclusively uses values of 00 and FF (hex). Y values are from 1 to 254, with 1 being black. C values are from 1 to 254, with 128 being no chroma.

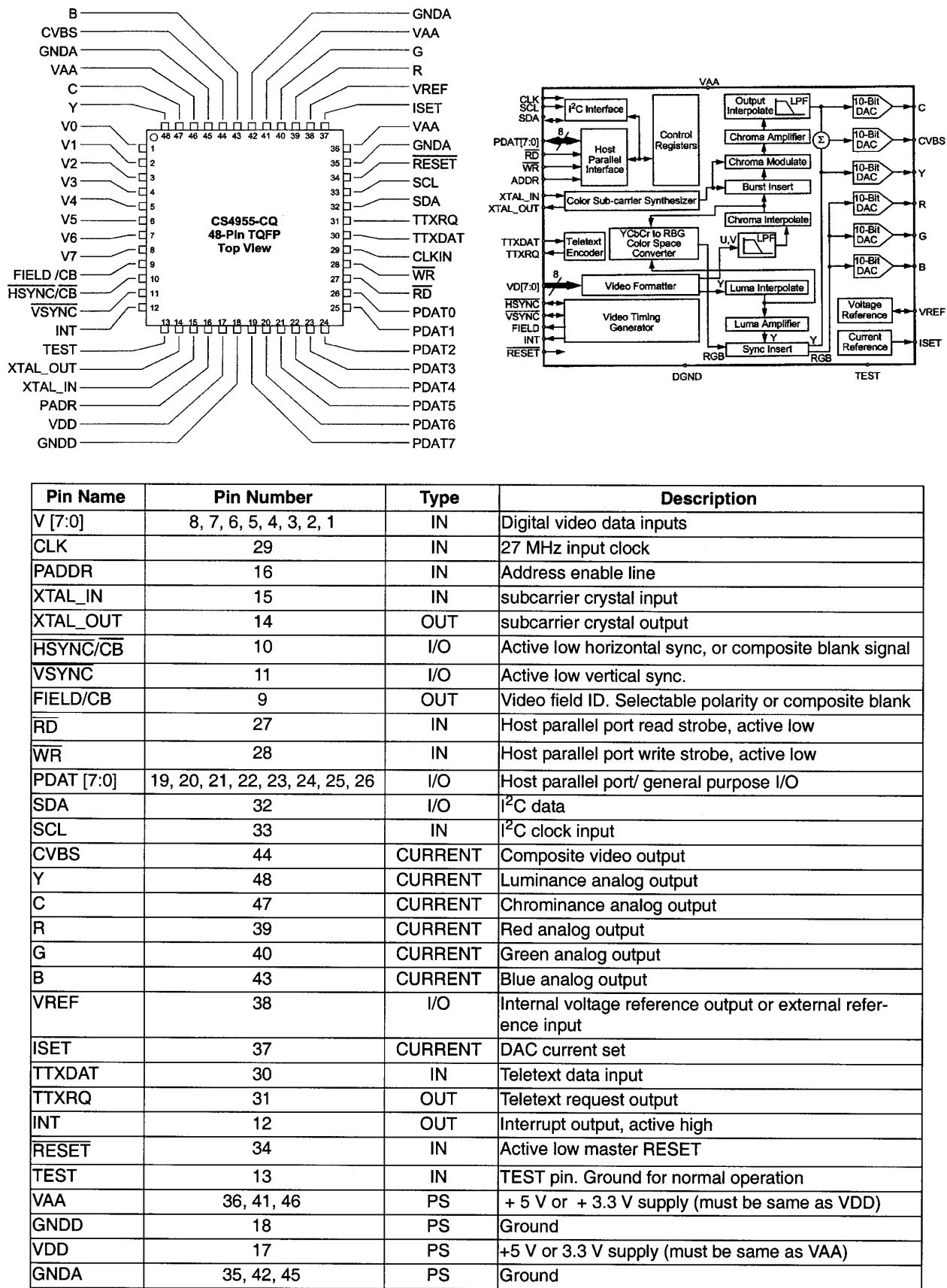

The video digital-to-analog converter, U5000 [sheet 10, C7], is a 44 pin quad flat pack, containing extensive video processing circuitry. This IC has the capability of generating Composite, S-Video, and Component outputs, which satisfy the requirement to provide the signals necessary for internal video. The data sheet for this part (number CS4955) shows the block diagram and signal processing circuitry inside the chip. The chip has many programmable registers inside, to set different operation modes, etc. These registers are set by the main processor over a serial I<sup>2</sup>C bus (VID\_DATA and VID\_CLK, pins 32 and 33).

The CS4955 receives the ITU R.BT656 data bus, decodes the synchronization and separates the Y, Cr, and Cb values into separate data streams. The three channels of video data are processed appropriately, including Macrovision generation, and sent to digital-to-analog converters. Composite video is generated at pin 44, S-video Y and C are generated at pins 48 and 47, and RGB or YCrCb (component video) are generated at pins 39, 40, and 43 but are not used.

# THEORY OF OPERATION

The CS4955 must receive a 27 MHz signal from the clock oscillator, with an accuracy of +/- 1350 Hz. This frequency is phase lock-looped inside the CS4955 to generate the 3.579545 MHz color subcarrier for the composite video signal, and must be of high accuracy so that all television monitors can lock onto it and be able to decode color information to display. If this accuracy is not met, there is a danger that on some monitors will not lock and produce a black-and-white image. This clock is originally generated by a 27 MHz oscillator that drives the DSP, which in turn drives the CS98000 which then drives the 4955.

To allow switching between external and internal video signals the Mitsubishi A/V mux (M52790), U5001 [sheet 10, B4], is used. The 3 video signals from the CS4955 are passed to one set of the A/V Mux inputs, and the external input video signals (CV2, Y2 and C2) are passed to another set of A/V Mux inputs. The Mux will select either set of video signals to be sent on further through the video chain. The selection is made by I<sup>2</sup>C communication on a dedicated bus from the display controller micro to the A/V Mux IC.

After internal/external selection, the three video signals are sent to the output connectors. Because the MUX IC biases the video signals to 3Vdc for Composite and Luma, 4V for Chroma, these signals must be AC coupled. The A/V mux drives the video signal through large capacitors, and a 75 Ohm resistor (C5066, 5067, 5068 and R5086, 5087, 5088). This ensures equipment compatibility even if there are DC differences between the 3-2-1 and the driven equipment (TV). The 75 Ohm resistor provides reverse cable termination for best signal integrity. Video sent through these capacitors have low frequency drop-off, causing sag in the video signal. These capacitors should be large enough not to cause any problems in horizontal synchronization, even for rapid changes in brightness (luma) of the video.

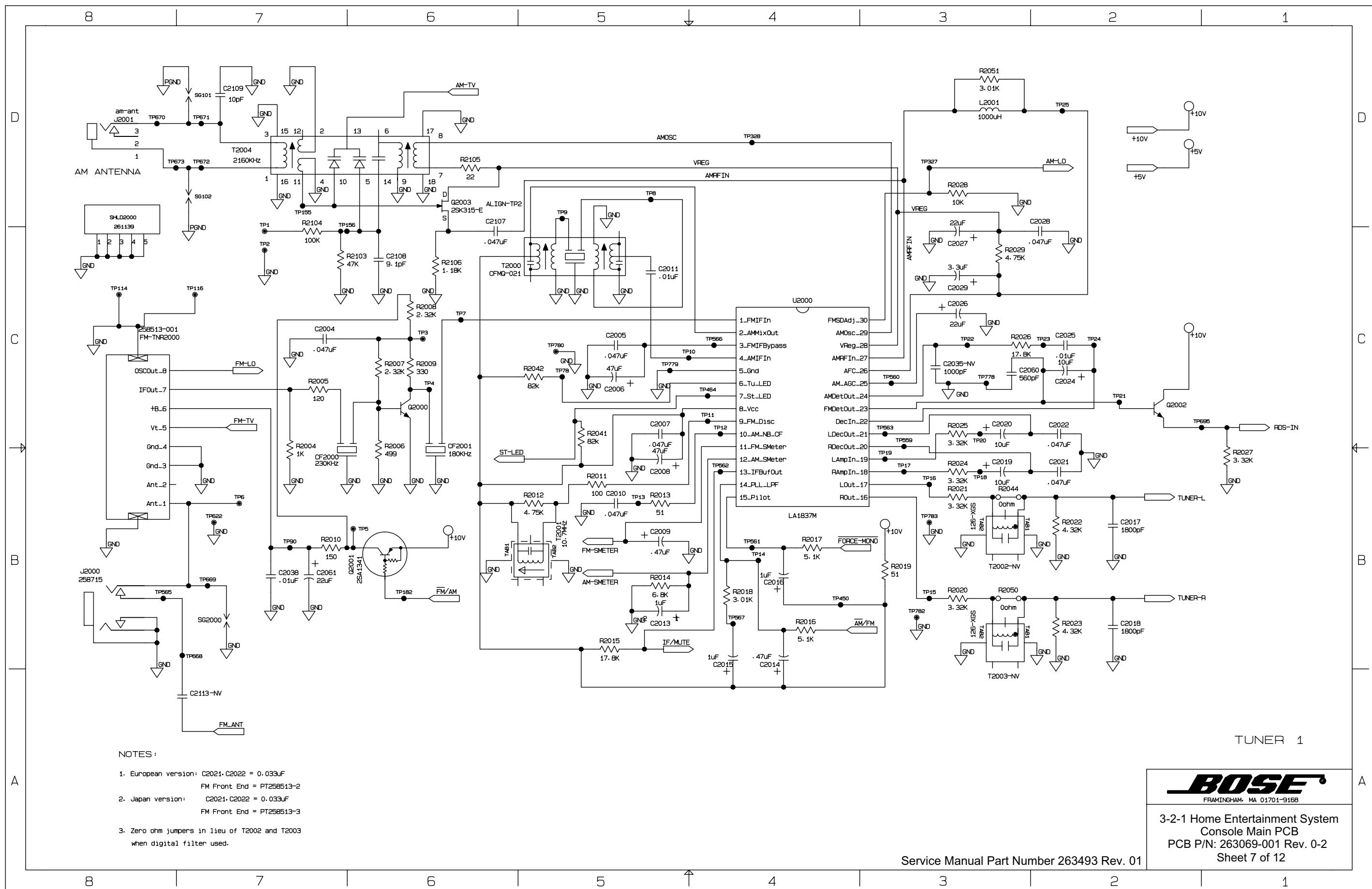

## 6.0 Tuner Electronics

### 6.1 Control

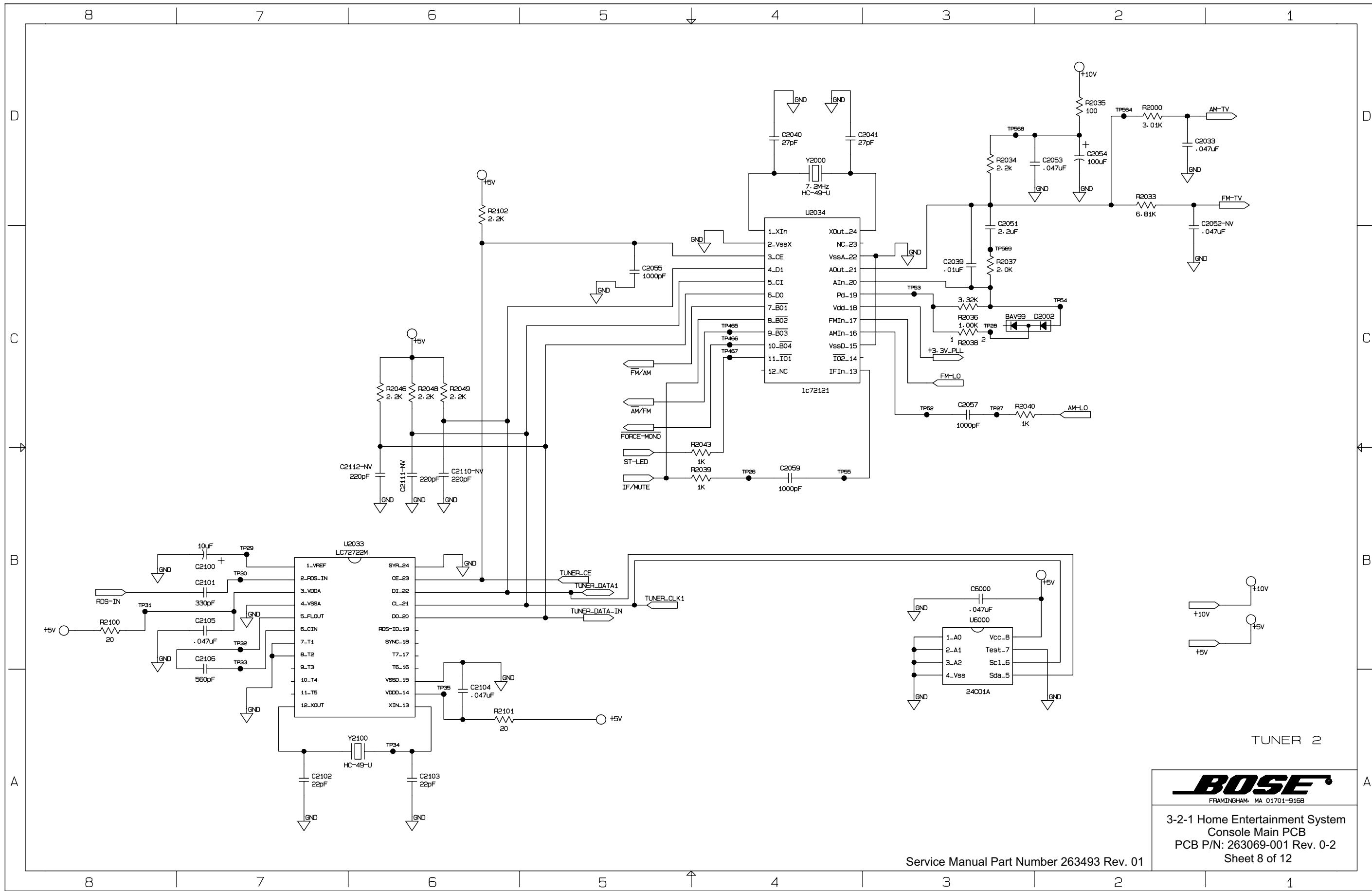

Detailed control of the tuner is implemented by the display microprocessor U3 upon instructions from the RISC processor residing inside U3000. U3000 will issue a command via the tuner bus to tune to a specific frequency and in response to this the display micro. Will communicate with the PLL IC, U2034 [sheet 8, C4], to set the local oscillator frequency as required.

The PLL IC also has some general purpose input and output ports which the display microprocessor programs as follows:

|               |                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a) FM/AM      | Controls Q2001 which switches power to the FM front-end and the IF amplifier. In AM mode these are both switched off.                                                                                                                                                                                                                                                                                       |

| b) AM/FM      | Switches the mode of detector IC U2000 and sets which output (FM : pin 23, AM : pin 24) is active. Inactive => high impedance.                                                                                                                                                                                                                                                                              |

| c) FORCE-MONO | Forces the detector IC to decode FM into monaural audio.                                                                                                                                                                                                                                                                                                                                                    |

| d) ST-LED     | This input port is used to monitor the stereo indicator coming from pin 7 of U2000. The state of this pin is shown on the stereo icon display or in the OSD FM status window.                                                                                                                                                                                                                               |

| e) IF/MUTE    | Pin 9 of U2034 is used to mute the audio output of the detector IC. When this pin is low audio output is enabled. When this pin is high impedance R2015 pulls the DC level of the IF/MUTE line high (>3.5v), audio is muted and the output of the FM IF buffer appears on this line. This is fed to the IF counter on pin 13. This is used during seek to determine if a valid broadcast signal is present. |

# THEORY OF OPERATION

## 6.2 FM Tuner

The FM RF signal from the antenna is input via the 3.5mm input connector J2000 [sheet 7, B8] and goes to the FM front-end module. The antenna supplied with the Media Center differs from the standard FM dipole antenna in that it contains a balanced-to-unbalanced converter which is designed to reduce the amount of interference from other electronic products.

The FM front-end contains a tuned RF amplifier an FM local oscillator and a mixer. The 10.7 MHz IF output signal (pin 7 of the module) passes through a 10.7 MHz ceramic filter, CF2000, an FM IF amplifier and then through a second ceramic filter, CF2001. Transistor Q2000 and related circuitry form the FM IF amplifier which produces about 15 dB of voltage gain and provides the proper impedance matching for the ceramic filters. These FM IF filter stages reject unwanted FM stations and noise.

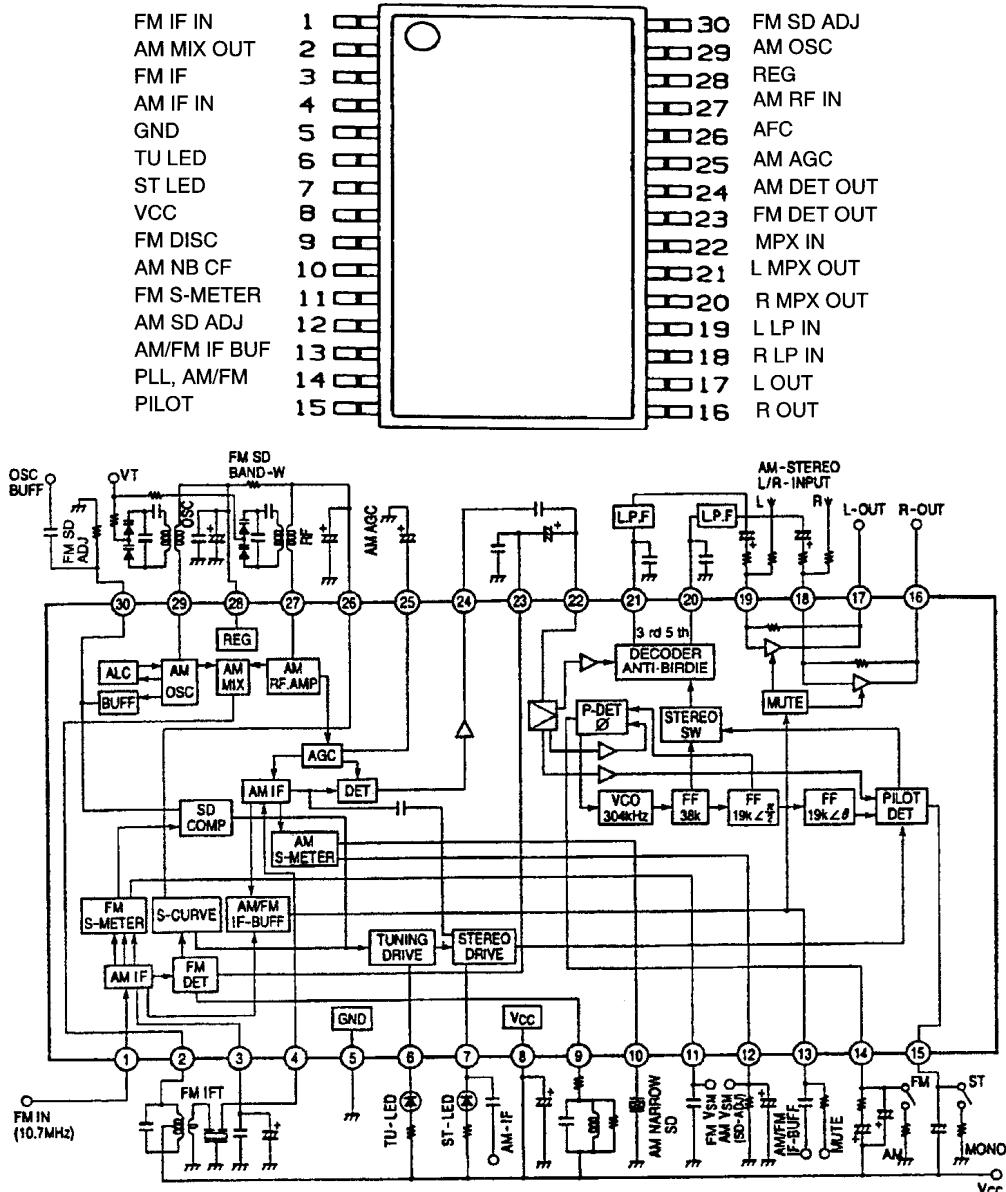

The output signal from CF2001 is fed to the LA1837 AM/FM detector IC, U2000 pin1 [sheet 7, C4]. This device contains the FM IF limiter, FM detector, FM stereo MPX decoder and S-meter circuitry which is used for seek processing. The FM IF input signal to the LA1837 goes through several gain/limiter stages and then to a single-tuned, coil-based discriminator circuit. The discriminator coil, T2001 [B5], is adjusted for minimum second harmonic audio distortion. The recovered FM composite signal appears on pin 23 of U2000.

The composite audio signal is filtered by C2060 and fed back into pin 22 of U2000. The value of C2060 is chosen to optimize FM stereo separation. The stereo MPX decoding is also performed by U2000 and the decoded left and right signals are output on pins 20 and 21. The pilot PLL VCO is completely internal to the LA1837 detector IC, not requiring an external 456 kHz ceramic resonator as in older designs. The pilot PLL loop filter is formed by C2015, R2018, and C2014 on pin 14.

FM de-emphasis for the right audio channel is set by C2021, R2024 and the output impedance of pin 21 of U2000 (3.3k). Similarly for the left audio channel. For a US unit the capacitor values are set to produce 75 $\mu$ S de-emphasis, and for Europe/Japan they are set to produce 50 $\mu$ S de-emphasis. The resultant de-emphasized and amplified audio signal appears on pins 16 and 17. Signals above the audio band, including the 38 kHz sub-channel demodulation components are cut off by the input filters in U4000 and the audio DSP is used to create a notch filter at 19kHz to reject the 19 kHz pilot tone thus removing the need for external MPX filters.

The FM and AM S-meter signals, pin 11 and 12 of the LA1837 respectively, are analog voltage levels that indicate the FM IF and AM RF input signal levels. These signals are connected to the 8 bit A/D inputs of the display microprocessor. During factory tuner alignment the appropriate test signal levels are injected into the UUT and the resultant ADC values for FM stop level, FM force-mono level, FM stereo level and AM stop level are stored in non-volatile memory on the main board.

The stop level is the voltage level above which the signal strength is deemed strong enough to warrant stopping on a channel during seek. This does not mean that the unit will always stop on a station if the S-meter level is high enough since an IF count is also performed to ensure that the correct IF frequency has been obtained.

# THEORY OF OPERATION

The force-mono level is the level below which the microprocessor will force the detector to decode audio information into monaural since the noise associated with decoding into stereo is deemed to be unacceptable. The stereo level is the level above which a channel which has been automatically forced into mono will return to being able to decode in stereo (if stereo material is present).

Note that switching stereo “on” via the OSD will enable the above automatic force-mono function while switching it “off” disables this automatic function and ALWAYS forces the unit into monaural decoding. Also note that the stereo icon on the front display and the stereo status flag on the OSD indicates the state of the ST-LED line which indicates detection of the 19kHz pilot tone present in stereo broadcasts. In force-mono (automatic or otherwise) this will always be low even if the actual broadcast is in stereo.

The nominal FM stop/force-mono and stereo levels are:

|               |                   |

|---------------|-------------------|

| FM stop       | 30 dBf @ 98.1 MHz |

| FM force-mono | 40 dBf @ 98.1 MHz |

| FM stereo     | 42 dBf @ 98.1 MHz |

## 6.3 AM Tuner

The signal from the external AM loop antenna enters through the 2.5 mm AM jack, J2001 [sheet 7, D8], and is fed to the AM front end module, T2004. This module contains the varactor-tuned RF and Local Oscillator (LO) tracking circuits. This part is pre-tuned by the manufacturer for proper alignment with AM antenna (part number 199824-002), and is further adjusted during factory alignment, if necessary. The RF tuned output is fed to the AM buffer FET transistor Q2003 and the buffered output is sent to pin 27 of U2000 which contains the AM RF amplifier, mixer, IF amplifier, AM detector, and AM S-meter circuitry. The 450 kHz AM IF output signal that appears on pin 2 is filtered by the IF filter, T2000, and fed back into the IC on pin 4. The AM IF signal is demodulated by U2000 and the audio output is sent to pins 20 and 21, to pass through the low pass filter used in FM for de-emphasis.

In order to avoid having harmonics of the switching power supplies interfere with the AM tuner the switching frequency is controlled by SYNCH\_PULSE, a clock output from the DSP, U7000. The display microprocessor contains a table of clock frequency vs AM channel frequency and each time a new channel is tuned, the DSP is commanded to change the SYNCH\_PULSE frequency to the appropriate frequency. The frequency of SYNCH\_PULSE is centered around 100 kHz.

The AM seek stop processing and factory alignment is performed in a similar fashion to FM mode processing. The nominal AM stop level is 58 dB $\mu$ V/m @ 1080 kHz.

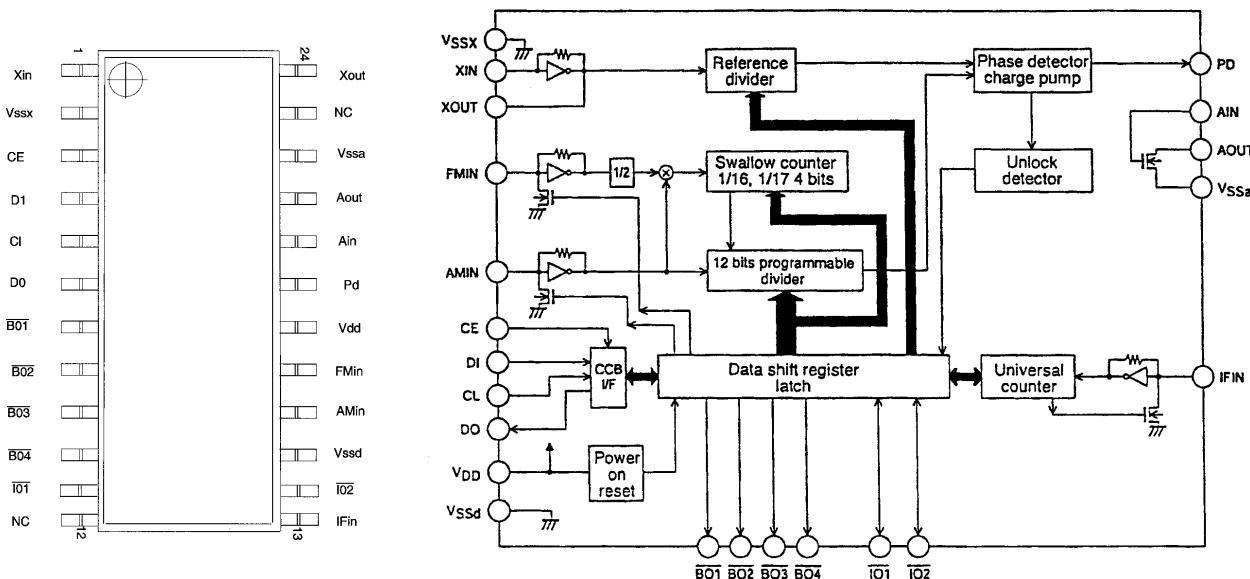

## 6.4 Phase-locked Loop Tuning

The AM and FM local oscillators are controlled by the PLL IC, U2034 [sheet 8, C4]. The microprocessor selects the AM or FM band and the particular frequency. The 7.2 MHz crystal, Y2000, is connected across an inverting amplifier inside U2034 to form an accurate and stable crystal oscillator. The 7.2 MHz oscillator is divided down to produce a 12.5 kHz reference frequency in FM mode and a 10 kHz reference frequency in AM mode. U2034 divides down the AM or FM LO input, compares it to the appropriate reference frequency and generates an error signal which is output on pin 19.

# THEORY OF OPERATION

This error signal is integrated and amplified by an active lead-lag filter formed using an internal FET inside U2034 and associated components connected to pins 19, 20 and 21. C2051, C2039, R2037, R2036 and R2038 control the gain and pole-zero locations of the filter. The resulting signal output at pin 21 is used as a tuning voltage and is fed back to the AM and FM front-ends.

The AM tuning voltage is further filtered by R2000 and C2033 and is fed back to the common node of the varactors inside the AM front end, T2004. The tuning voltage varies the capacitance of the varactor diodes, which in turn simultaneously tunes both the AM antenna and the AM LO. In FM mode, the tuning voltage is filtered by R2033 and the input capacitance of pin 5 of the FM front-end (0.022uF). As in the AM case, the tuning voltage is fed to varactors which tune the LO frequency and RF filtering.

## 7.0 DVD Electronics

The DVD-ROM drive is a Toshiba model SD-M1502. The drive is capable of playing DVDs (including CSS decoding), CD-ROMs, and audio CDs. An ATAPI cable for data and separate power cable connect the drive to the Main PCB.

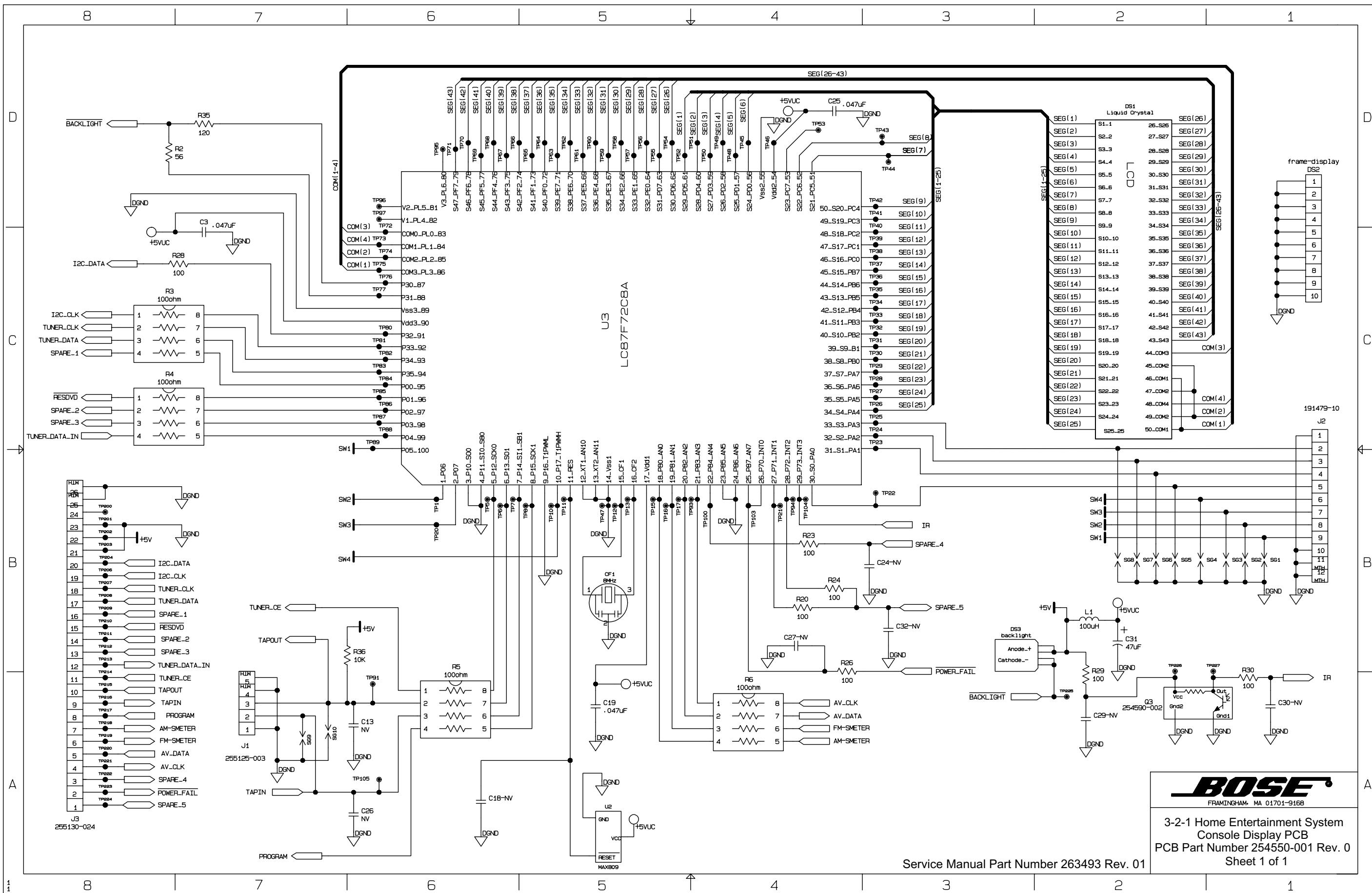

## 8.0 LCD Display

**Note:** Refer to the LCD display schematic sheet 1 for the following information. The information inside the brackets [ ] is the grid location on the schematic sheet for the component.

The Console display board is comprised of the uC PCB, and display parts: the display frame, LCD glass, diffuser, LED backlight, and elastomers. The frame holds all the display parts by compressing the elastomers and the twisted tabs. Behind the LCD glass is the diffuser. The diffuser serves a dual purpose: as a light diffuser to balance the light output at different viewing angles, and as a black mask around the edges to mask light leaking out. Behind the diffuser is the LED light pipe backlight. Having the smooth side of the diffuser towards the backlight helps with the overall light output. The LED light pipe is made up of a single super-bright green LED molded on its side inside a transparent plastic piece at one end. The LED light (green for US) fires off that (left) end axially down the length of the light pipe. Internal refraction keeps the light within the light pipe. Micro-lenses on the backside of the light pipe direct the light through the front of the pipe. A white reflector sheet on the backside and the non-LED end of the light pipe reflects some leakage light back to the pipe. White elastomers and white silkscreen printing on the PCB also help reflecting some light back to the pipe. There are three elastomers: two long strips for the LCD glass and one short piece for the LED light pipe. Signals and power are connected via the direction of the thin layers within the elastomers. While the two long pieces for the LCD are carbon based, the short piece for the LED is silver based. On the PCB the elastomers are compressed onto the carbon printing pads to make connections. On the LCD, the long elastomers are compressed against the shelf side of the glass, where there are exposed conductive ITO pads (faintly visible when viewed against bright light). On the LED light pipe, the short elastomer is compressed against the wrapped around LED leads in the cavity on the backside of the pipe.

The LCD is a passive matrix (4x43) alphanumeric type (two 7-segment numeric characters, eight 14-segment alphanumeric characters, and various other icons), with a total of 167 individually addressable icons. The LCD is a backlit transmissive negative-image type. The center row of alpha-numeric characters show detailed information such as titles and presets (left two numeric characters), chapters, tracks, time, volume, text, as well as system status messages, modes and selections (right 8 alpha-numeric characters).

# THEORY OF OPERATION

System messages and mode selections are also displayed by icons in the surrounding area. These include: TITLE, PRESET, CHAPTER, TRACK, SETTINGS, ANGLE, SLEEP, SHUFFLE, REPEAT DISC, REPEAT TRACK, MOVIE EQ, RDS, and STEREO. Besides punctuation marks, there are also the 'play' and 'pause' graphics icons. Mode selections are displayed on the bottom row of icons: DVD, CD, AUX, VIDEO 1, VIDEO 2, AM, and FM. With the exception of either CD or DVD, all source icons are displayed to allow source selections when the system is turned on. A graphics 'box' icon around a source icon indicates that the corresponding source is selected. The LCD has a viewing area of 28mm x 100mm. It is biased for a 12 O'clock (top) viewing direction (60/60/60/20 degrees viewing angles, where 20 degree is for the bottom view).

The 167 individual icons are addressed by the LCD microcontroller (uC) U3 [C5] on the PCB. There are 4 COM lines and 43 SEG lines out of the uC. There are also 43 SEG pins on the LCD. However, there are 7 COM pins on the LCD. Some of the 7 COM pins are connected on the PCB to match the 4 COM lines on the uC. To select an icon on the matrix, the corresponding COM line and SEG line (as the matrix indices) are asserted. To select all icons of a COM line, that COM line and all the SEG lines are asserted. To select all icons associated with a SEG line, all COM lines and that SEG line are asserted. By the same token, a short or open on some lines would cause all the icons associated with those lines to light up or not light up.

The LCD is operated off a 5V drive, at 1/3 bias. While an icon is not addressed, the corresponding COM and SEG lines are refreshed with rectangular AC type DC-biased waveforms whose difference is also a rectangular AC waveform with peaks below the turn-on voltage of the icon. It's only when the icon is addressed that the difference becomes larger than the turn-on voltage for a portion of the time (1/4 duty given that the system is 1/4 multiplexed by 4 COM lines). In other words, for a selected icon the COM - SEG difference waveform would have portions reaching the peaks 0V and 5V, during 1/4 of the time. Vice versa for a non-selected icon, the COM - SEG waveform would have portions away from the peaks 0V and 5V by at least 1/3 of 5V, or 5/3 V all the time.

When the Console is turned off, both the LCD and the LED backlight are turned off. When the Console is turned on by the pressing of console buttons or remote, the LCD and the LED backlight are both turned on. The LED backlight's brightness is bright when the Console is first turned on. It remains bright for approximately 7 seconds. Afterwards it goes to normal brightness. It remains in normal brightness until the next time a console button is pressed or a remote command is received, when it goes to bright mode. The LED remains bright for approximately 7 seconds after the last key press or remote command. System initiated updates on the display such as time and track changes do not cause the LED backlight to brighten.

The uC U3's ports P30 and P31 control the LED backlight's brightness. In the normal brightness, only P31 is asserted LOW. LED current goes from +5V through the LED to BACKLIGHT and returned through P31 only. In the bright mode, both P31 and P30 are asserted LOW. A larger LED current returns through both ports. In the OFF mode, both P31 and P30 are asserted HI, resulting in zero LED current.

Console switches are connected to the uC U3 via connector J2. The 8 switches are not multiplexed but simply sampled by the uC. Each uC port connected to a switch has an internally pulled-up resistor. Closing a switch or shorting the corresponding port pin to GND is detected by the uC as a key press. IC's that hang off the uC include a reset chip U2 at port RES, and a remote sensor Q3 at port P73. Both ports are normally high and LOW active. The reset chip resets (LOW) when +5VUC drops below 4.63V nominally. A ceramic resonator CF1 provides the main clock for the uC U3, at 8MHz.

# THEORY OF OPERATION

Communication with the Console main PCB is via connector J3. Off -board communication is via J1, the TAP port. Through the TAP port the system usage profile can be obtained.

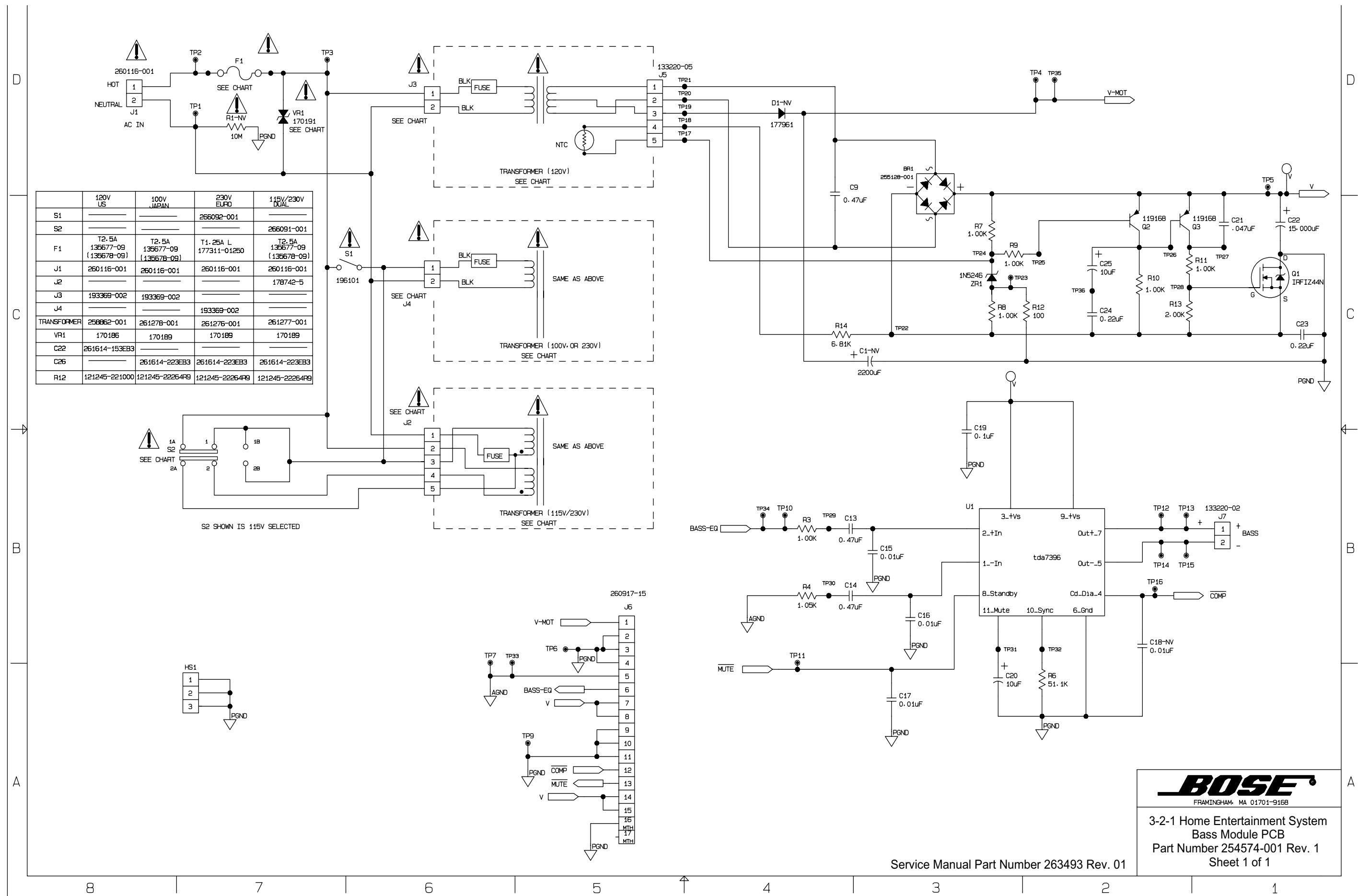

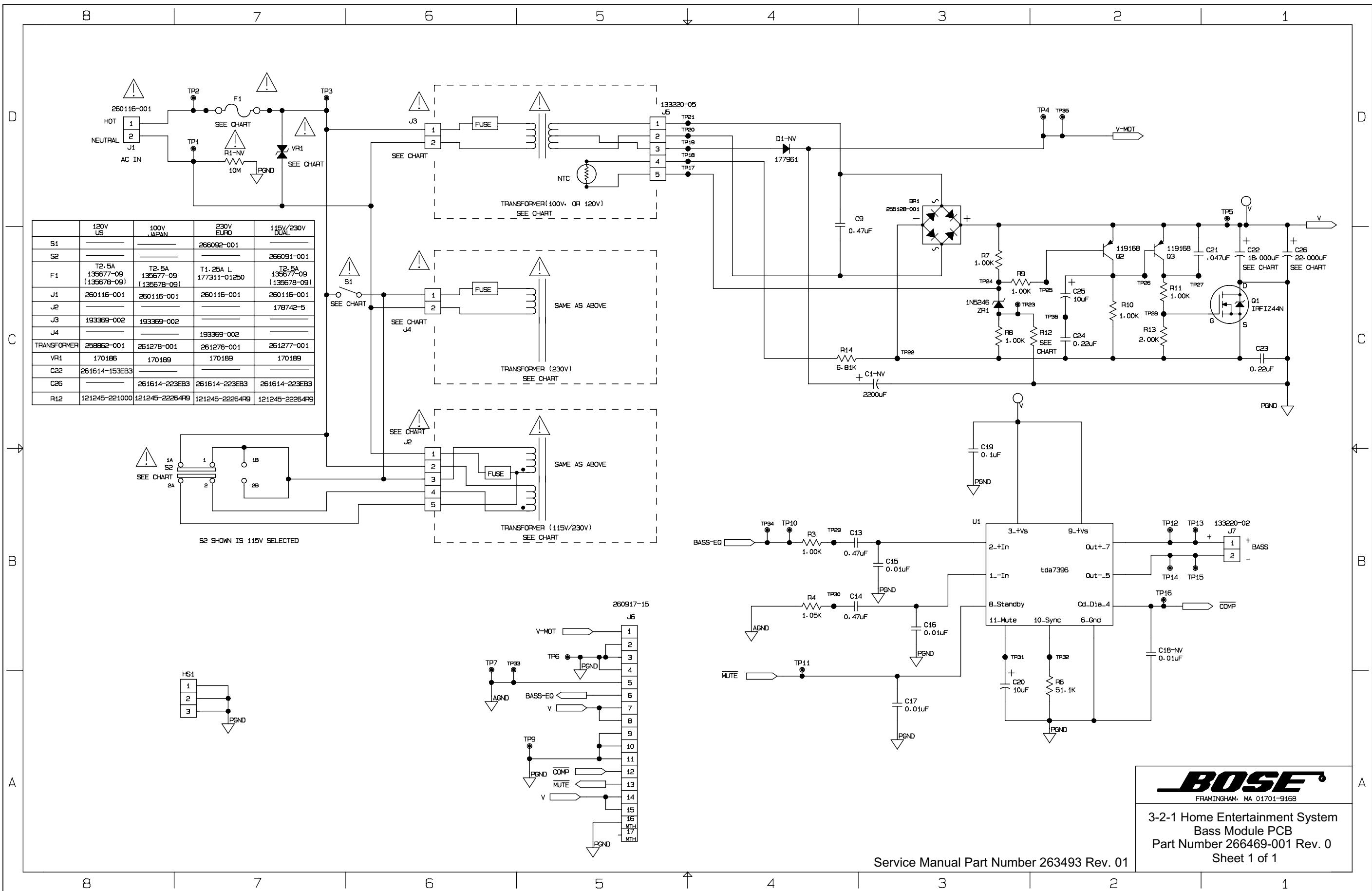

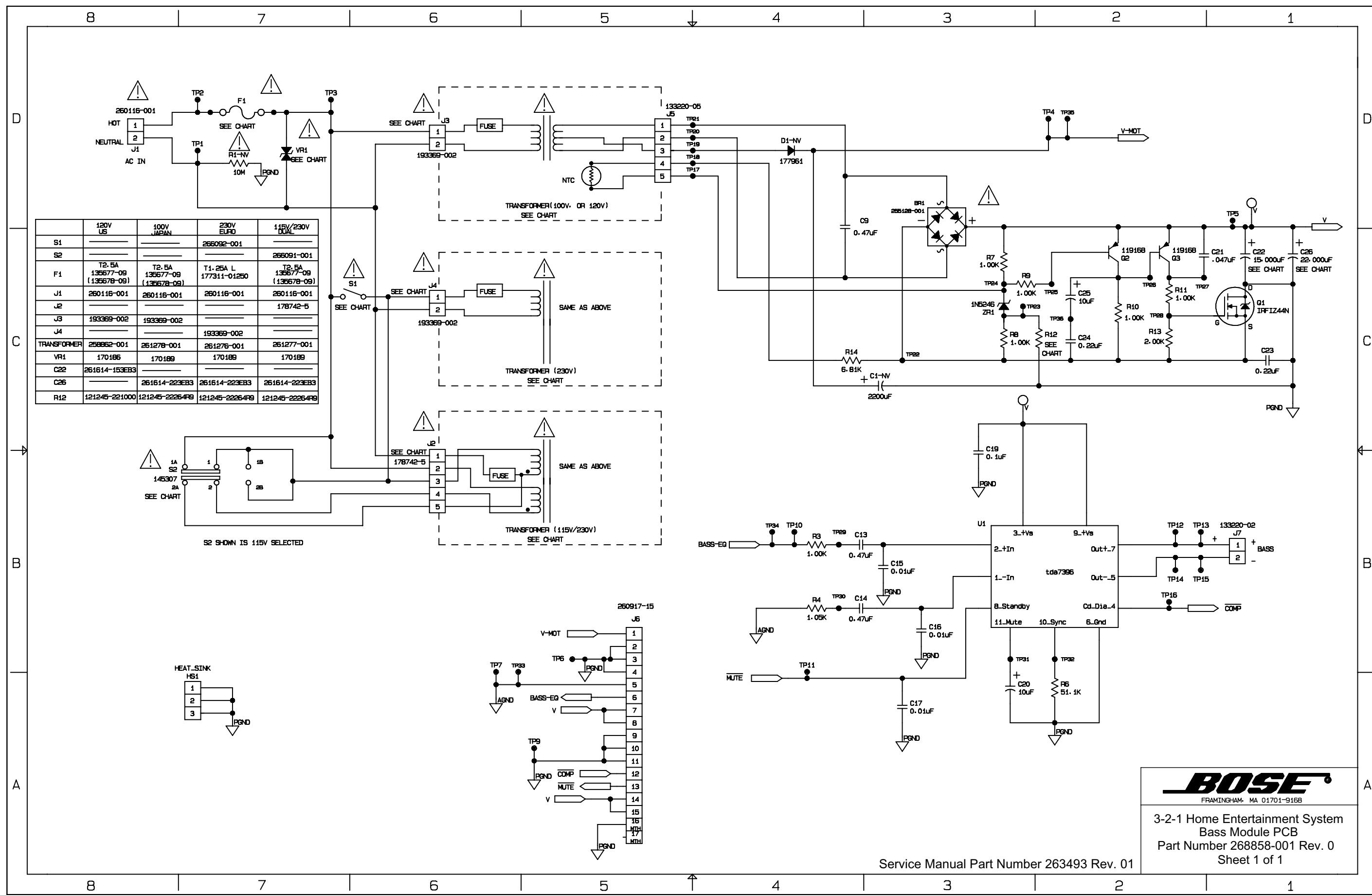

## 9.0 Bass Module

**Note:** Refer to the bass module schematic sheet 1 for the following information. The information inside the brackets [ ] is the grid location on the schematic sheet for the component.

### 9.1 Power Supply Electronics

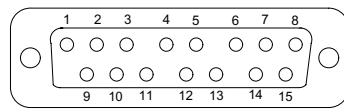

The bass module is a single channel system: its differential input is converted to accept a single ended bass signal from the console; the bridge output is connected to a 2 Ohm bass driver through J7 [B1]. The bass power amplifier U1 [B2] is a class AB type and is powered by a DC power supply (V). The same power supply (V) is shipped to power the console via a cable connected to the D-sub connector J6 [A6]. The bass signal and control signals from the console are sent through the same cable bundle. The console does all of the signal processing, equalization, and control. The bass module PCB supplies the main power supply (V) for the bass module and the console. The bass module PCB also amplifies the bass from the console using the same main power supply (V). The bare PCB is a universal PCB suitable for all bass module variants.

AC mains power is connected by the line cord via jack J1. A slow acting fuse F1 is connected between J1 [D7] and the locking primary connector J3 (or J2 or J4) to protect against faults. A Metal Oxide Varistor (MOV) VR1 is placed after the fuse and across the line. It is used to protect against lightning strikes and other line transients. Transformer T1 connects to primary connector J3 (or J2 or J4) and secondary connector J5. Polarized locking jack J5 ensures the correct connection of the pins from T1. Depending on the voltage variants, unique transformers, primary jacks, and if required, switches are used. F1 and VR1 [D7] also have unique values. See the bass module schematic diagram for details.

Transformer T1 has a primary winding unique for different AC mains voltage requirements. However it has about the same single secondary winding. The primary has a series thermal fuse to protect against overload and faults. The secondary winding has an optional center tap (currently not used) that can be part of a half-supply voltage circuit. There is also a Negative Temperature Coefficient (NTC) thermistor/sensor embedded inside the transformer. It is used in the power (voltage) limiting circuit in the event of overload. Large brackets and fins on the transformer help with power dissipation.

The main power supply V of the system is derived from the full wave rectifier BR1, filtering capacitor C22 and MOSFET switch Q1. It is a line frequency cycle-controlled switching power supply. By inserting the switch element Q1 in series with BR1 and C22, and controlling the OFF and ON times of Q1, a regulated maximum voltage can be obtained at V. Without the switch Q1 in series, BR1 and C22 would become a simple rectifier-capacitor AC-DC circuit, which would just full-wave rectify the secondary AC voltage of transformer T1. With Q1, the charging current is cut off when the voltage across C22 reaches a threshold (close to V). This is accomplished by the control circuit made up of ZR1, Q2 and Q3, etc.

During the rising edge of the rectified AC, when the full wave rectified output (between + and - terminals of BR1) rises beyond the zener voltage of zener diode ZR1, it is turned 'on' and clamped at its zener voltage (16V). The 'turn-on' of ZR1 causes excess current flow, which turns on Q2. The 'turn-on' of Q2 forces Q3 to turn 'off', and consequently Q1 to turn 'off'. When Q1 turns 'off', the charging current is cut from C22 to prevent further charging to a higher voltage.

# THEORY OF OPERATION

Normally this happens before the rectified AC climbs to its peak.  $V$  is therefore limited to approximately 16.5V (between 15.5V and 17.5V) peak. In other words, on the rising edge of the rectified AC voltage, charging of  $C_{22}$  is turned off after its voltage has reached  $V$ .

On the falling edge of the rectified AC voltage, charging of  $C_{22}$  is turned back on before the falling rectified AC voltage reaches  $V$ . The 'turn-on' of  $Q_1$  prior to reaching  $V$  is accomplished by the help of  $R_{12}$  and the unloading effect of the transformer  $T_1$ . Right after  $Q_1$  turns 'off', the unloading of the charging current on the transformer allows the transformer to have a larger unloaded output voltage, resulting in a voltage across  $Q_1$  (i.e., the unloaded rectified AC voltage minus the voltage across  $C_{22}$ ,  $V$ ). The voltage across  $Q_1$  re-biases the voltage of the zener  $ZR_1$  through  $R_{12}$  (and  $R_8$ ). The base of  $Q_2$  is biased up, resulting in an earlier 'turn-off' prior to the voltage falling to  $V$ . Consequently  $Q_3$  and  $Q_1$  turn 'on' earlier. The rest of the charging is governed by  $BR_1$ : it turns 'off' after the rectified AC voltage falls below  $V$ .

After  $Q_1$  turns 'on' on the falling edge, it remains 'on' until it turns 'off' on the rising edge (after reaching  $V$ ). During  $Q_1$ 's 'on' time,  $BR_1$  turns off on the falling edge but turns back 'on' on the rising edge.  $C_{22}$  is charged only when both  $Q_1$  and  $BR_1$  are on. That happens on two occasions for each half line cycle: once on the rising edge and the other on the falling edge. That means that for normal loads there are four charging periods for each line cycle. For light or no loads,  $Q_1$  sometimes turns 'on' only once in a while depending on the load. Charging may happen just on one rising or falling edge for the full line cycle. It may even happen every other cycle. Or it may happen on both edges for a half cycle but skip the next. For heavy loads  $Q_1$  stays 'on' all the time. The circuit then behaves just like a bridge ( $BR_1$ ) and a capacitor ( $C_{22}$ ) with  $Q_1$  shorted - the normal AC-DC charging circuit.

While in theory the above is true descriptions of the voltages, in reality there are some subtle differences in the actual circuit. For example, the 'rectified AC voltage' is not the normal waveform of the absolute value of the sine wave. When  $Q_1$  turns 'off', the back-bias through  $R_{12}$  actually applies the  $V$  voltage across the circuit. When  $BR_1$  is not in the conduction mode for charging  $C_{22}$ , the back-biased  $V$  voltage powers the control circuit, creating a voltage across the + and - terminals of  $BR_1$ . The voltage across + and - terminals of  $BR_1$  then looks like the larger of a normal rectified AC voltage and a flat DC voltage of approximately  $V$ . Another example is at the base of  $Q_3$ . That voltage is being modulated between a  $V_{be}$  (of  $Q_3$ ) and a  $V_{ce}$ , sat (of  $Q_2$ ). Furthermore, transients are ignored in the descriptions. One of such transients is created by the 'turn-off' of the charging current on the rising edge. That transient creates a spike voltage across the whole control circuit, including  $Q_1$ . Measures such as by-pass and smoothing caps ( $C_{24}$  and  $C_{21}$ ) are put in place.  $Q_1$ 's 'turn-off' is slowed down to suppress that transient and dissipate the heat.  $C_{23}$  is used to suppress ringing and prevent reverse-bias conditions on  $Q_2$  and  $Q_3$ .  $C_9$  is used for suppression of line conducted emissions.

In the event of overload or overheating of the transformer  $T_1$ , the embedded NTC thermistor that's connected to the zener bias circuit controls the output voltage at  $V$ . When the transformer overheats, the resistance of the NTC thermistor drops. At around 100 degrees C, the NTC starts to become effective in the circuit. Through  $R_{14}$ , the NTC takes the bias current from  $ZR_1$ , resulting in a lower threshold voltage for  $V$ . By the time the transformer heats to around 125 degrees C (if it does), the NTC becomes fully effective. It consequently limits the voltage at  $V$  to be below 10V. The lowered voltage at  $V$  means less power available, and less power dissipated by the transformer. The lowered power dissipation allows the transformer to cool. Eventually the system servos to such that the transformer temperature is between 100 degrees C and 125 degrees C, below its rated temperature of 130 degrees C. Under normal ambient temperature and normal loads, the voltage  $V$  is not compromised by the NTC.

# THEORY OF OPERATION

## 9.2 Audio Signal Path

The bass module amplifier PCB utilizes a TDA 7396 IC for the bass channel audio. The equalized bass audio signal is fed from the 3-2-1 console, down the 15 pin cable, and into the bass amplifier PCB at pin 6 of J6. This single-ended bass audio signal is then fed to pin 2 of the bass channel amplifier IC, U1. The bass audio output of this IC is taken off of pins 5 and 7, which is fed to the single woofer through J7.

In addition to bass channel audio from the 3-2-1 console, the console also supplies a DC voltage level to the /MUTE input of the bass module at pin 13 of J6. This +5Vdc level is used to un-mute the bass channel amplifier IC U1, taking it out of standby. Without this DC voltage, the device will not come out of standby, and no bass channel audio will be heard. When testing the bass module without the console attached, you will need to provide this +5Vdc level to allow the bass module to un-mute. Refer to the bass module test cable fabrication instructions in the Appendix of this service manual.

**Note:** The /COMP signal output of the bass module at pin 12 of J6 is not used.

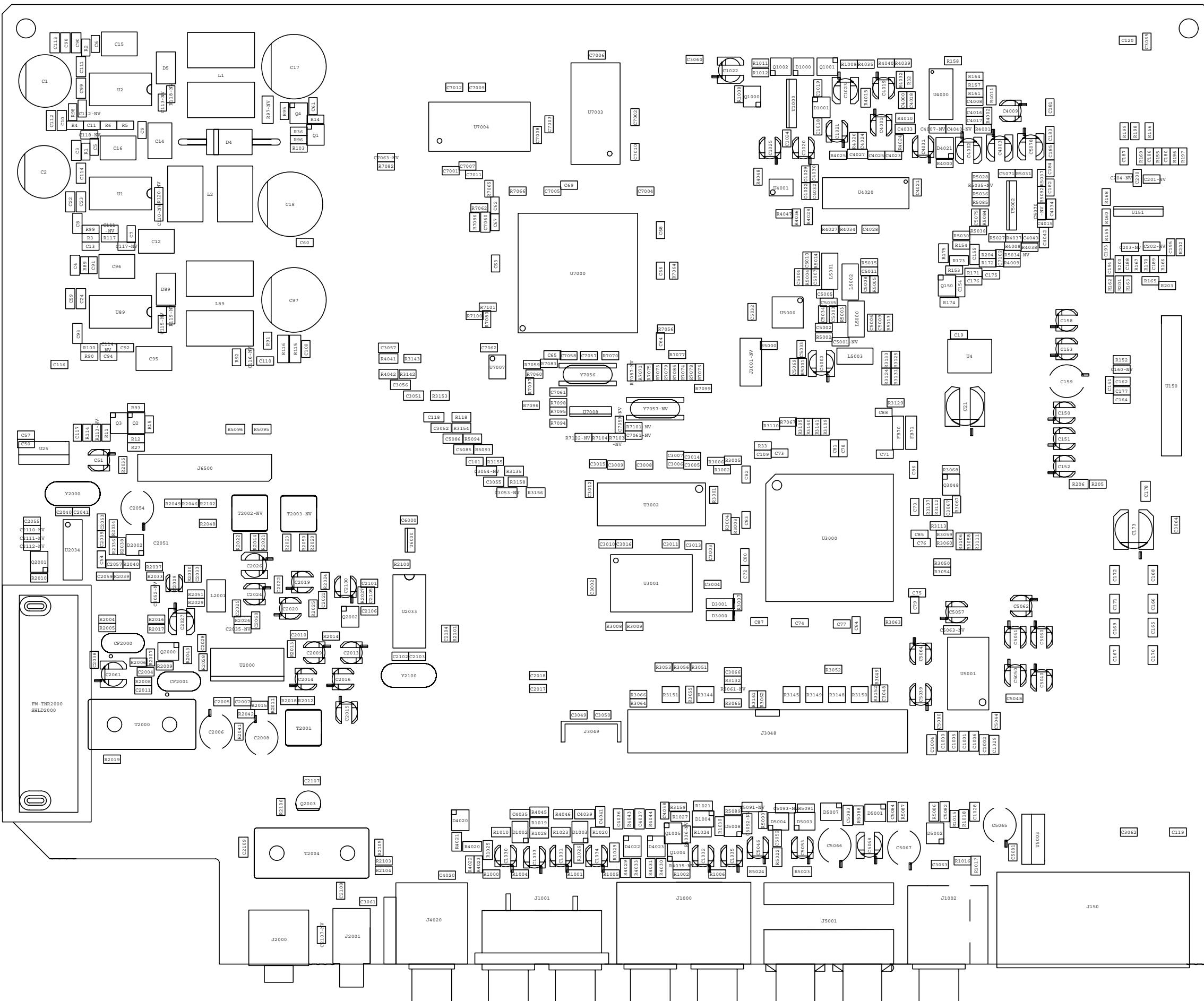

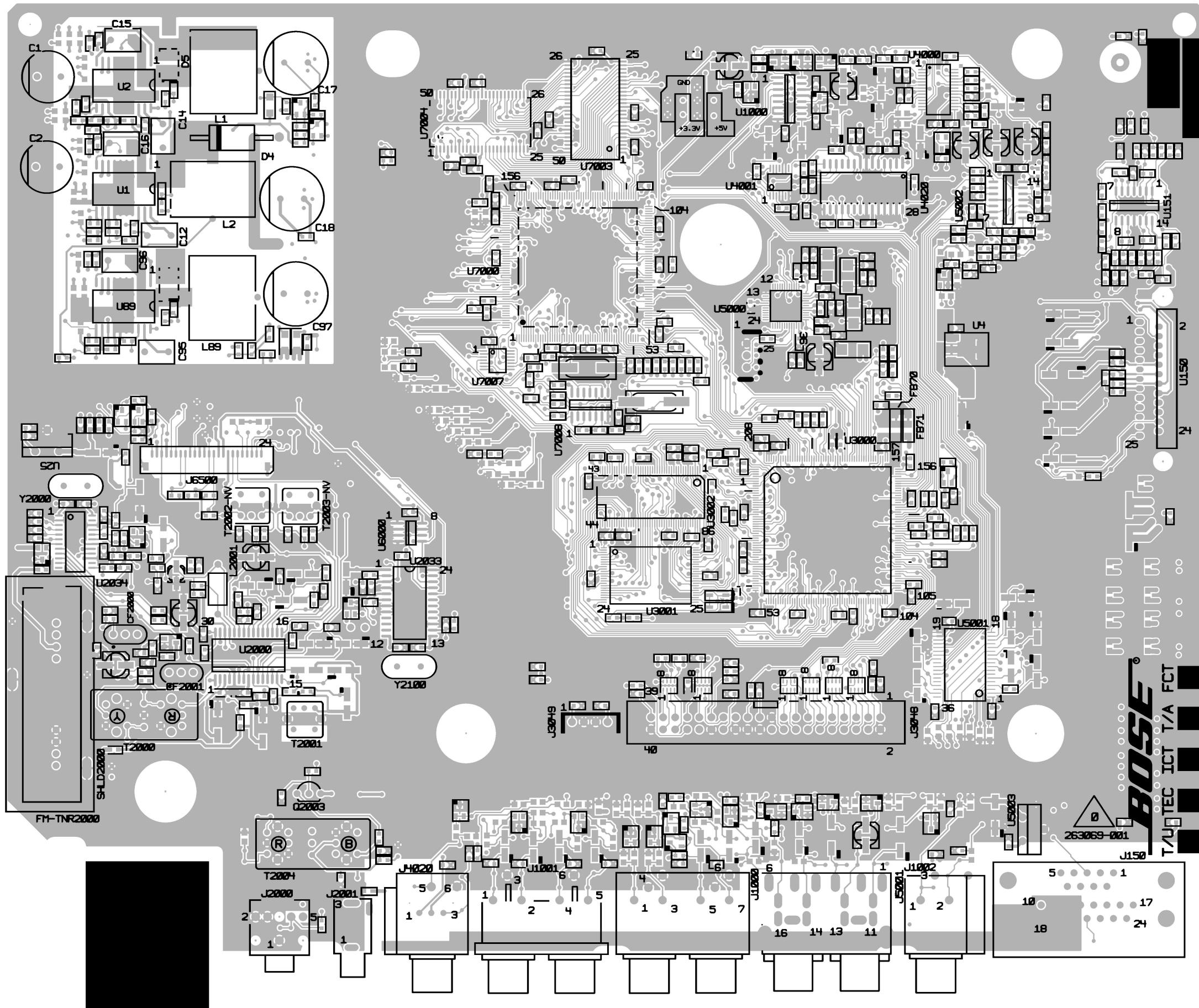

Figure 1. 3-2-1 Console Block Diagram

Figure 2. 3•2•1 Console Test Setup Diagram

**Figure 3. 3•2•1 Bass Module Test Setup Diagram**

**Figure 4. 3•2•1 and 3•2•1 GS Satellite Speaker Wiring Diagram**

# TEST PROCEDURES

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <p><b>Console Procedures</b></p> <p><b>CAUTION:</b> The DVD drive mechanism should not be closed by pushing it shut with no power applied to the console. Doing so could damage the drive. It must be closed with power applied so that the locking mechanism inside the drive will engage properly when the drawer is closed.</p> <p><b>Equipment required:</b></p> <p>Audio signal generator<br/>Digital multimeter<br/>Analog to S/PDIF converter<br/>S/PDIF to optical converter<br/>AM/FM signal generator<br/>Video signal generator or DVD player<br/>Abex test DVD (TDV-540A)<br/>Video monitor<br/>DC power supply or bass module w/cable<br/>Composite Video cable<br/>S-Video cable<br/>Optical cable</p> <p><b>Test Setup</b></p> <p>Set up the unit under test as shown in Figure 2 for the following tests.</p> <p><b>1. Analog Audio Test</b></p> <p><b>1.1</b> Apply a 1 Vrms, 1 kHz signal to the left and right VIDEO 1 audio analog inputs.</p> <p><b>1.2</b> On the console, select the VIDEO 1 input.</p> <p><b>1.3</b> Measure the output level at the audio outputs on the console rear panel. It should be 470 mVrms <math>\pm</math> 10%.</p> <p><b>1.4</b> Repeat steps 1.1 to 1.3 for the VIDEO 2 and AUX audio analog inputs.</p> <p><b>2. Coaxial Digital Audio Test</b></p> <p><b>2.1</b> Connect the audio signal generator to the input of the analog to S/PDIF converter.</p> | <p><b>2.2</b> Connect the output of the S/PDIF converter to the VIDEO 1 coaxial digital input.</p> <p><b>2.3</b> Apply a 500 mV, 1 kHz signal to the analog input of the S/PDIF converter.</p> <p><b>2.4</b> On the console, select the VIDEO 1 source.</p> <p><b>2.5</b> Measure the output level at the line outputs on the console rear panel. It should be 300 mVrms <math>\pm</math> 10%.</p> <p><b>2.6</b> Repeat steps 3.1 to 3.5 for the VIDEO 2 digital coaxial input.</p> <p><b>2.7</b> Repeat steps 3.1 to 3.5 for the AUX digital coaxial input.</p> <p><b>3. Optical Digital Audio Test</b></p> <p><b>3.1</b> Connect the audio signal generator to the input of the analog to S/PDIF converter.</p> <p><b>3.2</b> Connect the output of the S/PDIF converter to the input of the S/PDIF to optical converter.</p> <p><b>3.3</b> Connect the output of the optical converter to the VIDEO 1 optical input.</p> <p><b>3.4</b> Apply a 250 mV, 1 kHz signal to the analog input of the S/PDIF converter.</p> <p><b>3.5</b> On the console, select the VIDEO 1 source.</p> <p><b>3.6</b> Measure the output level at the line outputs on the console rear panel. It should be 150 mVrms <math>\pm</math> 10%.</p> <p><b>4. Video Tests</b></p> <p><b>4.1</b> Connect the video generator or DVD player to the COMPOSITE VIDEO INPUT only.</p> <p><b>4.2</b> Connect the video monitor to the COMPOSITE VIDEO OUTPUT.</p> |