# harman kardon Model DVD 37

# DVD/CD/CD-R/CD-RW/VCD MP3 Player

# Service Manual

### - Contents -

| SERVICE PRECAUTIONS2     | BASIC TROUBLESHOOTING GUIDE  | 26  |

|--------------------------|------------------------------|-----|

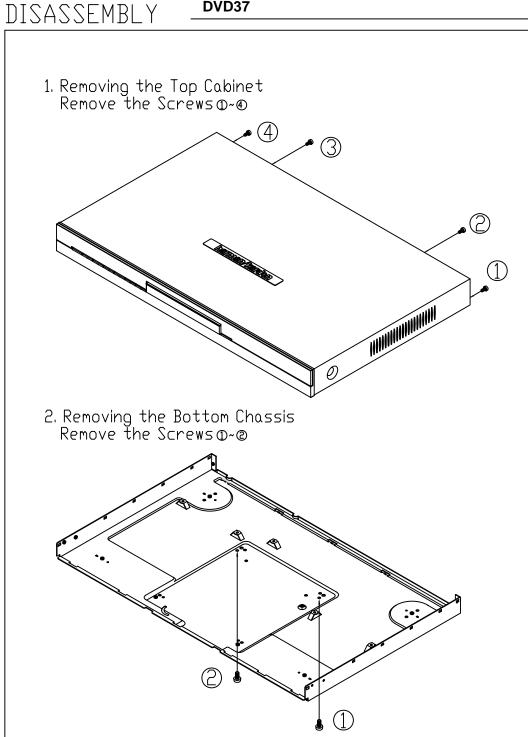

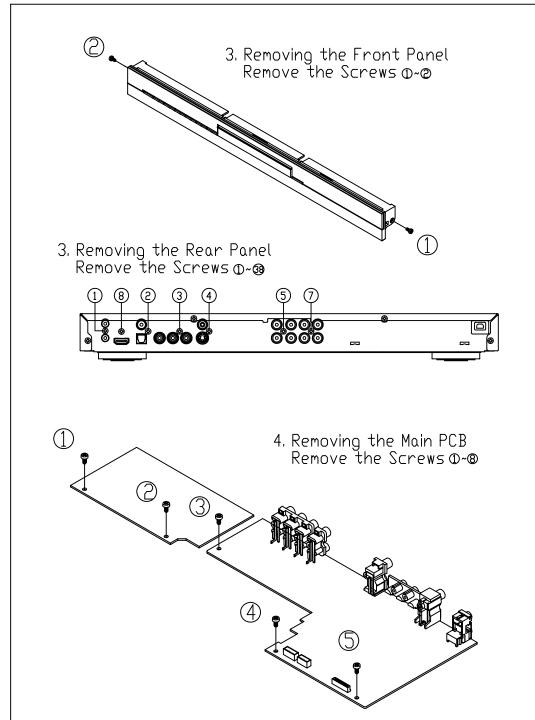

| BASIC SPECIFICATIONS5    | DISASSEMBLY PROCEDURE        | 27  |

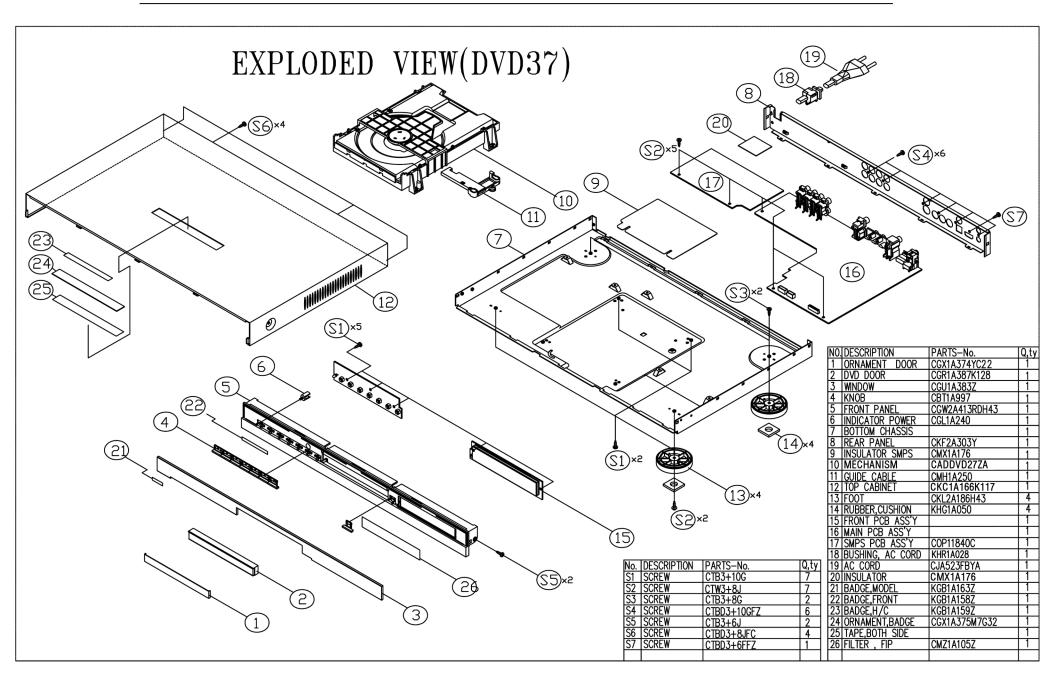

| DETAILED SPECIFICATIONS6 | EXPLODED VIEW (120v)         | 28  |

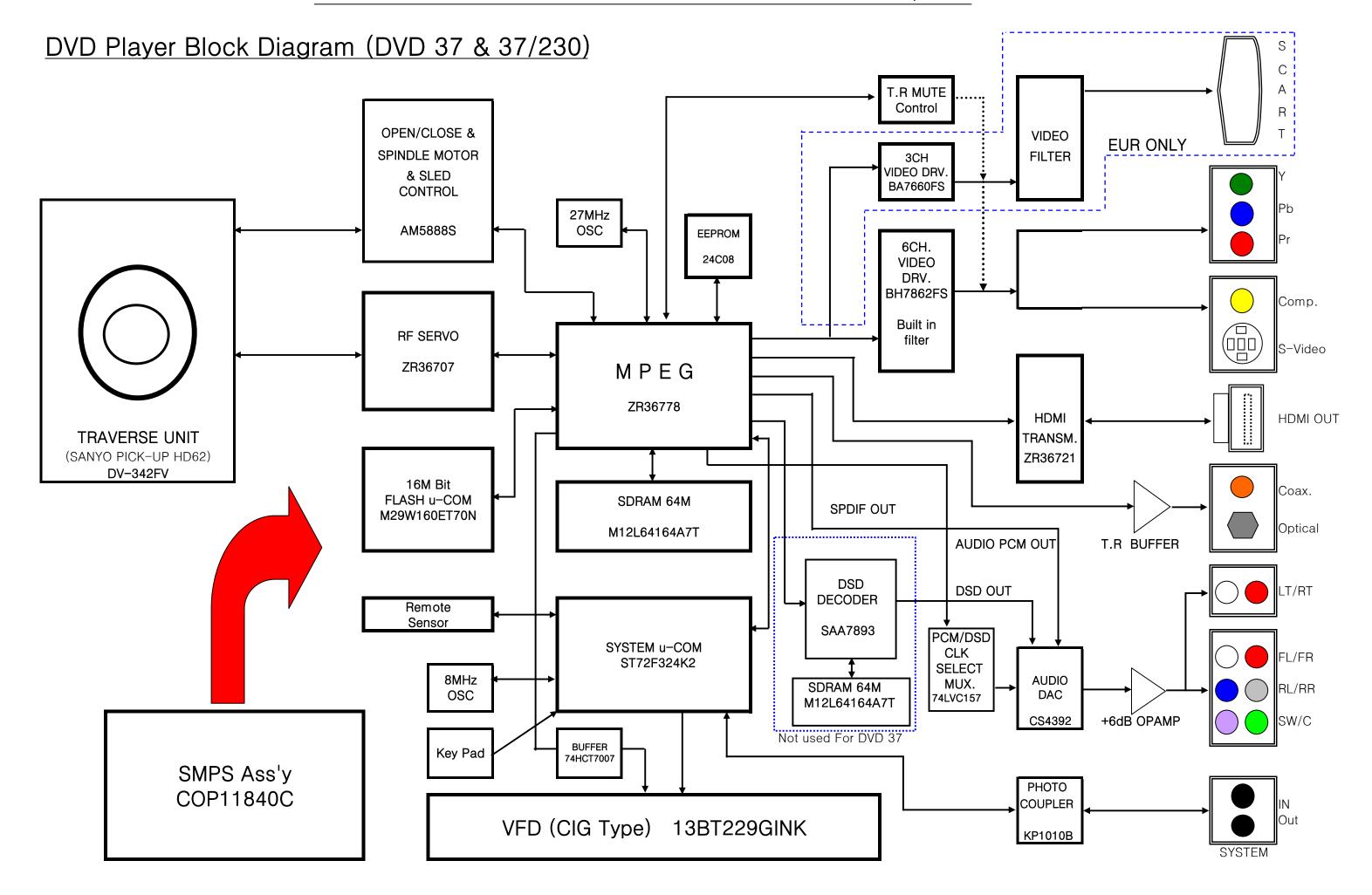

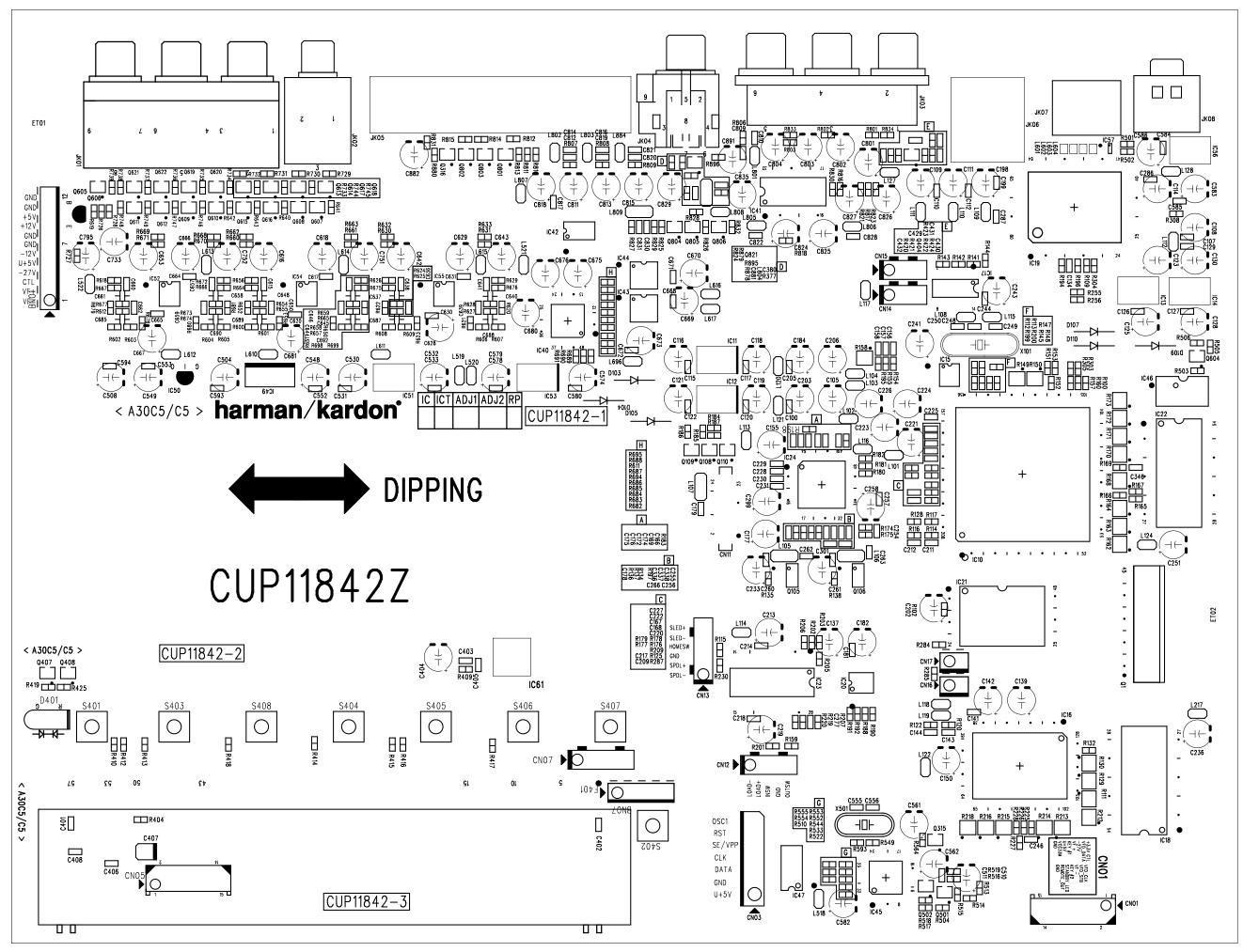

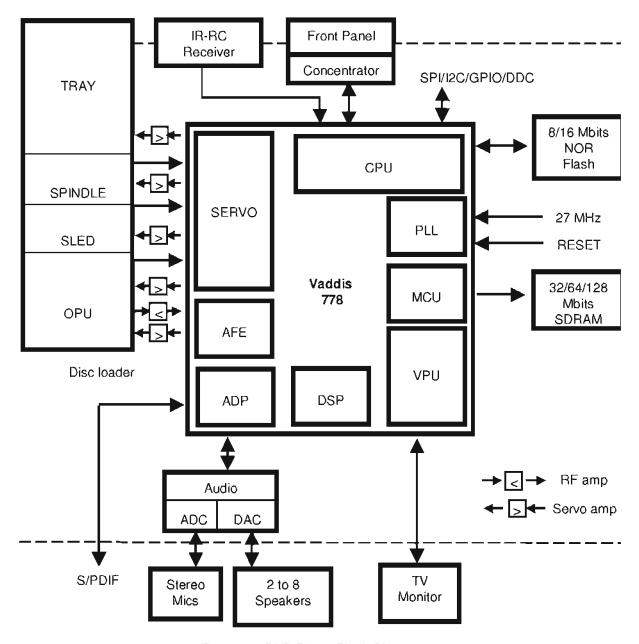

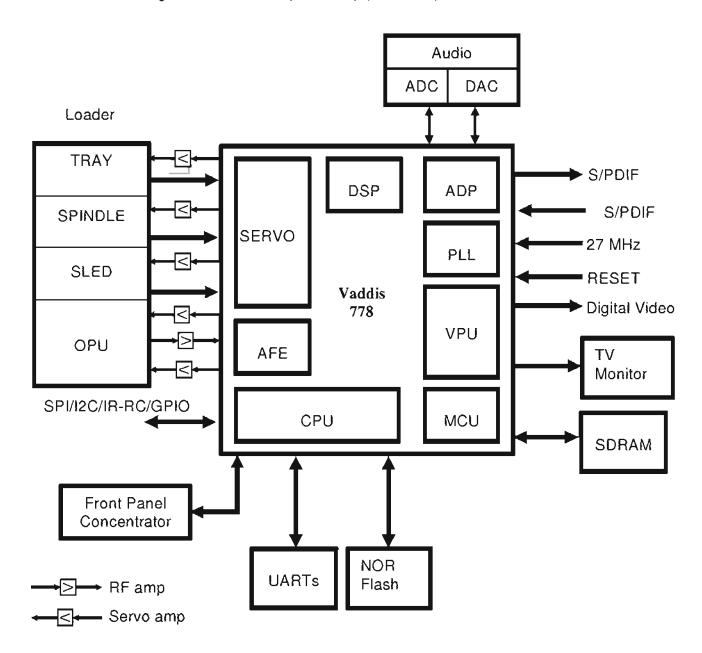

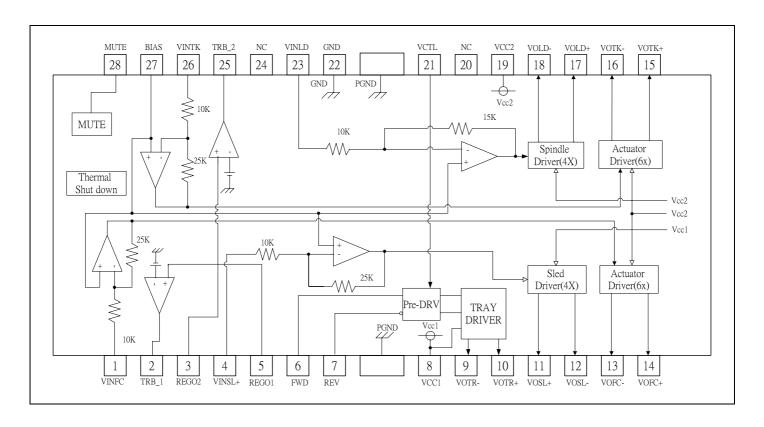

| PACKAGING10              | BLOCK DIAGRAM                | 29  |

| FRONT PANEL CONTROLS11   | ELECTRICAL PARTS LIST (120v) | 30  |

| INFORMATION DISPLAY12    | PCB DRAWINGS                 | 44  |

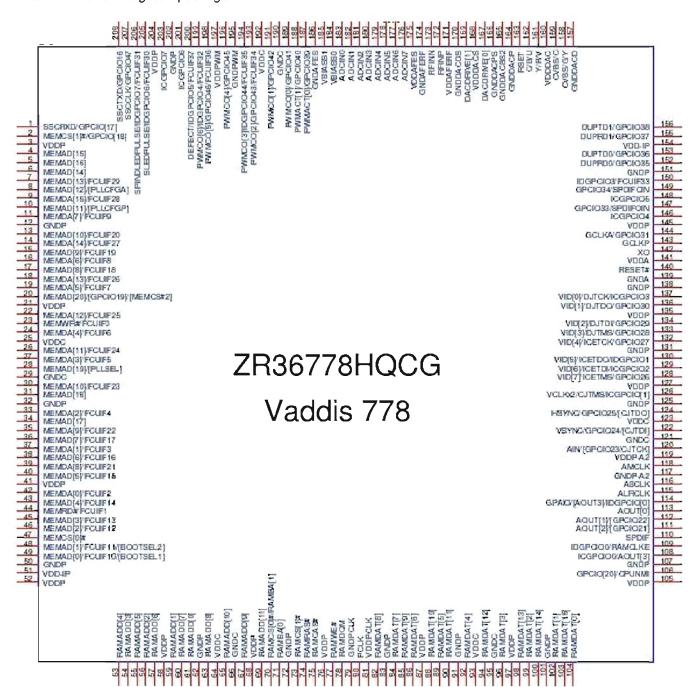

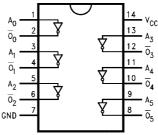

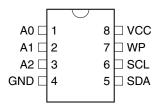

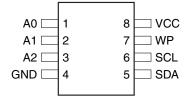

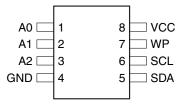

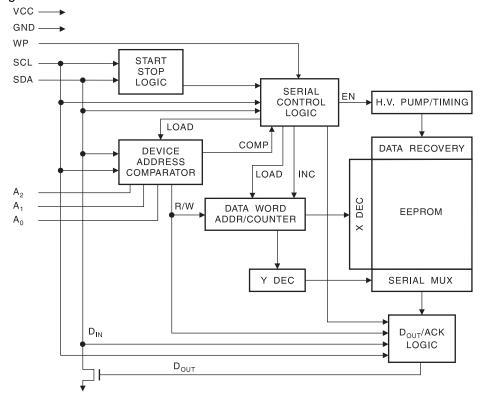

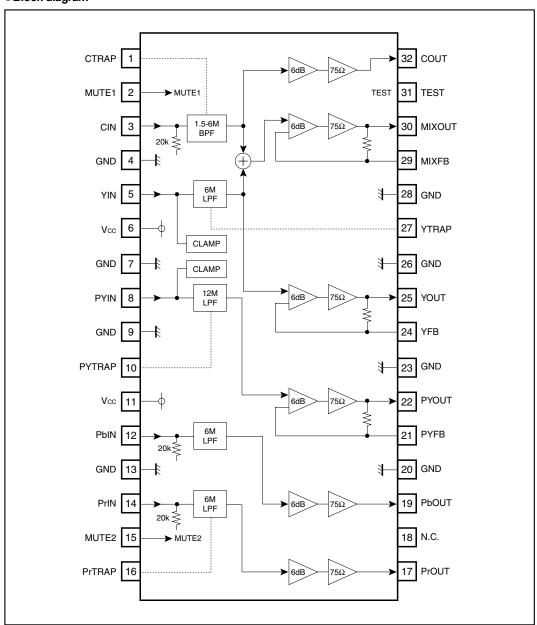

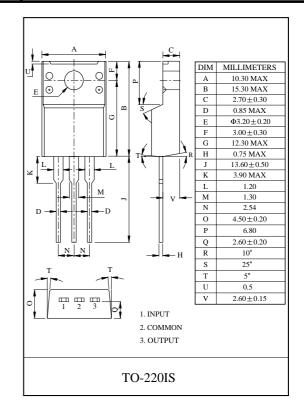

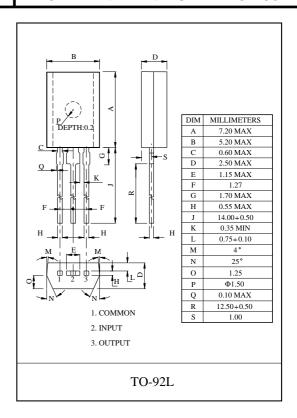

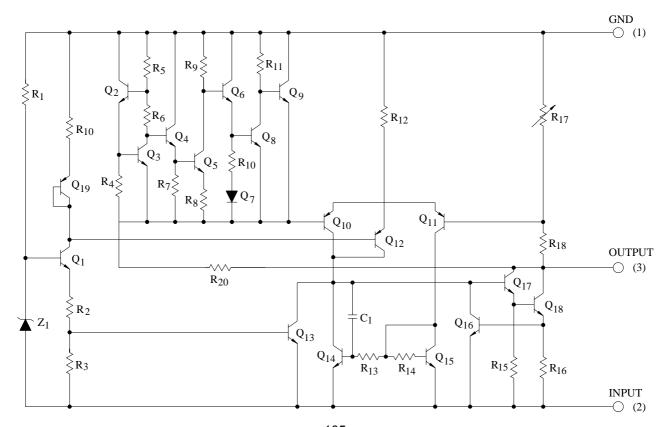

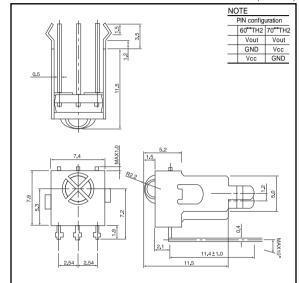

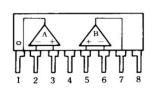

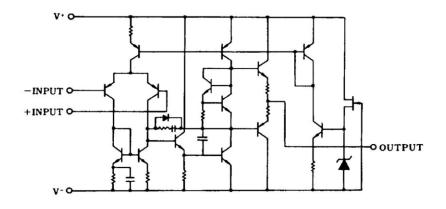

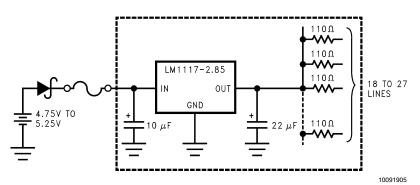

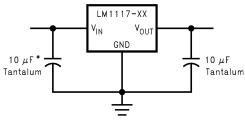

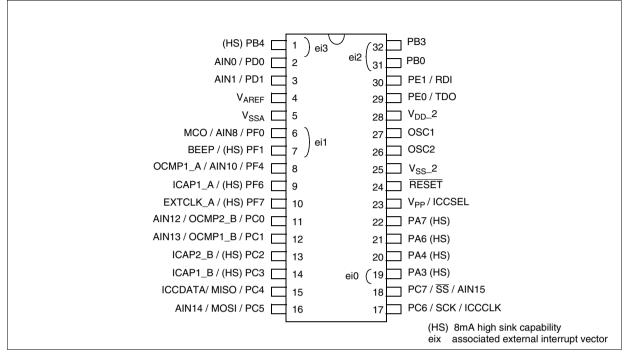

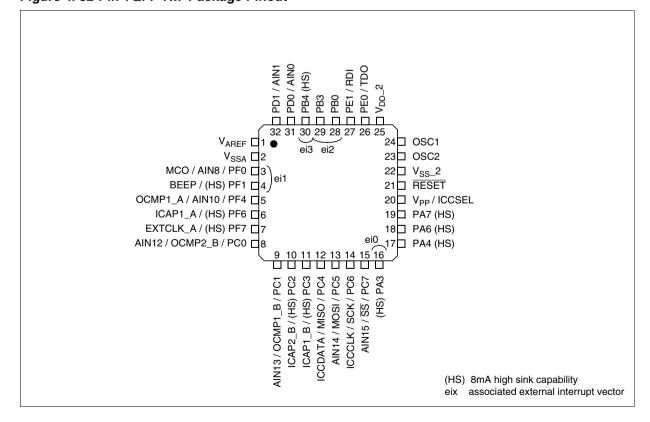

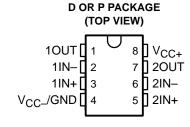

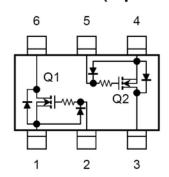

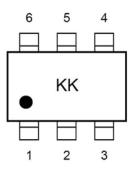

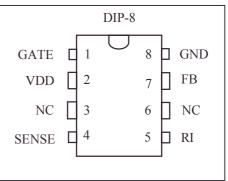

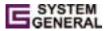

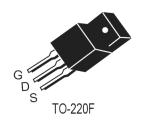

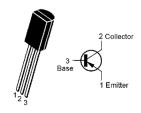

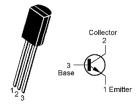

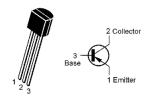

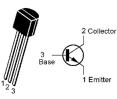

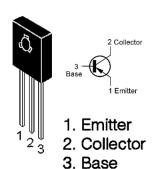

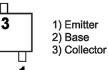

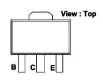

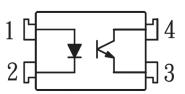

| REMOTE CONTROL13         | SEMICONDUCTOR PINOUTS        | 50  |

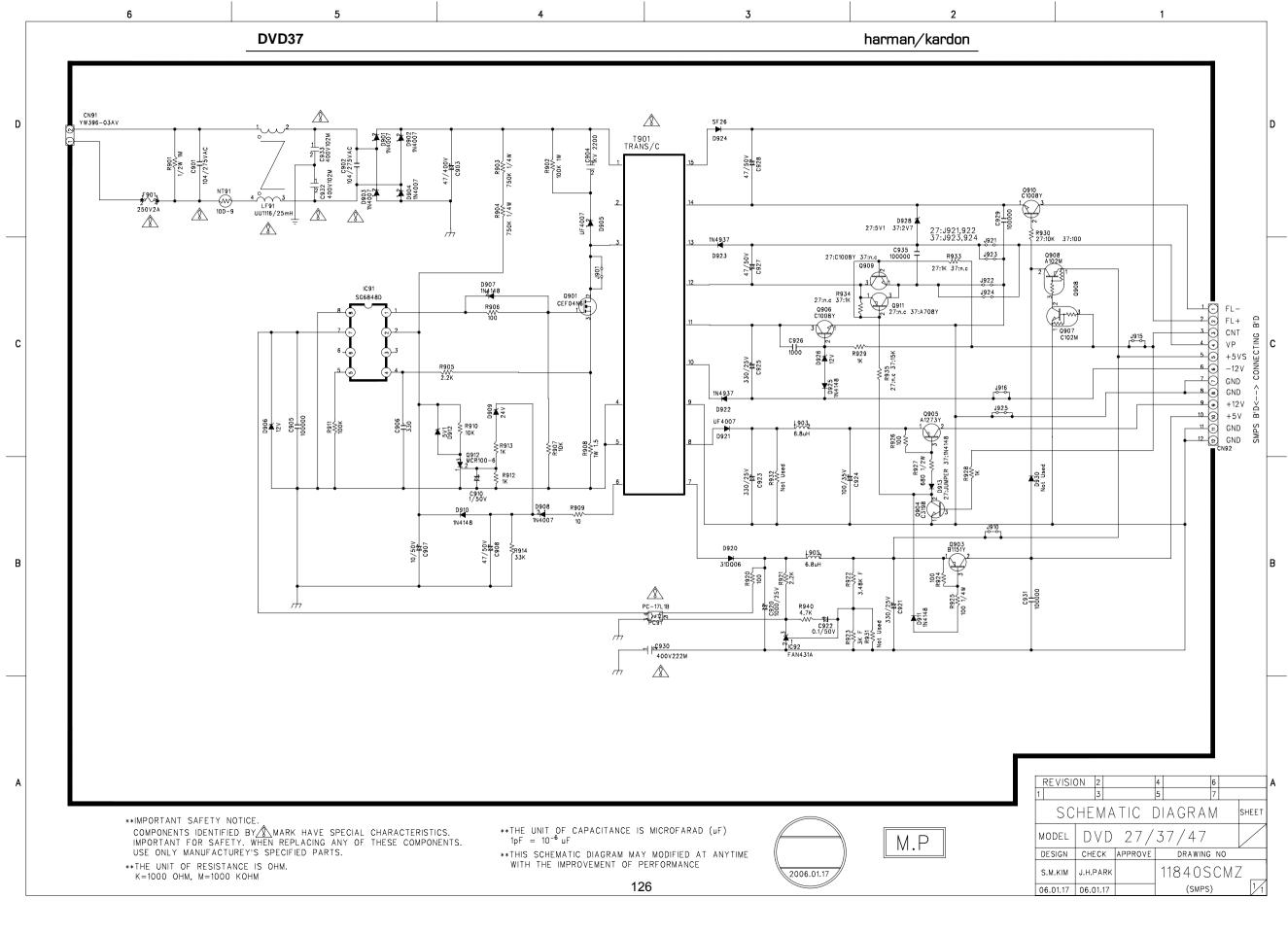

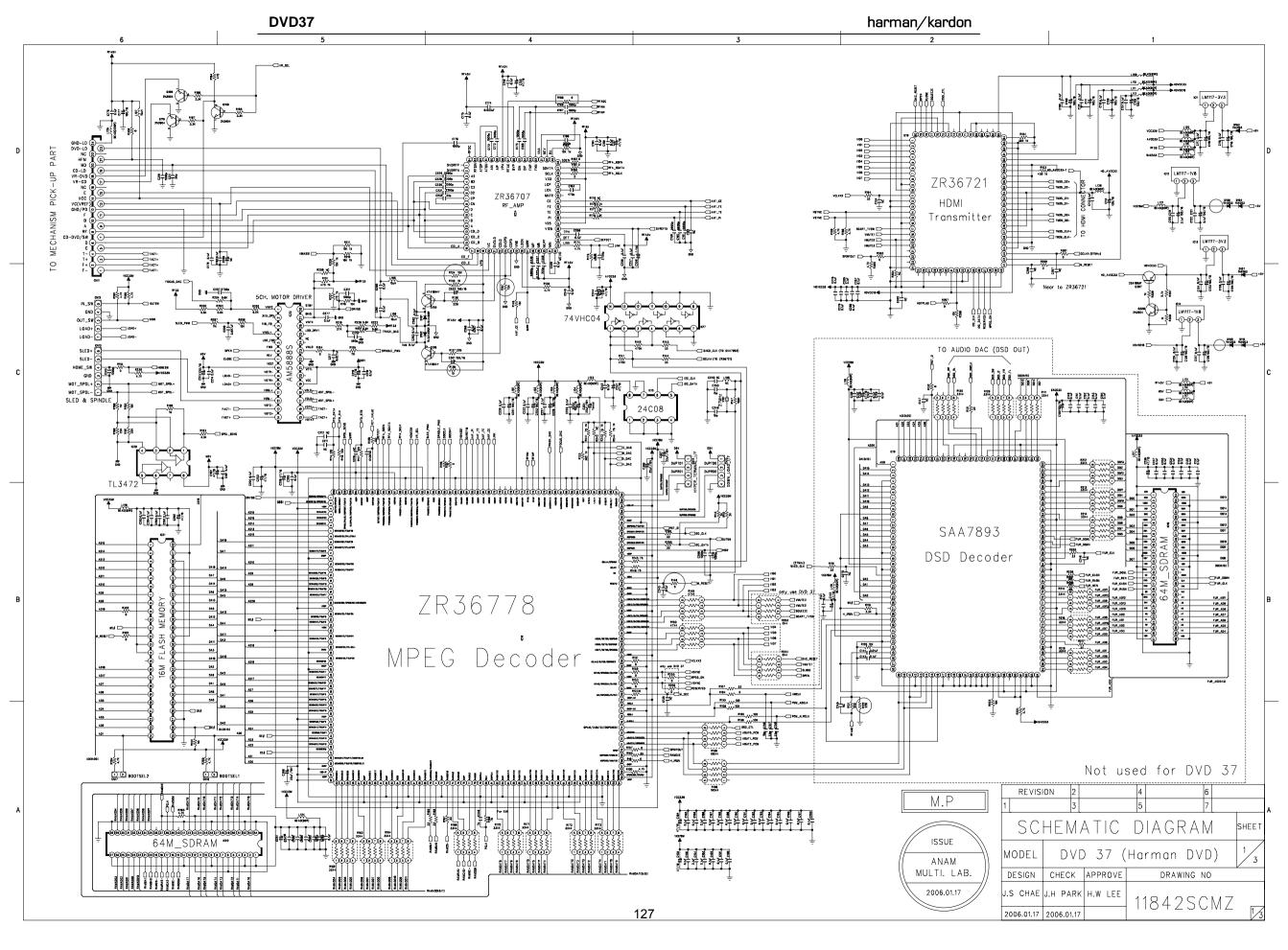

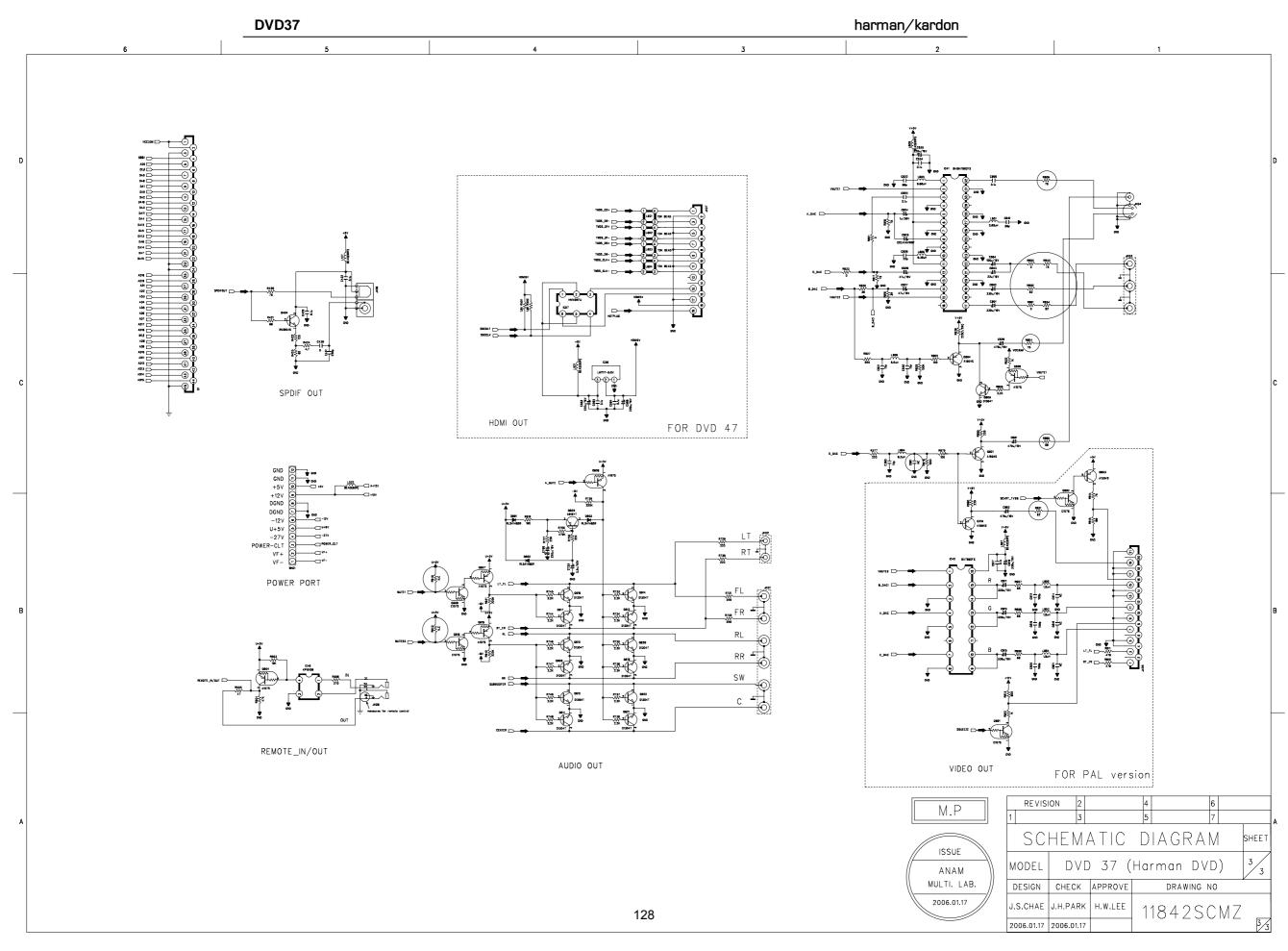

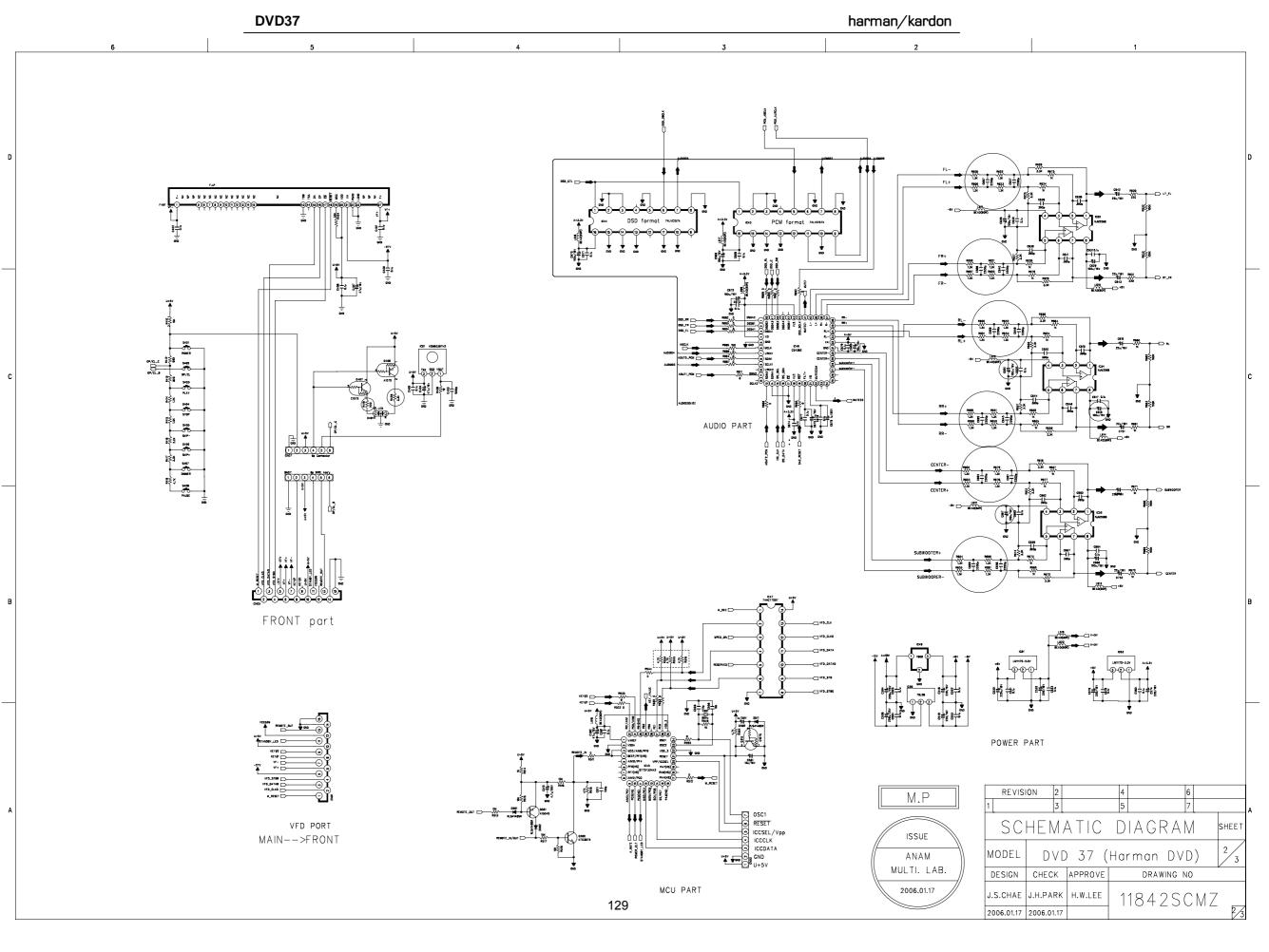

| REAR PANEL CONNECTIONS16 | SCHEMATICS                   | 126 |

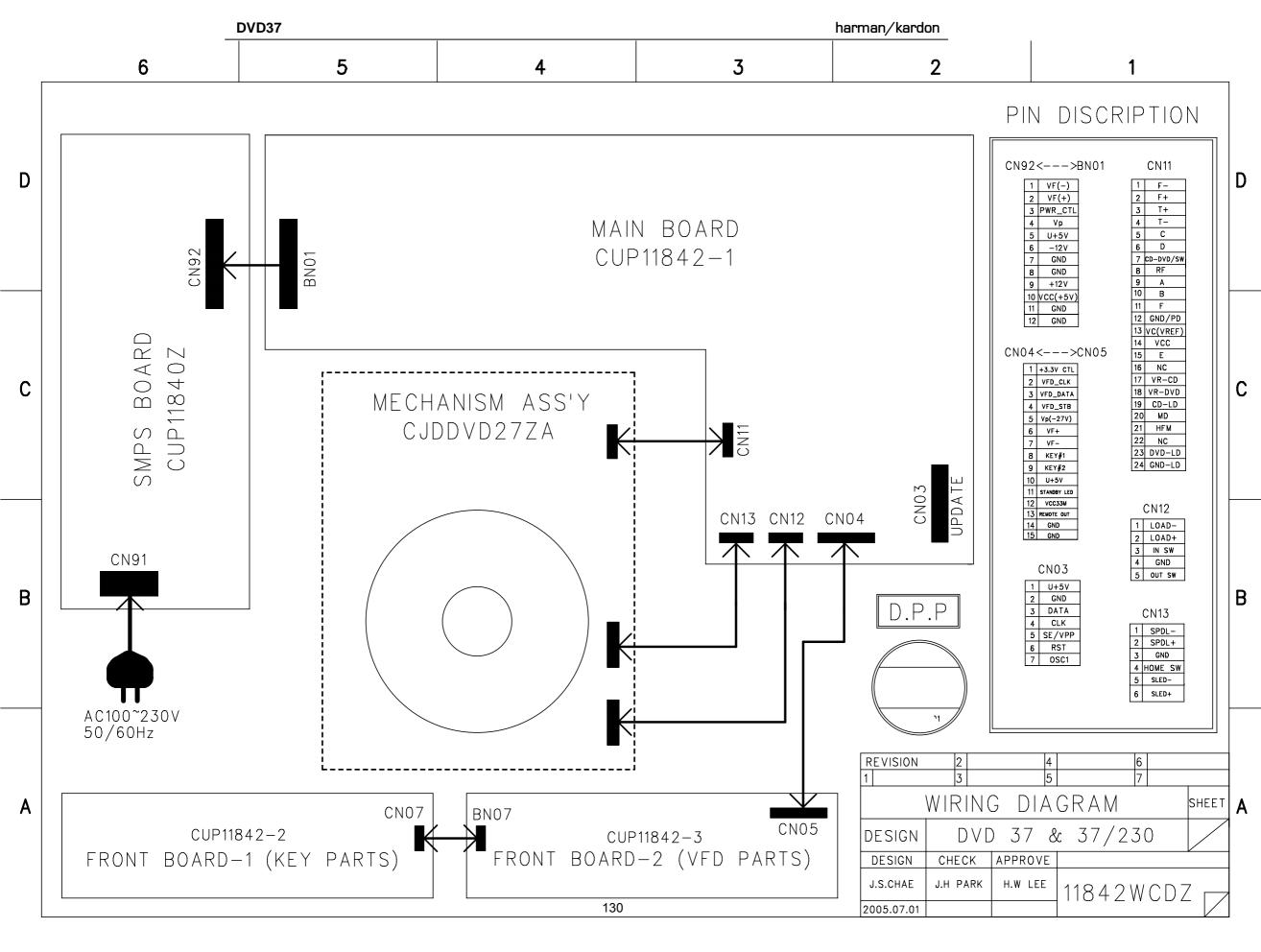

| CONNECTIONS/SETUP17      | WIRING DIAGRAM               | 130 |

| TEST SCREEN 25           |                              |     |

harman/kardon, Inc.

250 Crossways Park Dr.

Woodbury, New York 11797

### SERVICING PRECAUTIONS

### NOTES REGARDING HANDLING OF THE PICK-UP

### 1. Notes for transport and storage

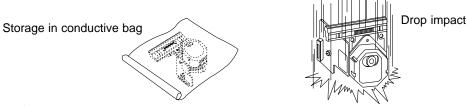

- 1) The pick-up should always be left in its conductive bag until immediately prior to use.

- 2) The pick-up should never be subjected to external pressure or impact.

### 2. Repair notes

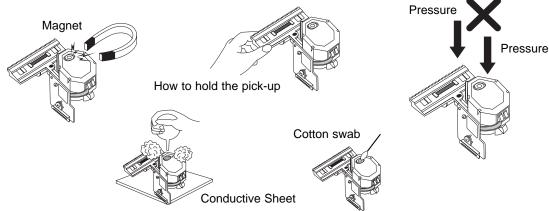

- 1) The pick-up incorporates a strong magnet, and so should never be brought close to magnetic materials.

- 2) The pick-up should always be handled correctly and carefully, taking care to avoid external pressure and impact. If it is subjected to strong pressure or impact, the result may be an operational malfunction and/or damage to the printed-circuit board.

- 3) Each and every pick-up is already individually adjusted to a high degree of precision, and for that reason the adjustment point and installation screws should absolutely never be touched.

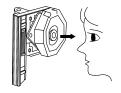

- 4) Laser beams may damage the eyes!

Absolutely never permit laser beams to enter the eyes!

Also NEVER switch ON the power to the laser output part (lens, etc.) of the pick-up if it is damaged.

NEVER look directly at the laser beam, and don't let contact fingers or other exposed skin.

#### 5) Cleaning the lens surface

If there is dust on the lens surface, the dust should be cleaned away by using an air bush (such as used for camera lens). The lens is held by a delicate spring. When cleaning the lens surface, therefore, a cotton swab should be used, taking care not to distort this.

6) Never attempt to disassemble the pick-up.

Spring by excess pressure. If the lens is extremely dirty, apply isopropyl alcohol to the cotton swab. (Do not use any other liquid cleaners, because they will damage the lens.) Take care not to use too much of this alcohol on the swab, and do not allow the alcohol to get inside the pick-up.

### NOTES REGARDING COMPACT DISC PLAYER REPAIRS

#### 1. Preparations

1) Compact disc players incorporate a great many ICs as well as the pick-up (laser diode). These components are sensitive to, and easily affected by, static electricity. If such static electricity is high voltage, components can be damaged, and for that reason components should be handled with care.

2) The pick-up is composed of many optical components and other high-precision components. Care must be taken, therefore, to avoid repair or storage where the temperature of humidity is high, where strong magnetism is present, or where there is excessive dust.

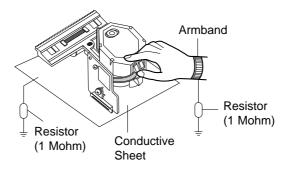

#### 2. Notes for repair

- 1) Before replacing a component part, first disconnect the power supply lead wire from the unit

- 2) All equipment, measuring instruments and tools must be grounded.

- 3) The workbench should be covered with a conductive sheet and grounded.

When removing the laser pick-up from its conductive bag, do not place the pick-up on the bag. (This is because there is the possibility of damage by static electricity.)

- 4) To prevent AC leakage, the metal part of the soldering iron should be grounded.

- 5) Workers should be grounded by an armband (1M $\Omega$ )

- 6) Care should be taken not to permit the laser pick-up to come in contact with clothing, in order to prevent static electricity changes in the clothing to escape from the armband.

- 7) The laser beam from the pick-up should NEVER be directly facing the eyes or bare skin.

### **ESD PRECAUTIONS**

### **Electrostatically Sensitive Devices (ESD)**

Some semiconductor (solid state) devices can be damaged easily by static electricity. Such components commonly are called Electrostatically Sensitive Devices (ESD). Examples of typical ESD devices are integrated circuits and some field-effect transistors and semiconductor chip components. The following techniques should be used to help reduce the incidence of component damage caused by static electricity.

- Immediately before handling any semiconductor component or semiconductor-equipped assembly, drain off

any electrostatic charge on your body by touching a known earth ground. Alternatively, obtain and wear a

commercially available discharging wrist strap device, which should be removed for potential shock reasons

prior to applying power to the unit under test.

- 2. After removing an electrical assembly equipped with ESD devices, place the assembly on a conductive surface such as aluminum foil, to prevent electrostatic charge buildup or exposure of the assembly.

- 3. Use only a grounded-tip soldering iron to solder or unsolder ESD devices.

- 4. Use only an anti-static solder removal device. Some solder removal devices not classified as "anti-static" can generate electrical charges sufficient to damage ESD devices.

- 5. Do not use freon-propelled chemicals. These can generate electrical charges sufficient to damage ESD devices.

- 6. Do not remove a replacement ESD device from its protective package until immediately before you are ready to install it. (Most replacement ESD devices are packaged with leads electrically shorted together by conductive foam, aluminum foil or comparable conductive materials).

- 7. Immediately before removing the protective material from the leads of a replacement ESD device, touch the protective material to the chassis or circuit assembly into which the device will by installed.

# CAUTION: BE SURE NO POWER IS APPLIED TO THE CHASSIS OR CIRCUIT, AND OBSERVE ALL OTHER SAFETY PRECAUTIONS.

8. Minimize bodily motions when handing unpackaged replacement ESD devices. (Otherwise harmless motion such as the brushing together of your clothes fabric or the lifting of your foot from a carpeted floor can generate static electricity sufficient to damage an ESD device).

### DVD 37 TECHNICAL SPECIFICATIONS

Applicable Disc: Disc formats: 5-inch (12cm) or 3-inch (8cm) DVD-Video, DVD-Audio, standard-conforming DVD-R, DVD+R, DVD+RW, DVD+RW,

VCD, CD, CD-R, CD-RW or MP3 discs

Region code: DVD video disc with Code 1 or 0 only

DVD layers: Single side/single layer, single side/dual layer, dual side/dual layer

Audio formats: DVD Audio MLP lossless, linear PCM, MPEG, Windows Media® 9, Dolby® Digital or DTS® audio discs

Still-image format: JPEG

Video Signal System: NTSC

**HDMI™ Output:** Video: 480p, 720p, 1080i

HDMI Version 1.0-compliant HDCP Version 1.1-compliant

Composite Video Output: 1V p-p/75 ohms, sync negative polarity

S-Video Output: Y/luminance: 1V p-p/75 ohms, sync negative polarity

C/chrominance: 0.286 V p-p

Component Video Output: Y: 1V p-p/75 ohms, sync negative polarity

Pr: 0.7V p-p/75 ohms Pb: 0.7V p-p/75 ohms

Analog Audio Output: 2V RMS (1kHz, 0dB)

Frequency Response: DVD (linear PCM): 2Hz - 22kHz +0/-0.5dB (48kHz sampling)

2Hz - 44kHz +0/-1.5dB (96kHz sampling) 2Hz - 88kHz +0/-0.5dB (192kHz sampling)

CD: 2Hz - 20kHz + 0/-0.5dB

Signal/Noise Ratio (SNR): 105dB (A-weighted)

**Dynamic Range:** DVD: 100dB (18-bit)/105dB (20-bit)

CD/DVD: 96dB (16-bit)

THD/1kHz:

DVD/CD: 0.0025%

Wow & Flutter:

Below measurable limits

AC Power:

110–240V AC/50–60Hz

**Power Consumption:** 1 Watt (on/standby)/13 watts (max)

**Dimensions (H x W x D):** 2" x 17-3/10" x 11-1/4" (50mm x 440mm x 285mm)

**Weight:** 6 lb (2.7kg)

Shipping Dimensions (H x W x D): 5" x 14-3/8" x 20" (127mm x 365mmx 508mm)

Shipping Weight: 8.8 lb (4kg)

Depth measurement includes knobs and connectors.

Height measurement includes feet and chassis.

All specifications subject to change without notice.

Harman Kardon and Harman International are trademarks of Harman International Industries, Incorporated, registered in the United States and/or other countries.

Dolby, Pro Logic and the double-D symbol are registered trademarks of Dolby Laboratories. Confidential Unpublished Works.

1992-1997 Dolby Laboratories, Inc. All rights reserved. Manufactured under license from Dolby Laboratories.

DTS and DTS-ES are registered trademarks of DTS, Inc.

Kodak and Photo CD are trademarks of Eastman Kodak Company.

Microsoft, Windows Media, HDCD and High Definition Compatible Digital are registered trademarks of Microsoft Corporation in the United States and/or other countries.

Blu-ray Disc is a trademark of the Blu-ray Disc Association.

HDMI, the HDMI logo and High-Definition Multimedia Interface are trademarks or registered trademarks of HDMI Licensing LLC.

HD-DVD is a trademark of the DVD Format/Logo Licensing Corporation (DVD FLLC).

SACD is a trademark of Sony Corporation.

This product incorporates copyright protection technology that is protected by method claims of certain U.S. patents and other intellectual property rights owned by Macrovision Corporation and other rights owners. Use of this copyright protection technology must be authorized by Macrovision Corporation and is intended for home and other limited viewing uses only unless otherwise authorized by Macrovision Corporation. Reverse engineering or disassembly is prohibited.

MODEL NAME : DVD 37 & DVD 37/230

Description : Characteristics Specification of AUGIO Test Disc : YEDS7 (SONY), TDV-540A (ABEX) Test Conditions :  $10k\Omega$  Load Terminated, AC100V 50/60Hz Test Measuerment : VP-7722A (Audio Analyzer) ,CASCADE SYS-2522(AP)

1 ANALOG ALIDIO OLITPLIT

| 1.ANALOG AUDIO OUT  Measurement                               |         |            | Limit         | Result  | TEST DISC                                         |

|---------------------------------------------------------------|---------|------------|---------------|---------|---------------------------------------------------|

| Output Level[Vrms]                                            |         | L          | $2.0 \pm 0.2$ |         | YEDS7 (SONY)                                      |

|                                                               | R       |            |               | TRACK 1 |                                                   |

|                                                               | Vrms]   |            | < 0.2         |         |                                                   |

| F/response [dB]                                               | 2 0 HZ  | L<br>R     | $0 \pm 1.0$   |         | YEDS7 (SONY)<br>TRACK 2                           |

| Ref.1kHz 0dB                                                  | 100 Hz  | L<br>R     | 0 ± 1.0       |         | YEDS7 (SONY)<br>TRACK 4                           |

|                                                               | 10 KHz  | L<br>R     | 0 ± 1.0       |         | YEDS7 (SONY)<br>TRACK 10                          |

|                                                               | 2 0 KHz | L<br>R     | 0 ± 1.5       |         | YEDS7 (SONY)<br>TRACK 13                          |

|                                                               | 44 KHz  | L<br>R     | 0 ± 1.5       |         | TDV-540A (ABEX) TITLE 4,CHAPTER 16 AUDIO STREAM 3 |

| Emphasis<br>Characteristic[dB]                                | 5 KHz   | L<br>R     | -4.53±1.0     |         | YEDS7 (SONY)<br>TRACK 40                          |

| Ref.1kHz 0dB                                                  | 1 6 KHz | L<br>R     | -9.04 ± 1.0   |         | YEDS7 (SONY)<br>TRACK 41                          |

| S/N [dB]                                                      |         | L          | > 105         |         | YEDS7 (SONY) TRACK 23                             |

| Channel Separation                                            | [dB]    | L→R<br>R→L | > 95          |         | YEDS7 (SONY) TRACK 30,34                          |

| Linearity [dB]<br>-90dB playback                              |         | L          | 89.5±3        |         | YEDS7 (SONY) TRACK 22                             |

| T.H.D [%]                                                     |         | L<br>R     | < 0.01        |         | YEDS7 (SONY)<br>TRACK 1                           |

| Dynamic Range [dB]<br>-60dB playback<br>全高調波歪率 [%]<br>DVD 96k |         | L<br>R     | > 93          |         | YEDS7 (SONY)<br>TRACK 20                          |

|                                                               |         | L<br>R     | < 0.01        |         | TDV-540A (ABEX)<br>TITLE 3, CHAPTER 1             |

| Dynamic Range [dB] D V D 9 6 k                                |         | L          | > 9 5         |         | TDV-540A (ABEX) TITLE 3, CHAPTER 2                |

| 全高調波歪率 [%]<br>DVD 48k                                         |         | L          | < 0.01        |         | TITLE 2, CHAPTER 1                                |

|                                                               | B]      | L<br>R     | > 95          |         | AUVISAGREAM 2<br>TITLE 2, CHAPTER 2               |

#### 2. DIGITAL OUTPUT

1) OPTICAL OUT

| JITTER | 44.1kHz<br>(mUI) | < 50mUl | Normal 44.1kHz<br>CD Playback |

|--------|------------------|---------|-------------------------------|

| JITTER | 96kHz<br>(mUI)   | < 50mUl | Normal 96kHz<br>DVD Playback  |

2) COAXIAL OUT

| OUTPUT Level [mV]              | / | 500±50 (mV) | Normal CD or DVD |

|--------------------------------|---|-------------|------------------|

| Peak to Peak Level at 75ohm Lo |   | 500±50 (mV) | Playback         |

MODEL NAME : DVD 37& DVD 37/230

Description : Characteristics Specification of Video

Test Disc : TDV-540A (ABEX) , MDVD-111 (TEAC) Serial NO.:

Test Conditions :  $75\Omega$  Load Terminated

AC Input : For USA (120V/60Hz) , For Europe (230V/50Hz)

Test Measuerment: VM-700T

### 4. Video Frequency Respoens (75Ω Terminated)

| Measurement Item |          |          | Limit          | Result | Test Disc        |

|------------------|----------|----------|----------------|--------|------------------|

|                  | 0.5MHz ( | OdB Ref. | 0              |        |                  |

|                  | 1MHz     |          | $0dB \pm 2dB$  |        | MDVD-111         |

| Composite [dB]   | 2MHz     |          | $0dB \pm 2dB$  |        | TITLE2,CHAPTER9  |

|                  | 3MHz     |          | $0dB \pm 2dB$  |        | •                |

|                  | 4MHz     |          | $0dB \pm 2dB$  |        | 100% Multi Brust |

|                  | 5.8MHz   |          | $-3dB \pm 2dB$ |        |                  |

| Measurer       | nent Item      | Limit          | Result | Test Disc        |

|----------------|----------------|----------------|--------|------------------|

|                | 0.5MHz 0dB Ref | . 0            |        |                  |

|                | 1MHz           | $0dB \pm 2dB$  |        | MDVD-111         |

| S-Video Y [dB] | 2MHz           | $0dB \pm 2dB$  |        | TITLE2,CHAPTER9  |

|                | 3MHz           | $0dB \pm 2dB$  |        | ,                |

|                | 4MHz           | $0dB \pm 2dB$  |        | 100% Multi Brust |

|                | 5.8MHz         | $-3dB \pm 2dB$ |        |                  |

| Measurer                             | nent Item       | Limit         | Result | Test Disc        |

|--------------------------------------|-----------------|---------------|--------|------------------|

|                                      | 0.5MHz 0dB Ref. | 0             |        |                  |

| Component Y<br>[dB]<br>Interace Mode | 1MHz            | $0dB \pm 2dB$ |        | MDVD-111         |

|                                      | 2MHz            | $0dB \pm 2dB$ |        | TITLE2,CHAPTER9  |

|                                      | 3MHz            | $0dB \pm 2dB$ |        | ,                |

|                                      | 4MHz            | $0dB \pm 2dB$ |        | 100% Multi Brust |

|                                      | 5.8MHz          | -3dB ± 2dB    |        |                  |

MODEL NAME : DVD 37& DVD 37/230

Description : Characteristics Specification of Video

Test Disc : TDV-540A (ABEX) , MDVD-111 (TEAC) Serial NO.:

Test Conditions :  $75\Omega$  Load Terminated

AC Input : For USA (120V/60Hz) , For Europe (230V/50Hz)

Test Measuerment: VM-700T

### 1. Video Level Test (75Ω Terminated)

| Measurement Item |              | Limit                             | Result | Test Disc       |  |  |  |

|------------------|--------------|-----------------------------------|--------|-----------------|--|--|--|

|                  | Composite    | $1.0V \pm 0.1V$                   |        |                 |  |  |  |

|                  | S-Video Y    | $1.0V \pm 0.1V$                   |        |                 |  |  |  |

|                  | S-Video C    | $286\text{mV} \pm 30\text{mV}$    |        |                 |  |  |  |

| Video output [V] | Component Y  | $1.0V \pm 0.1V$                   |        | MDVD-111        |  |  |  |

|                  | Component Pb | 700mV ± 100mV                     |        | TITLE2,CHAPTER1 |  |  |  |

| Video output [V] | Component Pr | 700mV ± 100mV                     |        | ,               |  |  |  |

|                  | Scart CVBS   | $1.0V \pm 0.15V$                  |        | 100% COLOR BAR  |  |  |  |

|                  | Scart Red    | 700mV ± 100mV                     |        |                 |  |  |  |

|                  | Scart Green  | $700 \text{mV} \pm 100 \text{mV}$ |        |                 |  |  |  |

|                  | Scart Blue   | 700mV ± 100mV                     | _      |                 |  |  |  |

<sup>\*\*</sup> Pb/Pr & RGB Video Level check before please setting the Black Level off in the set-up menu \*\*

### 2. Video S/N Raito Test (75Ω Terminated)

| Measurement Item |              | Limit     | Result | Test Disc        |

|------------------|--------------|-----------|--------|------------------|

|                  | Composite    | ≥ 65.0 dB |        |                  |

| Video SNR [dB]   | S-Video Y    | ≥ 65.0 dB |        | MDVD-111         |

| 100KHz~4.2MHz    | Component Y  | ≥ 65.0 dB |        | TITLE2,CHAPTER 4 |

| Use SC Trap      | Component Pb | ≥ 65.0 dB |        | 50% Gray Color   |

| ·                | Component Pr | ≥ 65.0 dB |        | 5                |

#### 3. Chroma Signal AM.PM Test (75Ω Terminated)

|                             | ment Item        | Limit     | Result | Test Disc        |

|-----------------------------|------------------|-----------|--------|------------------|

| Chroma AM [dB]              | Composite Chroma | ≥ 65.0 dB |        | TDV-540A         |

| 10KHz~500KHz S-Video Chroma |                  | ≥ 65.0 dB |        | TITLE2,CHAPTER17 |

|                             |                  |           |        |                  |

| Chroma PM [dB]              | Composite Chroma | ≥ 60.0 dB |        | 100% Magenta     |

| 10KHz~500KHz                | S-Video Chroma   | ≥ 60.0 dB |        | Color            |

### 2. DVD-Audio Part (Test Disc V-612, JVC)

| 2. DVD National (Test Disc v 012; 6 v c) |          |                     |             |       |         |    |    |             |    |   |     |

|------------------------------------------|----------|---------------------|-------------|-------|---------|----|----|-------------|----|---|-----|

|                                          |          | Trook Inform        | Limit       | Downm | nix 2CH |    | N  | ∕luiti 5 Ch | +  |   | SW  |

|                                          |          | Track Inform.       | LITTIL      | LT    | RT      | FL | FR | SL          | SR | С | 200 |

| Output Level                             | (V)      | Tr.38 1KHz 0dB      | 2.1±0.2Vrms |       |         |    |    |             |    |   |     |

| T.H.D (%) 20KH                           | tz LPF   | Tr.38 1KHz 0dB      | ↓0.01%      |       |         |    |    |             |    |   |     |

|                                          |          | Tr.59 17Hz          | 0±1.0dB     |       |         |    |    |             |    |   |     |

|                                          | 48 / 24  | Tr.54 10KHz         | 0±1.0dB     |       |         |    |    |             |    |   |     |

|                                          |          | Tr.53 20KHz         | 0±2.0dB     |       |         |    |    |             |    |   |     |

| Frequency                                |          | Tr.49 17Hz          | 0±1.0dB     |       |         |    |    |             |    |   |     |

| Respones (dB)                            | 96 / 20  | Tr.45 10KHz         | 0±1.0dB     |       |         |    |    |             |    |   |     |

| Ref.: Tr. 38                             |          | Tr.44 20KHz         | 0±2.0dB     |       |         |    |    |             |    |   |     |

|                                          |          | Tr.22 17Hz          | 0±1.0dB     |       |         |    |    |             |    |   |     |

|                                          | 192 / 24 | Tr.18 10KHz         | 0±1.0dB     |       |         |    |    |             |    |   |     |

|                                          |          | Tr.17 20KHz         | 0±2.0dB     |       |         |    |    |             |    |   |     |

| S/N (dB) "A" Filter                      |          | Tr.40 Infinity Zero | ↑90dB       |       |         |    |    |             |    |   |     |

| Dynamic Range<br>20KHz LPI               |          | Tr.39 -60dB         | ↑85dB       |       |         |    |    |             |    |   |     |

- ★ SW Level & THD --> Track 38 (30Hz) Play.

- ★ SW Frequency Respones -> Track 55(31Hz, 0dB) Reference

- ★ Track 54 (61Hz), Track 53 (81Hz), Track 51(127Hz) Play

DVD37

## Instruction manual ass'y - Accessories

| NO | DESCRIPTION              | PARTS NO.  | Q, ty |

|----|--------------------------|------------|-------|

| 1  | POLY BAG                 |            | 1     |

| 2  | CARD WARRANTY            | CQE1A172X  | 1     |

| 3  | HARMAN IMAGE BROCHURES   |            | 1     |

| 4  | SHEET, IMPORTANT         |            | 1     |

| 5  | INSTRUCTION MANUAL       | CQX1A1049Z | 1     |

| 6  | BATTERY                  |            | 2     |

| 7  | CORD, PIN(3P, W/R/Y)     | CJS4S004Z  | 1     |

| 8  | CABLE, S-VHS (1.5M)      | CJS01006Z  | 1     |

| 9  | CORD, JACK (MONO) 1200MM | CJS9D002Z  | 1     |

| 10 |                          |            |       |

| 11 | CABLE, HDMI (2M)         | CJS8T001Z  | 1     |

| 12 | STAPLE                   |            | 3     |

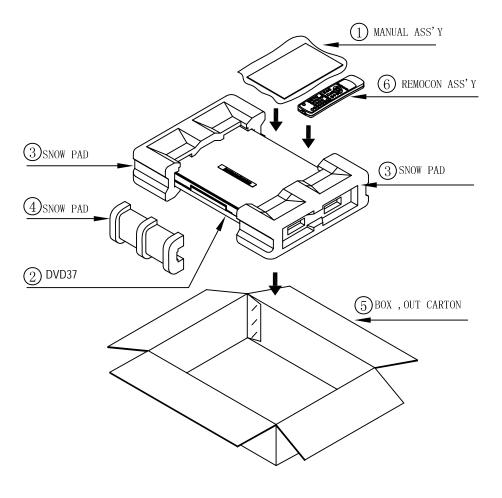

## Package Drawing

| NO | DESCRIPTION   | PARTS NO.  | Q, ty |

|----|---------------|------------|-------|

| 1  | MANUAL ASS'Y  |            | 1     |

| 2  | DVD 37        | DVD 37     | 1     |

| 3  | SNOW, PAD     | CPS1A714   | 2     |

| 4  | SNOW, PAD     | CPS1A715   | 1     |

| 5  | OUTER CARTON  | CPG1A798Y  | 1     |

| 6  | REMOCON ASS'Y | CARTDVD37A | 1     |

| 7  |               |            |       |

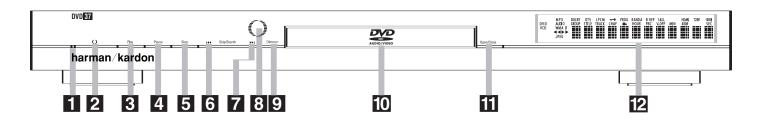

### FRONT-PANEL CONTROLS

**NOTE:** To make it easier to follow the instructions that refer to the controls and connectors in this illustration, a larger copy may be downloaded from the Product Support section for this product at www.harmankardon.com.

- 1 Power Indicator

- 2 Power On/Off (Standby)

- 3 Play

- 4 Pause

- Power Indicator: This indicator lights amber when the unit is connected to an AC power source, but is not turned on. When the unit is on, the indicator lights blue.

- **2** Power On/Off (Standby): Press the button once to turn the DVD 37 on. Press it again to put the unit in the Standby mode.

- 3 Play: Press to initiate playback or to resume playback after the Pause Button 4 22 has been pressed

- 4 Pause: Press this button to momentarily pause playback. To resume playback, press the button again. If a DVD is playing, action will freeze and a still picture will be displayed when the button is pressed.

- **5 Stop:** Press this button once to place the disc in the Resume mode, which means that playback will stop, but as long as the tray is not opened or the disc changed, playback will continue from the same point on the disc when the **Play Button 3 2** is pressed again. Resume will also work if the unit was turned off. Resume will not operate for WMA files or VCDs that do not have playback control. To stop a disc and have play start from the beginning, press the button twice.

- 5 Stop

- 6 Skip/Search Reverse

- 7 Skip/Search Forward

- 8 Remote Sensor

- **6** Skip/Search Reverse: Press this button once to return to the start of the current chapter for a DVD or track for a CD. Subsequent individual presses will skip backwards through the available chapters or tracks. Press and hold the button to play the disc in the fast reverse mode at the speed indicated in the on-screen display and by the **Playback Mode Indicators** .

- **7** Skip/Search Forward: Press this button once to move to the start of the next chapter for a DVD or track for a CD. Subsequent presses will skip forward through the available chapters or tracks. Press and hold the button to play the disc in the Fast Play mode at the speed indicated in the on-screen display and by the **Playback Mode Indicators ○**.

- Remote Sensor: The sensor that receives commands from the remote control is behind the front panel in this area. To ensure proper operation of the player with the remote, it is important that this area not be covered. In the event that the player is enclosed in a cabinet or if the remote sensor is covered, you may extend the remote sensor by connecting an optional, external remote sensor to the **Remote Control Input**

- ② on the rear panel (see page 14). When optional, external IR "blasters" are used for system control, they should be positioned so that they point at this area.

- 9 Display Dimmer

- 10 Disc Drawer

- 111 Open/Close

- 12 Information Display

- g Display Dimmer: Press this button to reduce the brightness of the Information Display 12 by 50% or to turn the display off completely in the following order: FULL BRIGHTNESS → HALF BRIGHTNESS → OFF → FULL BRIGHTNESS.

- discs played in the unit. Be certain to seat all discs carefully within the recess in the drawer. Do not press down on the drawer when it is open, to avoid damage to the player. When the drawer is left open with no activity for 5 minutes, it will automatically close to prevent dust or dirt from entering the component, and to prevent accidental damage. If a disc is present, the DVD 37 will immediately begin playback.

- Open/Close: Press this button to open or close the disc tray.

- [2] Information Display: The Information Display provides status information on the player and the disc being played through a series of specific indicators and messages that appear in the display. See page 10 for more information on the display.

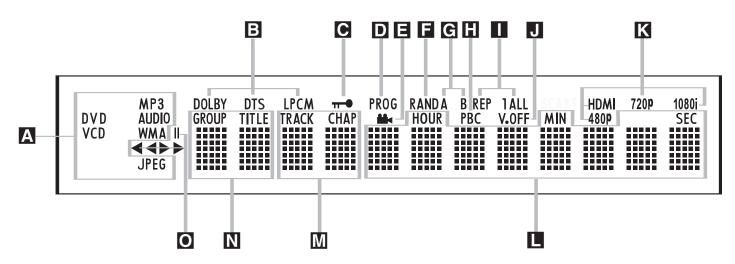

### FRONT-PANEL INFORMATION DISPLAY

**NOTE:** To make it easier to follow the instructions that refer to the controls and connectors in this illustration, a larger copy may be downloaded from the Product Support section for this product at www.harmankardon.com.

- A Disc-Type Indicators

- **B** Audio Bitstream Indicators

- C Parental Lock Indicator

- **D** Program Indicator

- **■** Angle Indicator

- A Disc Type Indicators: The DVD, DVD-Audio, CD, VCD, MP3, WMA or JPEG indicator will light to show the type of disc currently being played.

NOTE: The DVD 37 does not have an HDCD® (High Definition Compact Digital®) decoder. Therefore, to benefit from HDCD encoding, make sure to connect one of the DVD 37's Digital Audio Outputs 45 to your receiver or processor with HDCD encoding. If your receiver or processor does not have HDCD decoding, you may still enjoy conventional CD playback of the disc.

- Audio Bitstream Indicators: When a Dolby® Digital, DTS® or linear PCM digital audio signal is present on the disc, one of these indicators will light. DVD-Audio, MP3 and WMA bitstreams will be indicated by the Disc Type Indicator 🔼.

- Parental Lock Indicator: This indicator lights in red when the parental-lock system is engaged in order to prevent anyone from changing the rating level without a code.

- Program Indicator: This indicator lights when a playlist has been programmed using the menu system (available for CDs only). See page 36 for more information on programming playlists.

- Angle Indicator: This indicator blinks when alternative viewing angles are available on the DVD currently playing.

- Random Indicator

- G A-B Repeat Indicator

- H VCD Playback Control Indicator

- Repeat Indicators

- J V-OFF Indicator

- **Random Indicator:** This indicator lights when the unit is in the Random Play mode.

- **G** A-B Repeat Indicator: This indicator lights when a specific passage for repeat playback has been selected.

- Repeat Indicators: These indicators light when any of the Repeat functions are in use.

- V-OFF Indicator: This indicator lights in red when the unit's video output has been turned off by pressing the V-OFF Button on the remote control.

- Video Output Indicators: When the DVD 37 is connected to a video display using the HDMI Output

- (3), the display sends information to the DVD 37 indicating the highest video resolution it is capable of handling, and the DVD 37 automatically sets the video output to match it. That resolution is displayed here. You may use the HD Mode Selector (13) to manually select a lower video output resolution.

- Time Indicators: These positions in the display will show the running time of a disc in play.

NOTE: The indicators MMM will also display text messages about the DVD's status, including LOADING when a disc is loading, POWER OFF when the unit is turned off, and DISC ERROR when a disc not compatible with the DVD is put into the play position.

- K Video Indicators

- Time Indicators

- M Chapter/Track Number Indicators

- N Group/Title Indicators

- Playback-Mode Indicator

- M Chapter/Track Number Indicators: When a DVD disc is playing, these two positions in the display will show the current chapter. When a DVD-Audio or CD disc is playing they will show the current track number.

- M Group/Title Indicators: These two positions in the display will show the current title number when a DVD disc is playing, or the current group for a DVD-Audio disc.

- Playback-Mode Indicators: These indicators light to show the current playback mode:

- ▶ Lights when a disc is playing in the normal mode. This indicator will flash when the disc is in Forward Slow Play mode. The on-screen banner display indicates the selected speed (1/2, 1/4, 1/8 or 1/16).

- ▶▶ When the DVD 37 is in the Fast Search play mode, two of these indicators will light to show that the unit is in a Fast Play mode. The on-screen banner display indicates the selected speed (x2, x4, x8, x20 or x100). Fast Play mode is not available for WMA files.

- Lights when the disc is paused.

- ◄ Flashes when the disc is in Reverse Slow Play mode. The on-screen banner display indicates the selected speed (1/2 or 1/4).

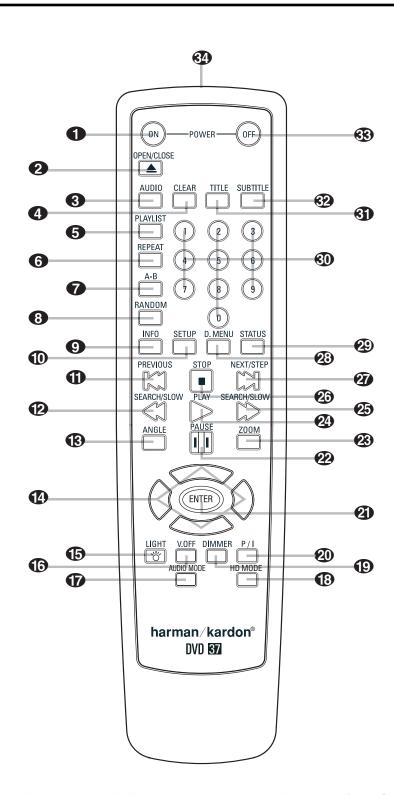

## REMOTE CONTROL FUNCTIONS

- Power On

- 2 Open/Close

- 3 Audio Select

- Clear

- Playlist

- Repeat

- **7** A-B Repeat

- Random

- Info

- Setup

- Previous Step/Skip

- Search/Slow Reverse

- Angle

- **⚠ △/▼/◄/▶** Navigation Buttons

- 1 Light

- Wideo Off

- Audio Mode Selector

- 18 HD Mode Selector

- Dimmer

- 20 Progressive Scan/Interlaced

- **2** Enter

- Pause

- Zoom

- 2 Play

- 25 Search/Slow Forward

- Stop

- Next Step/Skip

- 28 Disc Menu

- Status

- Numeric Keys

- 31 Title

- 3 Subtitle

- 3 Power Off

- 34 IR Emitter

**NOTE:** To make it easier to follow the instructions that refer to the controls and connectors in this illustration, a larger copy may be downloaded from the Product Support section for this product at www.harmankardon.com.

### REMOTE CONTROL FUNCTIONS

- Power On: Turns on the player when it is in Standby mode (Harman Kardon logo appears on screen).

- **2 Open/Close:** Press to open or close the disc tray.

- **3** Audio Select: Press to access various audio languages on a DVD (if the DVD contains multiple audio streams). This button may also allow you to access other audio formats on DVD discs, such as linear PCM or Dolby Digital 5.1 tracks (or other formats), if they've been recorded on the disc.

- Q Clear: Press this button to remove on-screen menus or banners from the display screen. Press this button to clear the current play order displayed next to a track while programming a playlist. In Stop mode and with all menus and banners removed from the display, press and hold this button for five seconds to reset all settings to their factory defaults.

- Playlist: Press this button to access the Playlist on-screen menu, which enables you to change the order in which tracks are played on a CD or DVD-Audio disc. (See page 36 for more information on creating and playing playlists.)

- Repeat: Each press of this button changes the playback mode to repeat a chapter or track or the entire disc. A repeat icon will appear in the upper right corner of the screen indicating the current repeat mode. If the Player Information Screen is active, the changes will be displayed on screen.

- **A-B Repeat:** Press this button to enter the starting point of a section on a disc you wish to repeat. The second press enters the end of the selection to be repeated. Once the "A" (start) and "B" (end) points have been entered the player will repeat the selection until the **Play Button 23** 3 is pressed or the disc is stopped. If the Player Information Screen is active, the changes will be displayed on screen.

- **3** Random: Each press of this button starts or stops playback in random order. The Random function is only available when playing CDs, but not when a Playlist is active (the Player Information screen indicates Programmed Order on the Playlist line).

- **(9)** Info: Press once to access the Player Information menu for information on the current disc and the playback mode settings. Press again to remove information from screen. See page 28 for more information on the Player Information menu.

- **(1)** Setup: Press this button to use the DVD 37's on-screen menu system to adjust the player's configuration settings. Note that the **Info Button (9)** must be pressed to access the DVD 37's Player Information menu to obtain detailed disc information, and to configure the playback mode of the disc.

- **(1) Previous Step/Skip:** Press this button once to skip back to the beginning of the current chapter on a DVD or track on a CD or DVD-Audio disc. Press it again to continue to skip back through the previous

- chapters or tracks. After first pressing the **Pause Button 22**, press this button to step backwards through a DVD or VCD as a series of still-image frames.

- ② Search/Slow Reverse: This button initiates fast or slow play in the reverse mode. For fast reverse play, each press of the button when playing DVD or VCD discs changes the speed as indicated by the number appearing in the upper right corner of the screen. For slow reverse play, first press the Pause Button ② and each subsequent press of this button will change the slow play speed as indicated by the number appearing in the upper right corner of the screen.

- (3) Angle: Press this button to change the camera angle on discs programmed for multiple-angle views. When a JPEG is being displayed, pressing the Angle Button (3) repeatedly causes the on-screen image to rotate clockwise by 90 degrees each press. The current orientation in degrees will be displayed in the upper right corner of the screen.

- ⚠ ▲ Navigation Buttons: Use to move the cursor in the on-screen menu system.

- **(5)** Light: Press to illuminate the buttons on the remote controller.

- **(iii)** Video Off: Press this button to turn off the video output for improved audio performance when playing discs. Press it again to view the on-screen menus. It is highly recommended that you use this function to prevent "burn-in" of your plasma video display.

- Audio Mode Selector: This button adjusts the Bass Management setting, which is also found in the AUDIO SETUP menu (see page 22). Stop playback of the current disc in order to use this selector. There are three available settings: Bypass (the default), On and Stereo. The first press displays the current setting, and each additional press cycles through the three settings.

- In Bypass mode, the analog audio information is passed through the **Analog Audio Outputs (9)** as is, without any bass management adjustments being applied. This mode is used with receivers and processors that are capable of applying bass management settings (speaker size, output levels and delay times) to their 6-channel analog inputs.

The On setting is used with receivers and processors that pass the audio signals from their 6-channel analog inputs directly to the outputs without applying any bass management settings. With bass management on, it is recommended that you use the AUDIO ADJUSTMENTS submenu to set the DVD 37's bass management settings. See page 22.

- NOTE: The 2-channel downmix (Stereo mode) and the 5.1-channel presentation of multichannel audio discs (Bypass or Bass Management On modes) are not available simultaneously. With bass management on, the same front left and right channel information will be available at both of the left and right Analog Audio Outputs ①. No surround information will be present in the signal output at the 2-channel Analog Audio Outputs ②. In Stereo mode only, the downmixed 2-channel signal will be available at both Analog Audio Outputs ②. Use the Audio Mode Selector ① to toggle through the three available settings.

- 13 HD Mode Selector: When the DVD 37 is connected to a video display using the **HDMI Output 3**, the display sends information to the DVD 37 indicating the highest video resolution it is capable of handling, and the DVD 37 automatically sets the video output to match it. Pressing this button allows you to manually change the output resolution, with your selection indicated by the Video Output Indicators K. The DVD 37 will not allow you to select a resolution beyond the capabilities of your display, and if you try to do so, an on-screen error message will appear to alert you to the selection of an incompatible video format. Changes made with this button remain active until the DVD 37 or the display is turned off. When either is turned off, and then on again, the DVD 37 will revert to the default setting transmitted by the display.

- **(D)** Dimmer: Press to change the brightness of the front panel display or to turn the display off completely in the following order: FULL BRIGHTNESS → HALF BRIGHTNESS → OFF → FULL BRIGHTNESS

- ② Progressive Scan/Interlaced Button: Each press of this button selects between the progressive scan and interlaced modes for the Component Video Outputs ③. This button has no effect while the Setup menu system is active, indicated by ¬SETUP¬ appearing in the Information Display 12. Press the Setup Button ① to clear the Setup menu, and then press this button to toggle between the progressive scan and interlaced component video settings.

- **2)** Enter: Press this button to enter a setting in the DVD 37 menu system or to confirm a menu selection choice in a disc's on-screen menu.

- **22 Pause:** Press this button to pause the disc and freeze the picture during DVD or VCD playback, or to pause the playback of a CD or DVD-Audio disc. To play a DVD or VCD in the slow-forward or reverse mode, first press this button and then press either the **Search/Slow Forward 25** or **Reverse Button 12**.

- **23** Zoom: Press this button to zoom in on the image from a DVD, VCD or JPEG image. The image may be expanded by a factor of x2, x3, x4 or x5. Once the on-screen indication of the zoom ratio disappears from the screen you may use the **Navigation Buttons 1** to explore the picture.

### REMOTE CONTROL FUNCTIONS

- Play: Press this button to begin the playback of a disc, or to resume normal playback when a disc has been paused or scanned.

- Search/Slow Forward: This button initiates fast or slow play in the forward mode. For fast forward play, each press of the button when playing DVD or VCD discs changes the speed as indicated by the number appearing in the upper right corner of the screen. For slow forward play, first press the Pause Button 2 and each subsequent press of this button will change the slow play speed as indicated by the number appearing in the upper right corner of the screen.

- ② Stop: When a DVD is playing, press this button once to place the disc in the Resume mode, which means that playback will stop. However, as long as the disc drawer is not opened, playback will continue from the point where the disc was stopped when the Play Button ② ③ is pressed again, as indicated by the LAST SCENE message (for DVDs) or the RESUME message (for CDs, MP3 files, JPEG files and VCDs with PBC) in the Information Display 12. Resume will not operate for WMA files or VCDs that do not have playback control. Pressing the button twice will stop the disc and play will start from the beginning of the disc when the Play Button ② 3 is pressed again.

- Next Step/Skip: Press this button once to advance to the beginning of the next chapter on a DVD or track on a CD. Press it again to continue to advance through the remaining chapters or tracks. After first pressing the Pause Button (2), press this button to step through a DVD-Video disc as a series of still-image frames.

- **23** Disc Menu: While a DVD is playing, press this button to view the disc's main menu.

- Status: Press while a disc is playing to view the on-screen status banner display. The first press will display the current title and chapter, the play mode icon and the elapsed time, along with a "temperature bar" display of the time elapsed. You may use the

- Navigation Buttons and the Enter Button to select and change the current title or chapter, or the time display. The Status Banner is only available for DVDs and VCDs when PBC is turned off. Press the button one more time to remove the status displays from the screen. More detailed information about the disc is available by pressing the Info Button .

- **30** Numeric Keys: Press these buttons to enter a number.

- Title: When a DVD is playing, press this button to go back to the main title menu for the disc being played. If you are playing a DVD-Audio disc that contains other formats the DVD 37 is capable of playing, such as linear PCM or Dolby Digital 5.1, pressing this button may enable you to switch playback from one audio format to another.

Subtitle: When a DVD is playing, press to select a subtitle language or to turn subtitles off.

**NOTE:** Due to the variations in how DVD discs are authored, the subtitle languages displayed by the DVD 37 may not accurately reflect the actual languages available on the disc. It is recommended that subtitles be selected using the disc's menu.

- Representation of the standard of the standard

- (3) IR Emitter: This small, clear button-like device sends the IR commands from the remote control to the DVD 37. To ensure proper performance of the remote control, be sure to point it toward the unit and do not cover it with your fingers when sending remote commands.

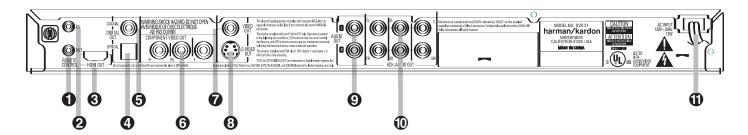

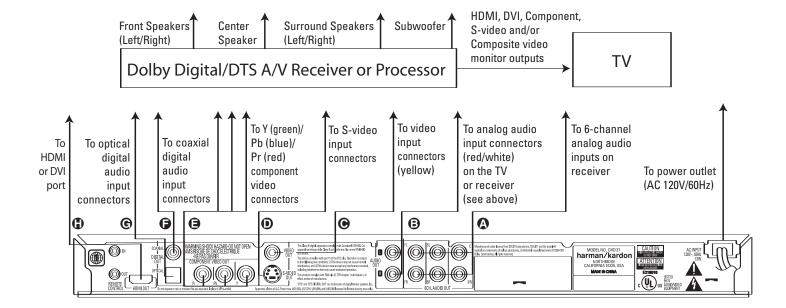

### REAR-PANEL CONNECTIONS

**NOTE:** To make it easier to follow the instructions that refer to the controls and connectors in this illustration, a larger copy may be downloaded from the Product Support section for this product at www.harmankardon.com.

- Remote Control Output

- 2 Remote Control Input

- **3** HDMI Output

- 4 Optical Digital Audio Output

- Remote Control Output: Connect this jack to the infrared (IR) input jack of another compatible remote-controlled product to have the built-in Remote Sensor on the DVD 37 provide IR signals to other compatible products.

- **2** Remote Control Input: Connect the output of a remote infrared sensor, or the remote control output of another compatible product, to this jack. This will enable the remote control to operate even when the front-panel Remote Sensor on the DVD 37 is blocked. This jack may also be used with compatible IR remote control-based automation systems.

- **3 HDMI Output:** If you have an HDMI-compatible receiver or video display device, connect this output to an HDMI input on the receiver or video display for high-quality uncompressed digital audio and video. Even if your receiver is not capable of processing audio in the HDMI format, you will still experience the superb reproduction of HDMI video.

If your video display has a DVI input, you may use an optional HDMI-to-DVI cable or adapter for the connection to the display. In all cases, the video display must be HDCP-compliant in order to use the HDMI output. For best results, we do not recommend HDMI connections in excess of ten feet.

The following audio formats may be output via the HDMI connection:

Audio CD — 2-Channel PCM or 5.1-channel DTS DVD-Audio and SACD — 2-Channel PCM DVD-Video — Up to 5.1-channel Dolby Digital or DTS NOTE: To hear the high-resolution surround sound recorded on DVD-Audio discs, you need to connect the 6-Channel Audio Outputs 10 to the corresponding input jacks on your receiver or processor. These formats are not output digitally.

- 6 Coaxial Digital Audio Output

- **6** Component Video Outputs

- **7** Composite Video Output

- S-Video Output

- **4** Optical Digital Audio Output: Connect this jack to the optical digital input of an A/V receiver or surround processor for Dolby Digital, DTS or PCM audio playback.

- **6** Coaxial Digital Audio Output: Connect this jack to the coaxial digital input of an A/V receiver or surround processor for Dolby Digital, DTS or PCM audio playback.

#### NOTES:

- Connect either the Optical Digital Audio Output

or the Coaxial Digital Audio Output

to a corresponding digital audio input on your receiver or processor, but not both.

- The coaxial digital output should only be connected to a digital input. Even though it is the same RCAtype connector as standard analog audio connections, DO NOT connect it to a conventional analog input jack.

- **6** Component Video Outputs: These outputs carry the component video signals for connection to display monitors with component video inputs. For standard analog TVs or projectors with inputs marked Y/Pr/Pb or Y/Cr/Cb, connect these outputs to the corresponding inputs. If you have a high-definition television or projector that is compatible with high-scan-rate progressive video (480p or better), connect these jacks to the HD component inputs. If you are using a progressive scan display device, **PROGRESSIVE** must be selected in the Video menu in order to take advantage of the progressive scan circuitry. See the "Scan Type" section on page 23 for more information on progressive scan video.

**IMPORTANT:** These jacks should NOT be connected to standard composite video inputs.

- Analog Audio Outputs

- 6-Channel Audio Outputs

- **11** AC Power Cord

- **©** Composite Video Output: Connect this jack to the video input on a television or video projector, or to a video input on an A/V receiver or processor if you are using that type of device for video input switching.

- **3** S-Video Output: Connect this jack to the S-video input on a television or video projector, or to an S-video input on an A/V receiver or processor if you are using that type of device for S-video input switching.

- (3) Analog Audio Outputs: Connect these jacks to an audio input on an A/V receiver, surround processor or your television for analog audio playback.

- 6-Channel Audio Outputs: Connect these outputs to the matching 6-channel analog audio inputs on your receiver or surround sound processor. This connection is required to listen to the multichannel tracks on DVD-Audio discs. If the disc also contains a linear PCM, Dolby Digital or DTS track, you may listen to it using the HDMI Output ③, Optical Output ④ or Coaxial Digital Audio Output ⑤ or the Analog Audio Outputs ④.

- (f) AC Power Cord: Connect the AC power cord to an AC outlet. If the outlet is controlled by a switch, make certain that it is in the ON position. If the cord somehow becomes damaged, contact your authorized Harman Kardon dealer for a replacement.

**NOTE:** You'll find more details about all audio/video connections under Setup and Connections on the following pages.

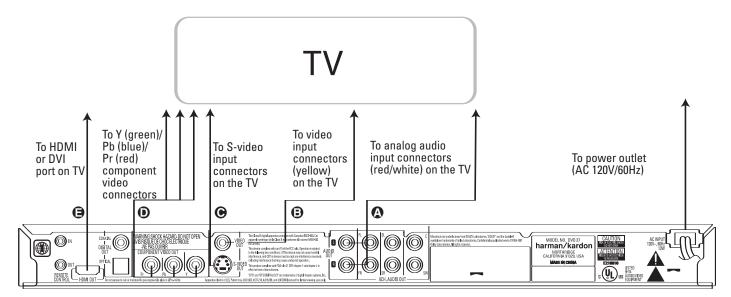

### SETUP AND CONNECTIONS

- Ensure that the power switch of this unit (and of other equipment to be connected) is set to "Off" before commencing connection. We also strongly recommend that you leave all system components unplugged from AC power until after you have completed the interconnections described in this section.

- Do not block the ventilation holes of any of the equipment and arrange them so that air can circulate freely.

- Read through the instructions before connecting other equipment.

- Ensure that you observe the color-coding when connecting audio and video cables.

#### VIDEO NOTES:

For the best quality, if your receiver or processor and/or video display are HDMI-capable, we recommend using the HDMI output. With a single cable connection between components, HDMI is able to deliver uncompressed high-definition digital video and digital audio programming. Even without audio processing capability, your HDMI-ready receiver will be able to pass the uncompressed digital video signal to your video display.

**NOTE:** If your video display has a DVI input, you may use an optional HDMI-to-DVI cable or adapter for the connection to the display. In all cases, the video display must be HDCP-compliant in order to use the HDMI output.

If your equipment is not HDMI-ready, we recommend the use of component video for higher quality pictures. You may also use the standard S-video or composite video connection if your TV does not have component video inputs. The component and S-video outputs are not available simultaneously.

- The composite video output (yellow) sends the complete video signal to the TV (or to the AVV receiver) by one cable only. Use this video output when your TV set is equipped with a video input jack only.

- The S (separate) video output connector separates the color (C) and luminance (Y) signals before transmitting them to the TV set in order to achieve a sharper picture. Use the S-video cable when connecting the player to a TV equipped with an S-video input for improved picture clarity.

- The component video outputs further separate the color components of the video signal, optimizing the DVD 37's video performance. Component video connections are preferred, when available on your TV or receiver. If you are using a TV or video display that is compatible with high-resolution 480P video signals, use the input jacks on the video display marked "HD Component," if available. Also, be sure to configure the display's input settings for use with "480P" video signals. You will also need to change the scan type in the DVD 37's Video Setup menu from "Interlaced" to "Progressive." See page 23.

- Modern audio/video receivers are capable of connection to several video source devices, such as the DVD 37 and a VCR, cable television set-top box, HDTV tuner or other device. The receiver is equipped with video monitor outputs for connection to your television, projector or flat-panel display. As you select any input source device, the receiver selects the correct video input and routes it to the correct video monitor output to your television. It is recommended that you connect one of the video outputs from the DVD 37 to the corresponding input on your receiver to simplify operation of your home entertainment system. Refer to the owner's guide for your receiver for more information.

• If your receiver is capable of multiroom operation, it is recommended that you connect both the component (or HDMI) and composite video outputs of the DVD 37 to the receiver. This enables the highest-quality picture (component video) for viewing in the main listening room, while enabling the multiroom system, if it is video-capable, to distribute the composite video signal to the remote zone. Consult the owner's guide for your receiver to determine whether it has video multiroom capability.

#### Connecting to a TV Only

When using the DVD 37 with a television but no audio receiver or processor, connect it as follows. Make the Analog Audio Connection (a) and one of the Video Connections (Composite Video (a), S-Video (b), Component Video (b)). If your television or video display is HDMI-capable, you only need to make the HDMI (c) connection, as it handles both audio and video. Remember to plug in the power cord.

**NOTE:** When using the **HDMI (a)** connection, turn on the television or video display *before* the DVD 37.

### SETUP AND CONNECTIONS

#### Connecting to a Receiver/Amplifier With a Dolby Digital or DTS Decoder

One of the major advantages of the DVD format is its ability to use a variety of digital audio formats for the ultimate in sonic performance. However, in order to enjoy the benefits of digital audio, you must use a receiver or processor that has digital audio decoding capabilities and make an optical or coaxial digital audio connection between the DVD 37 and your home theater system. This simple connection is made as shown below with an optional coax or optical cable. Only one of these connections is required, and both should not be made at the same time.

In order to take advantage of the high-resolution DVD-Audio output of the DVD 37, you must connect the **6-Channel Audio Outputs 1** to the matching 6-channel inputs on your receiver or processor. Only compressed PCM, Dolby Digital or DTS tracks that may be present on the disc may be listened to using the digital audio outputs. Thus, the DVD 37 decodes the digital signal and outputs separate signals for each channel: front left, center, front right, surround right, surround left and low-frequency effects (LFE).

#### **NOTES FOR ANALOG AUDIO:**

- If you wish to use the DVD 37 as the input for a multiroom system, the Analog Audio Outputs (9) should be connected to the standard analog left/ right DVD or CD inputs on your digital receiver or processor.

- The connection from the Analog Audio Outputs

to the TV is optional. If you plan on occasionally using your DVD 37 alone, without turning on your complete system, this connection must be made.

- When the audio signal is to be fed to an analog receiver rather than to the TV, connect the Analog Audio Outputs to any analog audio inputs on your receiver or processor. The DVD 37 will "downmix" multichannel recordings to two channels.

- The analog audio connection should also be made if you wish to play high-resolution 96kHz PCM audio discs where your receiver does not support 96kHz processing.

- In each of these four cases in which the Analog Audio Outputs

are used, set the bass management line of the AUDIO SETUP menu to STEREO.

#### NOTES ON VIDEO:

- With multiple video sources, your audio/video receiver can be used for selecting the video signal and routing it to the TV. Connect the HDMI ③, Component ⑤, Composite ⑥ or S-Video ⑦ output of the DVD 37 to the correct video input on your receiver, and the video outputs of the receiver to your TV. For more details, see the manual for your audio/video receiver.

- If your receiver has only DVI inputs, you may use an optional HDMI-to-DVI cable or adapter for the connection to the receiver. In addition, the video display used with your system must be HDCP-compatible in order to take advantage of the HDMI output, whether it is used with HDMI or DVI connections.

#### Connecting to a Receiver

When using the DVD 37 with an audio/video receiver or processor, connect it as follows. First, make one

of the video connections (Composite Video , S-Video , Component Video or HDMI ) to the video input jacks on the A/V receiver, and then connect the receiver's video monitor output to the TV. If you will sometimes use the TV without the audio component, you may optionally make the Analog Audio Connection to the TV. In addition, to benefit from the high-resolution surround sound formats recorded on DVD-Audio discs, which are not output via the HDMI connection, you will need to make the 6-Channel Audio Connection to your receiver or processor.

Second, if your receiver or processor is not HDMI-capable, make either the Optical Digital Audio Connection or the Coaxial Digital Audio Connection to the receiver or processor. Remember that when the HDMI connection is used with a receiver or processor that is compliant with the HDMI format, a single connection suffices for both audio and video, except for DVD-Audio discs, as noted. If your receiver or processor is not capable of processing the HDMI audio signal, then a separate audio connection is required. If your receiver/processor has multiroom capability, you may also connect the DVD 37's analog audio outputs to the DVD analog audio inputs on the receiver.

IMPORTANT NOTE: Make certain that any device being connected, including the DVD 37, your receiver or processor and your TV or video display, is turned off whenever you make connections between products. When using the HDMI connection, turn on your system components in this order: 1) television or video display, 2) receiver or processor, and 3) DVD 37.

### SYSTEM SETUP

#### System Setup

The final step in the installation of the DVD 37 is to establish the system's configuration. Before proceeding further to make any adjustments, make certain that the DVD 37 is properly connected to a video display and an AC power source. Turn on the DVD 37 by pressing the Power On/Off Switch 2 and the Power Indicator 1 will change from amber to blue. You do not need to play a CD or DVD in the unit to make system setup adjustments.

In many cases, you will be able to accept the default settings. Of course, these settings may be changed at any time to reflect changes to the other equipment in your home theater system or to adjust the DVD 37's output or operation to your needs and preferences.

#### Menus and Navigation

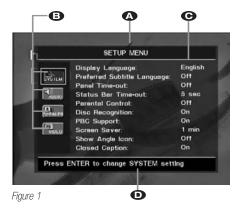

The DVD 37 uses an elegant but simple on-screen menu system for all setup and control functions. There are two main menus that are navigated in a similar fashion:

- The **SETUP** menu is used to establish the basic configuration settings for all aspects of the DVD player's operation, including language and display settings, audio settings, video settings and adjustments, speaker bass management settings, parental control and other settings that you may customize. The **SETUP** menu is accessed by pressing the **Setup Button** .

- The PLAYER INFORMATION menu displays information about the current disc, allowing you to set the playback mode and create a playlist if desired. The PLAYER INFORMATION menu will appear on screen automatically for audioonly and JPEG discs, and for VCDs without PBC. For DVDs and VCDs with PBC, it may be accessed by pressing the Info Button (3).

The two main menus share a common layout, and are navigated in a similar manner. The menu screen is divided into four main areas:

A: Menu Title: The top line identifies which main menu is on screen.

(a): The submenus listed in a vertical column at the left side of the screen access the specific groups of settings or controls. The submenu that is at the top of the list will be highlighted. As indicated on the Instruction Line (b), press the Enter Button (c) to select that submenu, which will move the cursor to the first Control Setting (c).

On the Setup Main Menu, the Available Submenus Are:

- The SYSTEM SETUP menu, identified by a wrench icon and the word SYSTEM, is used to establish the general settings for the player.

- The AUDIO SETUP menu, identified by a speaker icon and the word AUDIO, is used to establish the settings for the player's audio output.

- The SPEAKER SETUP menu, identified by a loudspeaker cabinet icon, is used to establish the bass management settings for the audio output at the 6-Channel Audio Outputs (1) that are used when a DVD-Audio disc is playing.

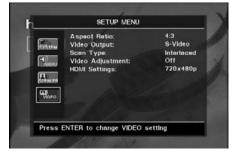

- The VIDEO SETUP menu, identified by a TV icon and the word VIDEO, is used to establish the video formatting and configuration settings and to access the video adjustments screen for the picture settings.

On the Player Information Menu, the Available Submenus Are:

- The PLAYBACK INFO menu, identified by an "i" icon, includes the disc type and name (if available on the disc), and contains settings to control the playback mode.

- The PROGRAM menu, identified by an icon showing musical notes, is used to program a playlist, which lets you play back selected CD tracks in the order you choose. Playlists are only available for audio CDs.

- The DISC INFO menu, identified by a disc icon, provides detailed information about the video and audio content on the disc being played.

Control Settings: The main area of each menu screen shows a list of the control settings available for the current submenu. On the left side of the main area is a listing of the settings available. To the right of each line is the current value for each setting. To adjust a specific setting, press the ▲ ▼ Navigation Buttons ② until the setting for the desired item is highlighted. Next, press the Enter Button ② and a dropdown menu will appear that contains the available options for that setting. Press the ▲ ▼ Navigation Buttons ① until the desired option is highlighted, then press the Enter Button ② to select that option. See Figure 2 for an example of a dropdown menu.

Figure 2

**Instruction Line:** The DVD 37 will display the appropriate instructions in this area to assist you in navigating the menu system and making changes to the various settings.

Within a given menu, adjustments are made using the following steps and commands on the remote control:

- Press the Navigation Buttons to select an item to be adjusted.

- When the current setting for the item to be adjusted is highlighted, press the **Enter Button 21**.

- When the desired setting is highlighted or the numeric entry made, press the **Enter Button 21**.

- Press the **Navigation Buttons** to select another item for adjustment, if required.

- When all required adjustments on this submenu have been made, press the → Navigation

Buttons → Navigation

Area → Navigation

Buttons → Navigation

Buttons → Navigation

Buttons → Navigation

- If all adjustments are complete, press the Setup Button to exit the SETUP menu, or press the Info Button to exit the PLAYER INFORMATION menu.

Most DVDs are created to allow setup menus to be displayed while the disc is playing, superimposed over the video playback. However, some discs are authored

### SYSTEM SETUP

in a way that does not allow this. If you see the Ø icon displayed on the screen after pressing the Setup Button ① or the Info Button ②, press the Stop Button ② and then press the Setup or Info Button ① ③ again.

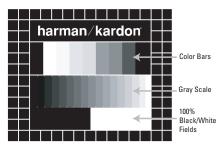

This method of navigation, option selection and adjustment applies to all menus except for the Video Adjustments menu, which accommodates the need to view the on-screen video or the DVD 37's internal test signal while the settings are being made. See page 24 for information on changing the Video Adjustments.

The **SPEAKER SETUP** menu uses the same navigation method, but with a slightly different arrangement. Since adjustments are made to accommodate the speaker used for each channel, the settings for each speaker are displayed according to their placement in the listening room.

#### Setup Menu

The four submenus within the **SETUP** menu are where you establish the basic system settings for the DVD 37. Most of these settings need to be adjusted only once, and in many cases you will find that the system defaults are the correct option for your combination of components. However, it is worth a few minutes to briefly scan through each of the Submenus to confirm that the settings are correct and to familiarize yourself with the available options so that you are aware of the flexibility of the DVD 37.

#### System Setup Submenu

The **SYSTEM SETUP** submenu is where you establish the control options, languages and displays. In most cases, the system default options are sufficient for normal operation, but you may wish to change them to tailor the unit's operation to your preferences.

Access the SYSTEM SETUP submenu by pressing the Setup Button to display the main SETUP menu. The System icon should be highlighted. If it isn't, use the Wavigation Buttons to highlight the icon. As indicated on the Instruction Line P, press the Enter Button to access the settings in SYSTEM SETUP.

The following adjustments may be made on the **SYSTEM SETUP** menu.

Figure 3

**Display Language:** This setting selects the language that will be used for the DVD 37's OSD menus and other system messages. The default is English, but you may also select French, Spanish, German or Italian.

**Preferred Subtitle Language:** This setting selects the language used for the display of subtitles. The default setting is **OFF**, to play discs without subtitles. To set the player so that subtitles will always play in a specific language when they are available, select from the choices shown in the drop down menu.

If you do not find your preferred language in the list of options, you may select a preferred language by first pressing the \( \rightarrow \rightarrow Navigation Buttons \( \frac{1}{4} \) so that \( \frac{0}{1} \) THER is highlighted in the dropdown menu. Press the Enter Button \( \frac{1}{4} \) and then use the \( \rightarrow \rightarrow \rightarrow Navigation Buttons \( \frac{1}{4} \) to select a subtitle language (see Figure 4). When the desired language is highlighted, press the Enter Button \( \frac{1}{4} \) to set it as the preferred subtitle language.

This procedure selects a preferred subtitle language, but it will only be available when the disc being played contains that language. The list of subtitles available on any given disc is always shown on the disc jacket, usually at the bottom of the back cover. Note that the subtitles may also be switched on or off, or a new language selected during playback using the **Subtitle Button** 32, as described on page 30.

If you have selected a subtitle language and subtitles do not appear on screen, press the **Subtitle Button** to display the Subtitle banner. Each press of the **Enter Button** will cycle through the subtitle languages available on the disc. If subtitles still do not appear, press the **Disc Menu Button** to make sure that subtitling has been selected in the disc's menu system.

**NOTE**: Due to the variations in how DVD discs are authored, the subtitle languages displayed by the DVD 37 may not accurately reflect the actual languages available on the disc. It is recommended that subtitles be selected using the disc's menu.

Figure 4

Panel Time-Out: This setting allows you to select the length of time the Front-Panel Display 2 remains illuminated during disc playback (as some people find the front-panel display to be distracting while a movie is playing). You may program the DVD 37 to refresh the front-panel display only when a button is pressed on the remote or front panel, and to turn the display off again after either five or 20 seconds. When the display is off, the blue Power Indicator will remain lit to remind you that the unit is turned on. When the Panel Time-Out setting is set to "Off," the display remains lit at all times. This feature is only in effect when a DVD or VCD is playing. However, you may always press the Dimmer Button 1 to dim the front-panel display either by half or fully.

Status Bar Time-Out: This setting selects the time-out interval for the on-screen Status Bar that appears at the top of your video screen when the Status Button (29) is pressed while a disc is playing. During DVD playback, the status bar shows the current title and chapter, the elapsed or remaining time in the current chapter or title, a setting to adjust the time display, and a temperature bar for the time display.

You may program the status bar to remain on screen for either five or 20 seconds after the **Status Button** is pressed. When **OFF** is selected, the timeout is disabled, and the status bar will remain on the screen until the **Status Button** or **Clear Button** is pressed.

Parental Control: The DVD 37's password system allows you to restrict viewing of certain materials that may not be suitable for younger members of the household by requiring the viewer to enter a password before viewing those materials. The system is based on rating information encoded in the DVD that classifies materials into eight levels, roughly corresponding to the Motion Picture Association of America (MPAA) voluntary ratings system:

**Level 1:** Corresponds to the MPAA's "G" (General Audiences) rating, and is considered suitable for all viewers.

**Level 2:** Intermediate level between the "PG" and "G" ratings.

**Level 3:** Corresponds to the MPAA's "PG" (Parental Guidance) rating.

**Level 4:** Corresponds to the MPAA's "PG-13" (Parental Guidance and 13 years old) rating.

**Level 5:** Intermediate level between the "R" and "PG-13" ratings.

**Level 6:** Corresponds to the MPAA's "R" (Restricted) rating.

**Level 7:** Corresponds to the MPAA's "NC-17" (17 years and older) rating.

### SYSTEM SETUP

**Level 8:** All DVDs, including adult materials, can be played.

**Unlocked:** Any DVD may be viewed without entering the password.

The DVD 37 is shipped from the factory with the parental control system unlocked (no password is required to view any DVD), and with the password set to the four-digit code "1234." To activate the system, use the \\_\ \Navigation Buttons \( \begin{align\*} \Delta \) to highlight the Parental Control Setting on the \( \SYSTEM \) \( \SETUP \) submenu, and press the \( \text{Enter Button} \) \( \begin{align\*} \Delta \) Select the "On" setting from the dropdown menu, and the password screen will appear (see Figure 5.) Make sure the dashes on the Password line are highlighted, then enter the password code using the Numeric Keys \( \begin{align\*} \Delta \) and press the \( \bigcup \)

If you have entered the password correctly, the current setting of the Rating line will be highlighted. You may press the Enter Button 2 to display the ratings dropdown menu. Select a new rating using the Navigation Buttons 2 and the Enter Button 2.

Figure 5

The first time you use the DVD 37, it is recommended that you scroll down to the Change Password line and press the Enter Button to display the Change Password screen. Use the Numeric Keys to enter your new password once at the New Password line, and a second time at the Confirm Password line. The DVD 37 will return to the screen shown in Figure 5, where you may then change the Ratings Setting. Since you had previously entered a valid password, you will not be required to enter a password again before changing the rating. However, once you press the Navigation Button And return to the SYSTEM SETUP submenu, the new password will take effect

**Disc Recognition:** The setting for the Disc Recognition feature, when turned on, allows you to pause or stop a DVD-Video disc, remove it from the player, play another disc, and then resume playback of the original disc at a later time from the point at which you paused. When a previously played disc is reinserted in the DVD 37, you will be presented with an on-screen status message asking whether you wish to start play-

back from the beginning of the disc or resume at the point where you left off. Note that even when the setting is activated, you must press the **Stop Button** [5] [26] either once (Resume mode) or twice (Stop mode), but not the **Pause Button** [4] [22]. The unit may be turned off between discs. The DVD 37 can store the information for up to five DVDs at a time.

**PBC Support:** This setting controls the activation of PBC (Play Back Control) Support for VCD discs. If you plan to play VCD discs, which are a CD-ROM-based format that predates DVD, we recommend that the setting be turned **ON**. However, with PBC enabled, the Repeat Track, Repeat Disc and Random functions will not be available for VCDs.

Screen Saver: The DVD 37 offers a Screen Saver option to protect your TV or video display from damage that may occur if the player is left turned on with the same still image for a period of time, as there is a possibility that the image may be "burned" into some display devices. This is particularly important for plasma displays and some CRT devices. Set Screen Saver to  $\mathbf{O}\,\mathbf{N}$  so that the DVD 37 will run the screen saver when no action has been detected for either one or five minutes. Press a desired command key on the front panel or remote to "wake" the DVD 37 and resume normal operation.

Show Angle Icon: Some DVDs are programmed with multiple-angle capability, allowing you to view the same scene from a different camera angle. Normally, the angle icon will be displayed on screen during those scenes to inform you that you may press the Angle Button (3) to change to a different view. If you would find the appearance of the icon on-screen distracting, select the Show Angle Icon setting in the System submenu, and set it to 0 F F. The Angle Indicator (3) will appear in the front-panel display whenever multiple angles are available, regardless of whether the on-screen icon appears.

Closed Caption: This setting enables viewing of closed caption messages, if they have been encoded in the video material. Closed captions — text displays of the program's dialogue which are normally hidden from view — are made available for the hearing-impaired or others. Select the **ON** setting to activate the DVD 37's closed captioning decoder so that these messages may be viewed.

#### Audio Setup Submenu

This submenu establishes the DVD's configuration for general audio settings, such as preferred language and digital audio settings.

As with all setup menus, press the Setup Button to activate the main menu screen, and then press the Navigation Buttons until the AUDIOSETUP icon is highlighted, and press the Enter Button again.

Figure 6

The following adjustments are available on the Audio Setup menu:

Preferred Audio Language: This setting is used to select the default language that will be used for program playback. The factory default setting is English, but you may choose French, Spanish, German or Italian by making a selection from the dropdown menu. To select a language other than those shown, select **OTHER** from the dropdown menu and press the **Enter Button 21**. A screen will appear with a list of language choices (see Figure 4). Use the AVAN Navigation Buttons (1) to select a language. When the desired language is highlighted, press the Enter Button 21 to set it as the preferred audio language. If you wish to exit this screen without selecting a language, use the

Navigation Buttons until the word RETURN at the bottom of the screen is highlighted, and press the Enter Button (2) to return to the AUDIO SETUP screen.

This procedure selects a preferred audio program language, but it will only be available when the disc being played contains that language. The list of languages available on any given disc is always shown on the disc jacket, usually at the bottom of the back cover. Note that the audio playback language may also be changed at any time during playback using the **Audio Select Button 3**, as described on page 30, but any changes made will only be effective during playback of that disc.

Digital Output: This setting selects the digital audio data stream that is routed to the Optical Digital Output 4 or the Coaxial Digital Output 5.

Two choices are available:

- Bitstream, the default setting, outputs the Dolby Digital or DTS signal, as selected from the disc's menu or by using the Audio Select Button

a, as explained on page 30. This setting should be used when your receiver or processor is capable of decoding signals in the Dolby Digital or DTS format.

- PCM outputs a standard PCM signal for decoding by receivers or processors that are not capable of decoding a Dolby Digital or DTS bitstream. This setting enables 2-channel audio playback or matrix decoding where available.

### SYSTEM SETUP

**NOTE:** Any changes made to the Digital Output setting during playback will not take effect until after play has been stopped and restarted.