### D-5500 (U,C,W,FS,BS,AU)

### SERVICE MANUAL

**English** No. 1193-1

1278

This unit employs the UD-1 standard mechanism. When inspecting and repairing this unit, read this together with the service manual (No. 1155) of the UD mechanism (UD-1).

### Note:

U ..... USA

C ..... Canada

W General Area

FS ..... Switzerland and

Scandinavia

BS..... Great Britain

AU..... Australia

### SAFETY PRECAUTION -

The following precautions should be observed when servicing.

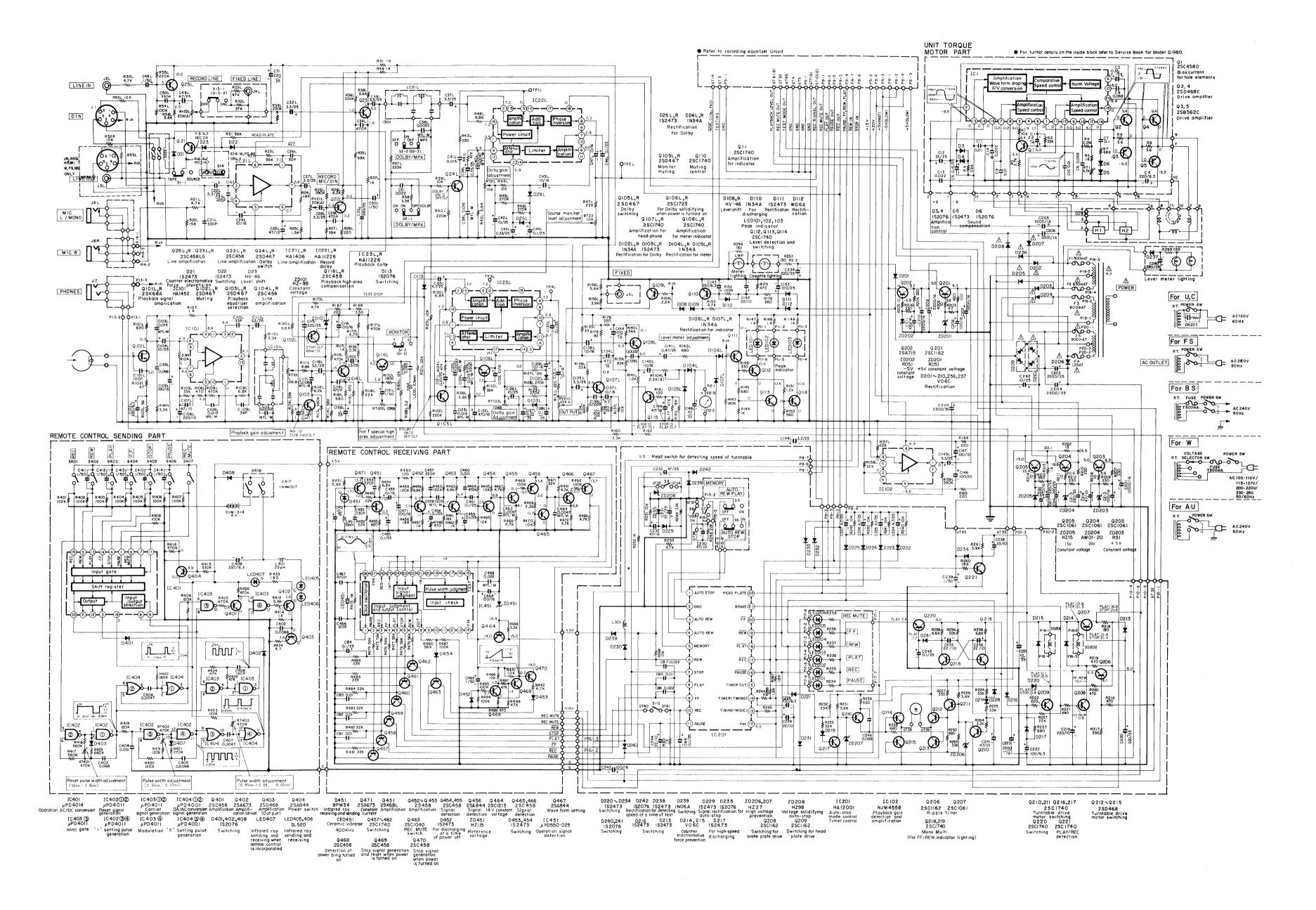

- 1. Since many parts in the unit have special safety related characteristics, always use genuine Hitachi's replacement parts. Especially critical parts in the power circuit block should not be replaced with other makers. Critical parts are marked with A in the schematic diagram, and circuit board diagram.

- 2. Before returning a repaired unit to the customer, the service technician must thoroughly test the unit to ascertain that it is completely safe to operate without danger of electrical shock.

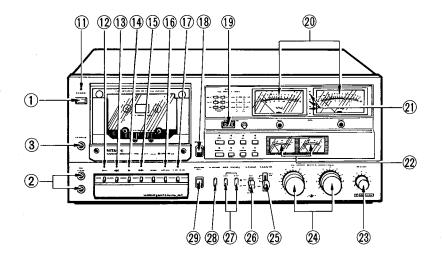

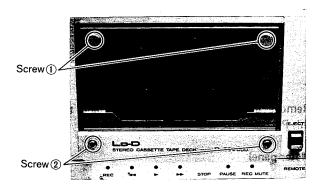

### **KEY TO ILLUSTALATIONS**

**①POWER SWITCH**

**②MIC JACKS (MIC)**

③HEADPHONE JACK (PHONES)

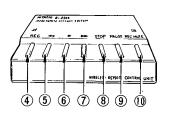

④RECORDING BUTTON (REC) ⑤REWIND BUTTON (◀ ◀)

**©PLAYBACK BUTTON** ()

⑦FAST-FORWARD BUTTON (▶ ▶)

®STOP BUTTONS (STOP)

PAUSE BUTTON (PAUSE) **®REC MUTE SWITCH (REC MUTE)**

**(1) POWER INDICATOR**

@rec indicator

③REWIND INDICATOR

**14 PLAYBACK INDICATOR**

(15) FAST FORWARD INDICATOR

(6) PAUSE INDICATOR

TREC MUTE INDICATOR

(®EJECT BUTTON (EJECT)

**®TAPE COUNTER (TAPE COUNTER)**

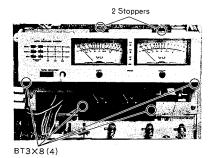

**MOVU METERS**

②PEAK INDICATOR

@BIAS/TAPE SENSITIVITY INDICATING

**METERS**

**33OUTPUT LEVEL CONTROL (OUTPUT)**

@RECORDING LEVEL CONTROLS (RECORD)

**®DOLBY NOISE REDUCTION SWITCH/MPX**

FILTER SWITCH (DOLBY NR)

**26 MONITOR SWITCH (MONITOR)**

**②AUTO-REWIND SWITCHES**

<sup>®</sup>MEMORY SWITCH (MEMORY)

**②CONTROL UNIT REMOVAL BUTTON**

(REMOTE REMOVAL)

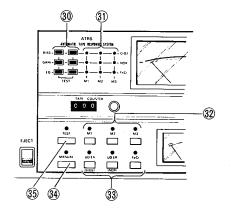

**30 TEST INDICATOS**

3 MEMORY INDICATORS

**32 MEMORY BUTTONS**

**33 TAPE SELECT BUTTONS** 39 MANUAL BUTTON (MANUAL)

③ TEST BUTTON (TEST)

### STEREO CASSETTE TAPE DECK

### CONTENTS

| SP  | ECIFICATIONS                                                            | 4  |

|-----|-------------------------------------------------------------------------|----|

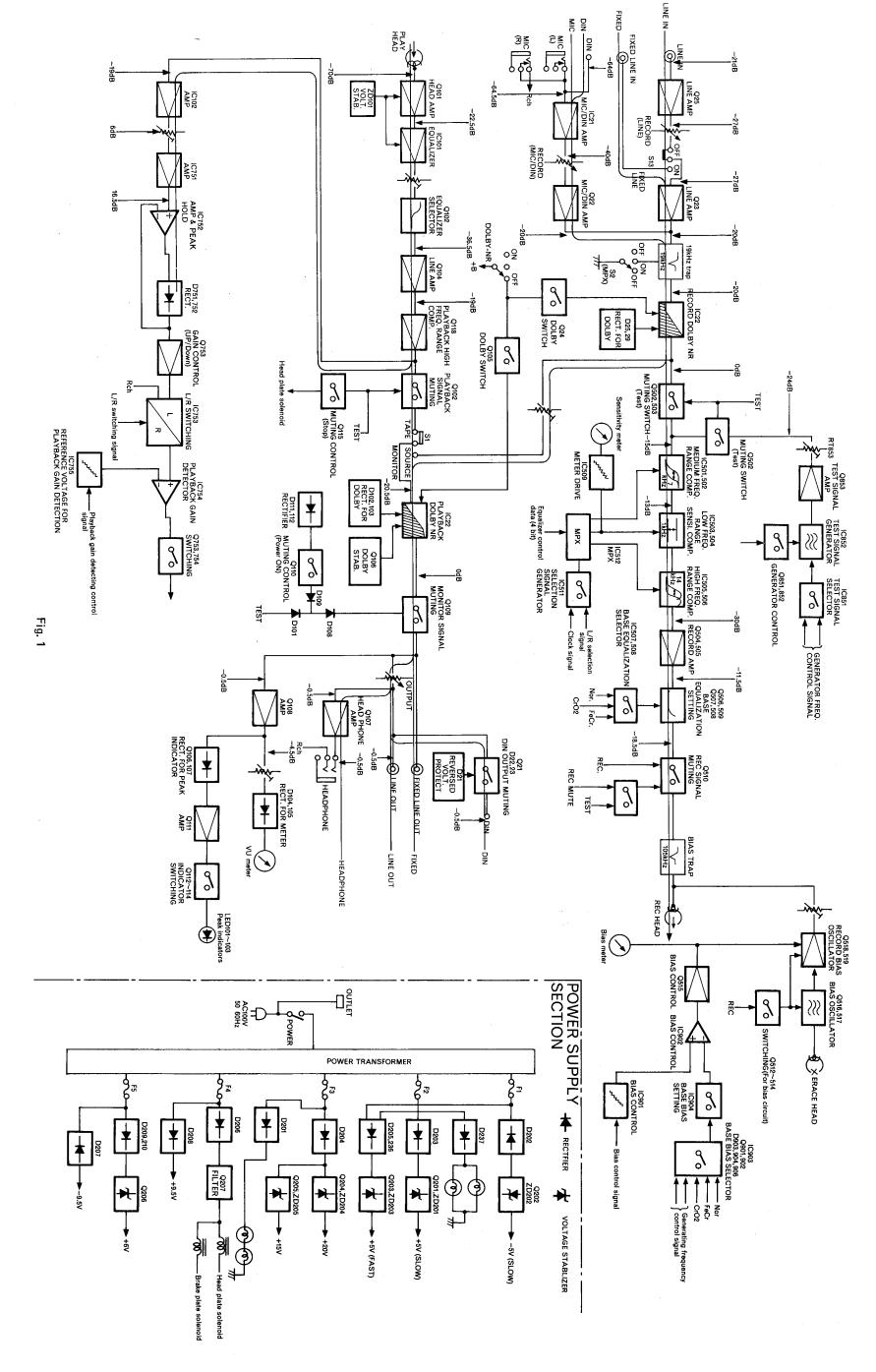

| BL  | OCK DIAGRAM (Amplifier and Power supply sections)                       | 5  |

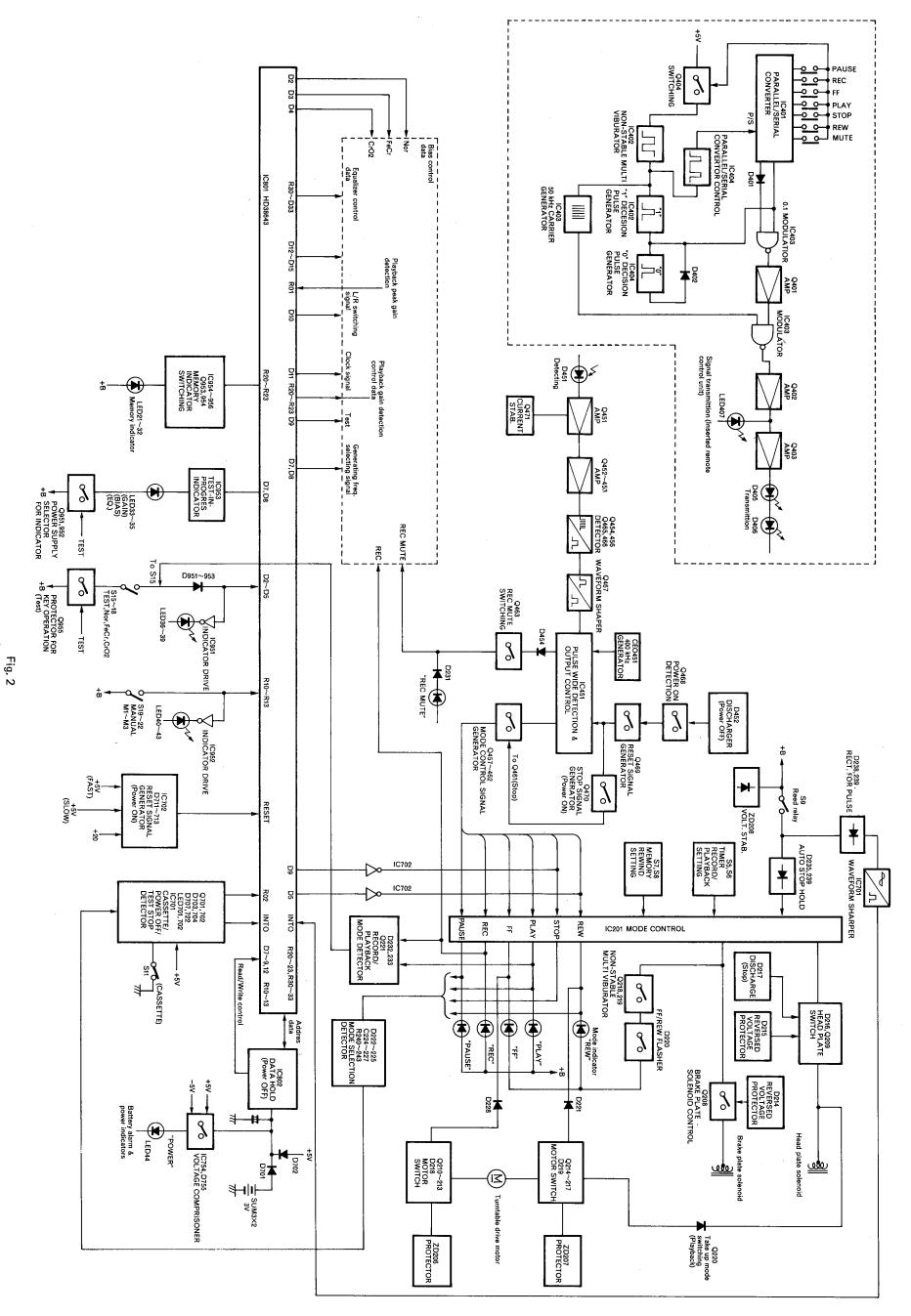

| ВL  | OCK DIAGRAM (Control section)                                           | 7  |

| TE  | CHNICAL INFORMATION OF ATRS                                             | 9  |

| 1.  | Operation and Description of Each Mode                                  | 9  |

| 2.  | Initial Start Circuit when the power is switched ON                     | 10 |

|     | 1) Operation when power is switched ON                                  | 10 |

|     | 2) Operation immediately after power is switched OFF                    | 10 |

| 3.  | Power OFF, Cassette and Test Mode Stop Detections                       | 11 |

|     | 1) Power OFF detection                                                  | 11 |

|     | 2) Cassette detection                                                   | 11 |

|     | 3) Test mode stop detection                                             | 12 |

| 4.  | Tape Selector/Memory Selections                                         | 12 |

|     | 1) Tape selector selection                                              |    |

|     | 2) Memory selection                                                     |    |

| 5.  | Test Mode Selection                                                     |    |

|     | Test Data Transfer to Memory                                            |    |

|     | Stop Signal Generation Circuit                                          |    |

|     | Battery Alarm Circuit                                                   |    |

|     | IC HD74145P                                                             |    |

|     | Memory Indicator Circuit                                                |    |

|     | Data Storage when power is switched OFF                                 |    |

|     | Recording/Playback Circuit Block Diagram                                |    |

|     | Playback High Frequency Range Compensation Circuit                      |    |

|     | Gain Control Circuit                                                    |    |

|     | 1) Principle of D/A convertor (4 bit control signal)                    |    |

|     | 2) When Z1 — Z4 has pure resistance (R)                                 |    |

|     | 3) When Z1 — Z4 are composed of pure resistance (R) and capacitance (C) |    |

|     | 4) When Z1 — Z4 are composed of resistance (R) and inductance (L)       |    |

|     | 5) Low frequency range sensitivity compensation circuit                 |    |

|     | 6) Medium frequency range compensation circuit                          |    |

|     | 7) High frequency range compensation circuit                            |    |

| 15  | Data Transfer Circuit in Recording Equalizer Section                    |    |

|     | 1) Sift resistor (IC511)                                                |    |

|     | 2) Multiplex (IC512)                                                    |    |

|     | 3) Operation of data transfer circuit                                   |    |

|     | 4) Switching signal generation timing diagram                           |    |

| 16. | Bias Oscillator Circuit                                                 |    |

|     | 1) Oscillator circuit                                                   |    |

|     | 2) Variable recording bias circuit and temperature compensation circuit |    |

|     | 3) Bias/EQ test and tape selector detection circuit                     |    |

|     | 4) Bias setting                                                         |    |

| 17. | Test-in-progress Indicator                                              |    |

|     | Playback Gain Detector Circuit                                          |    |

| •   | 1) Amplifier and rectifier peak hold circuit                            |    |

|     | 2) L/R channel switch                                                   |    |

|     | 3) Comparison and peak detection circuits                               |    |

on

### **D-5500**

### **SERVICE MANUAL**

No. 1193

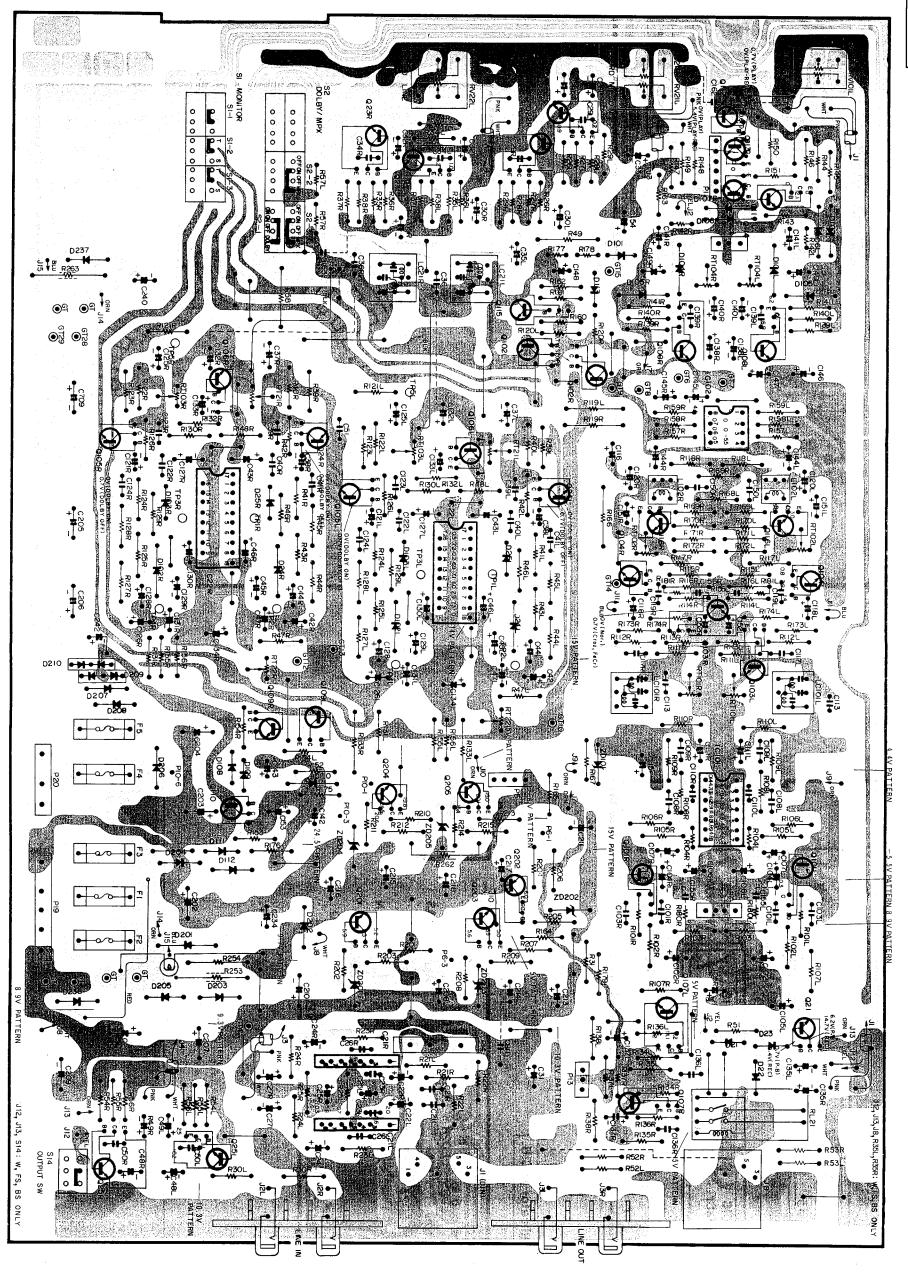

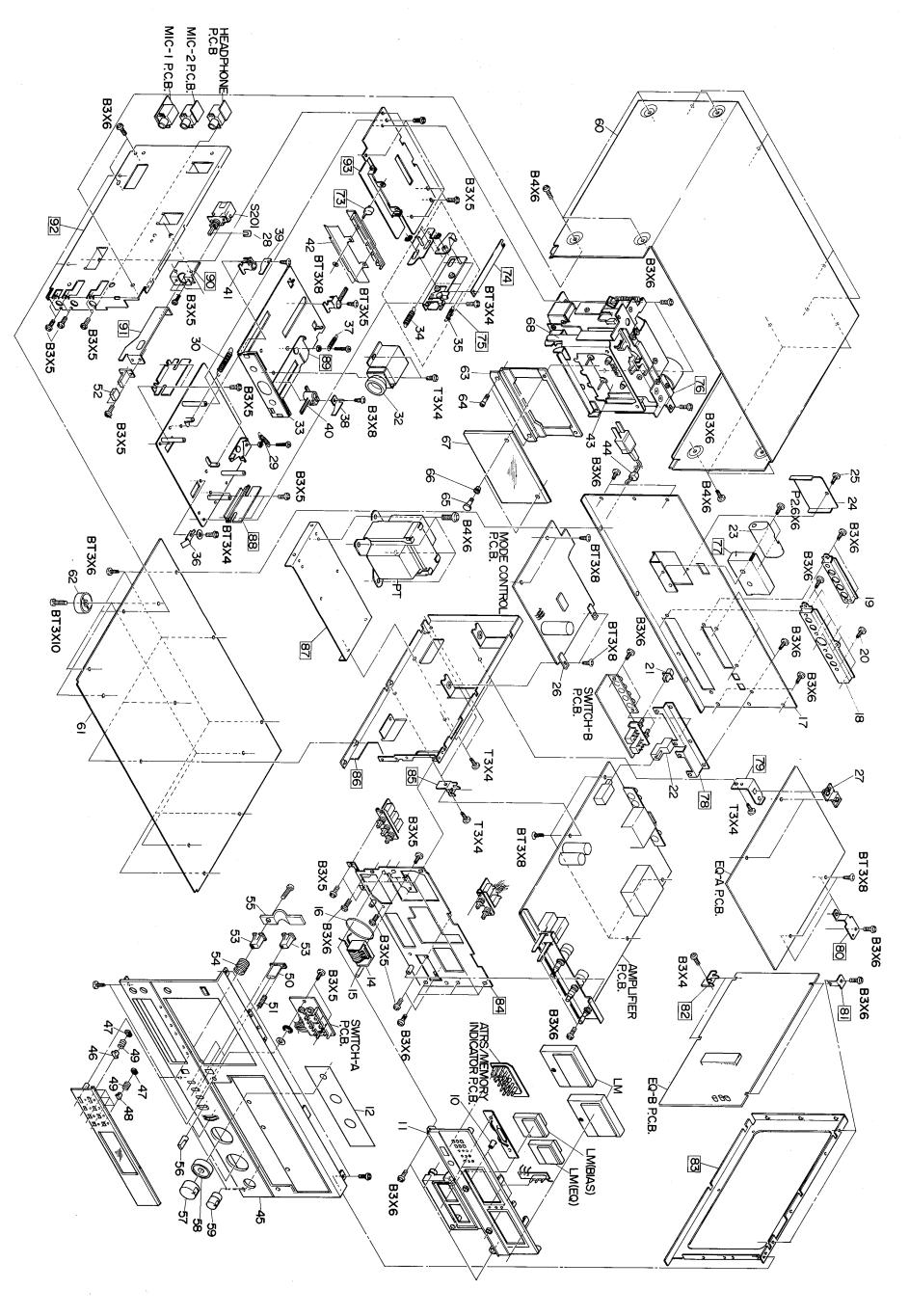

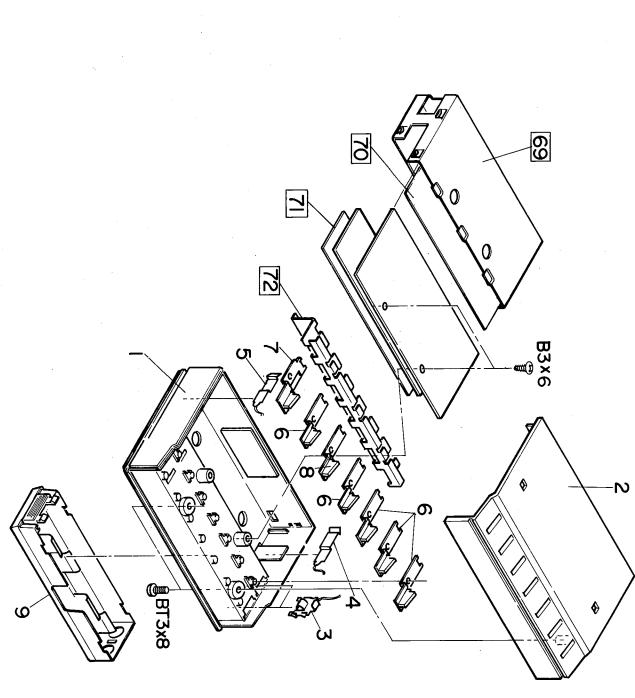

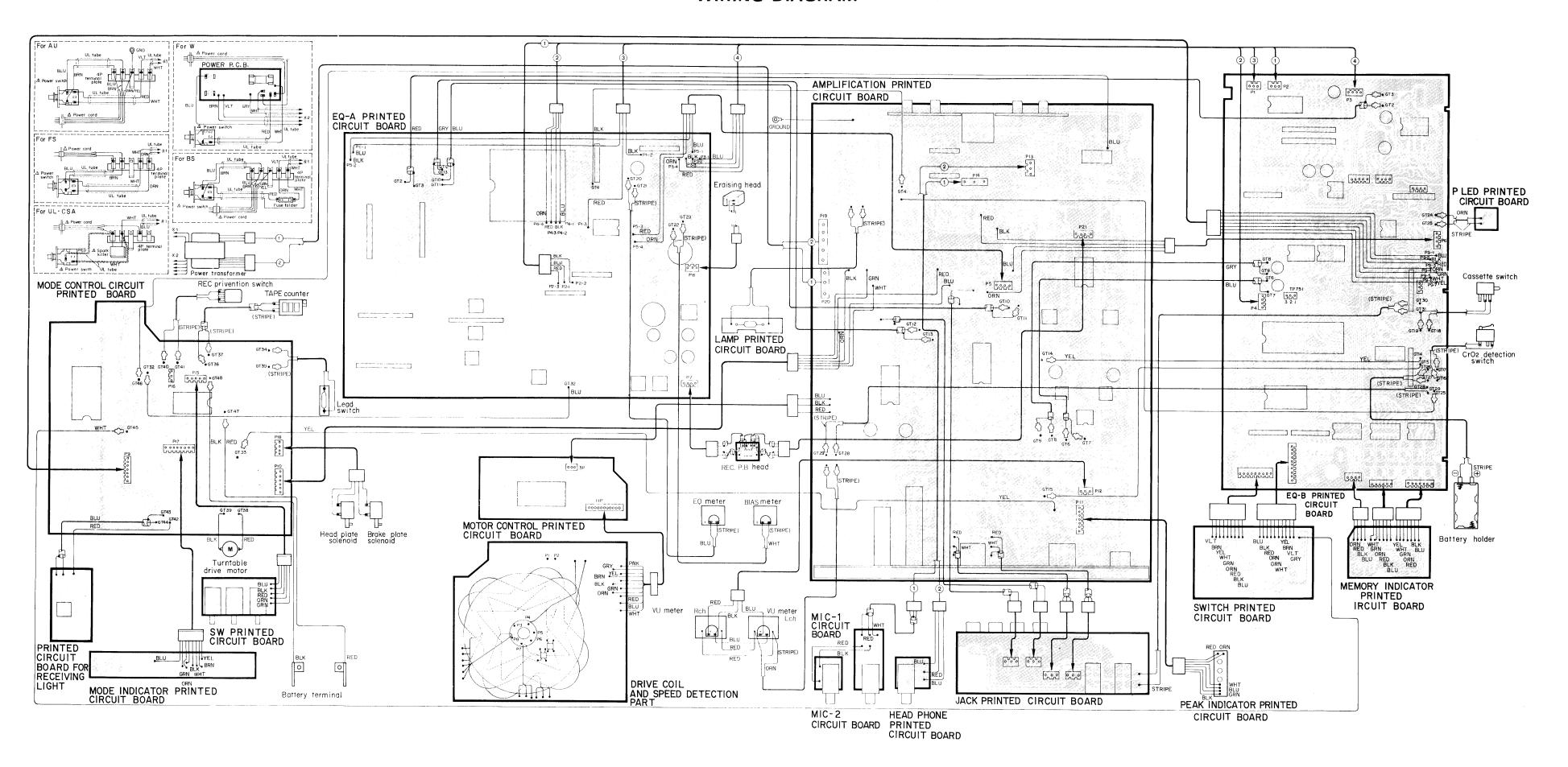

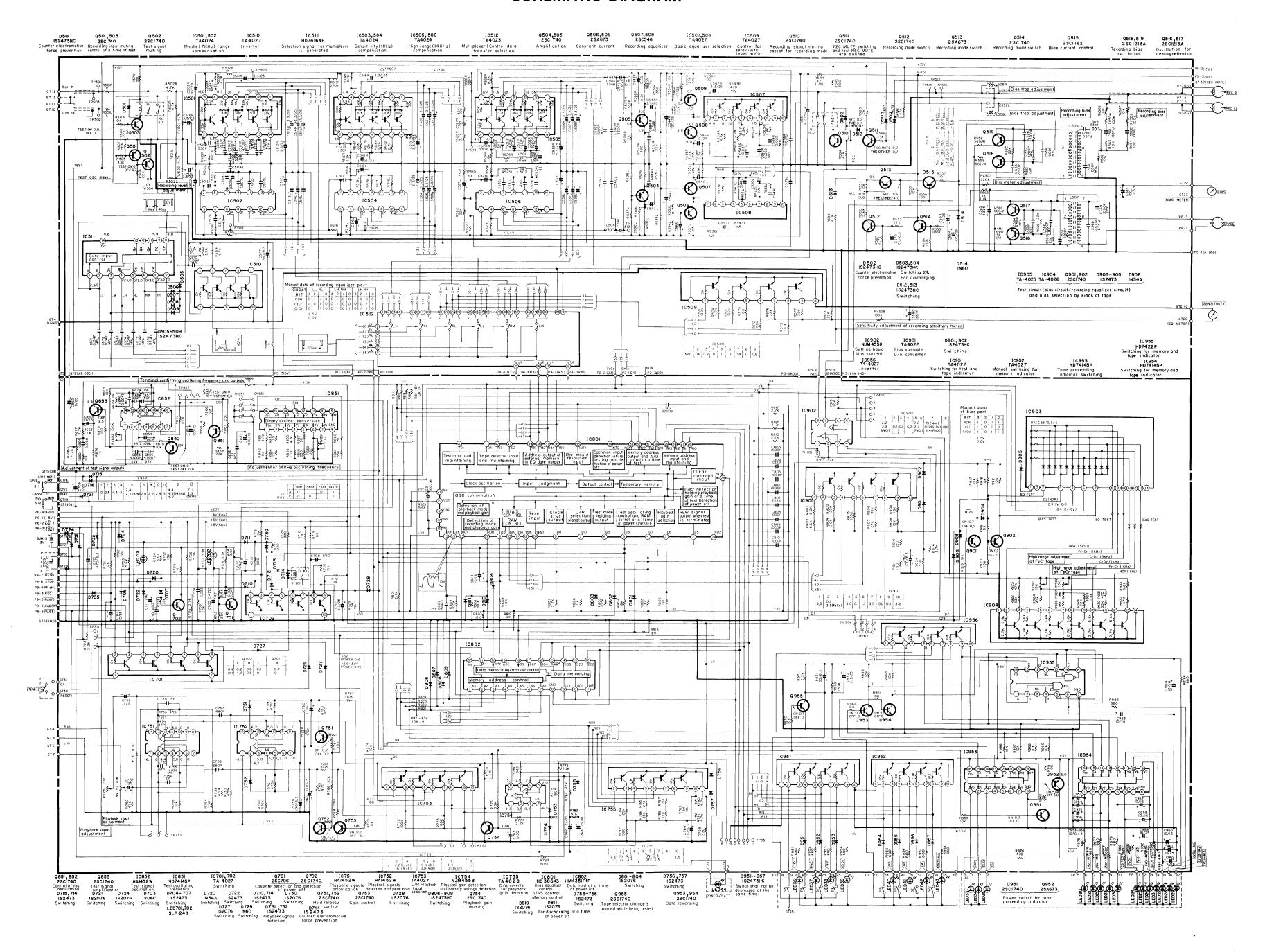

This service manual only shows the Schematic diagram, Circuit board diagram and Wiring diagram.

We will issue the completely service manual including

We will issue the completely service manual including Technical informations, Adjustments, Exploded views and Replacement parts list.

### STEREO CASSETTE TAPE DECK

April. 1979

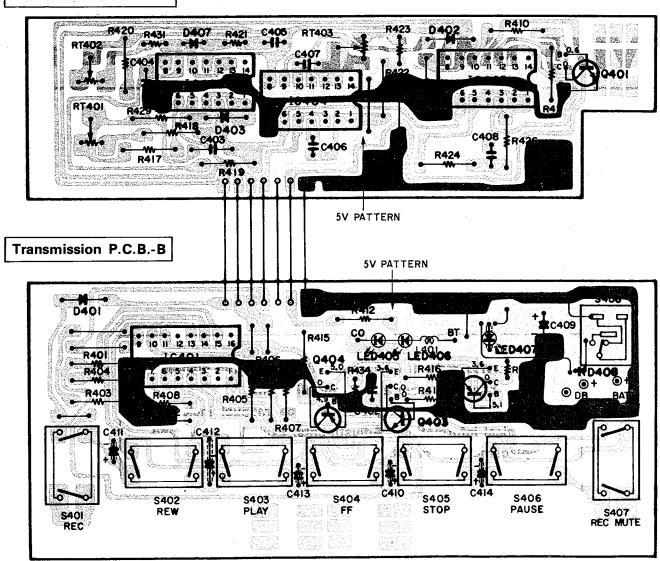

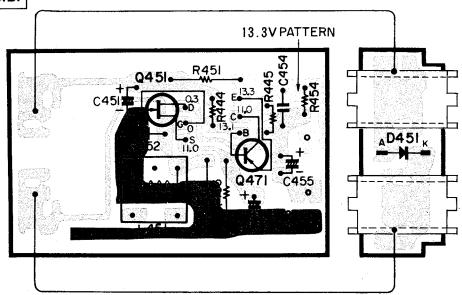

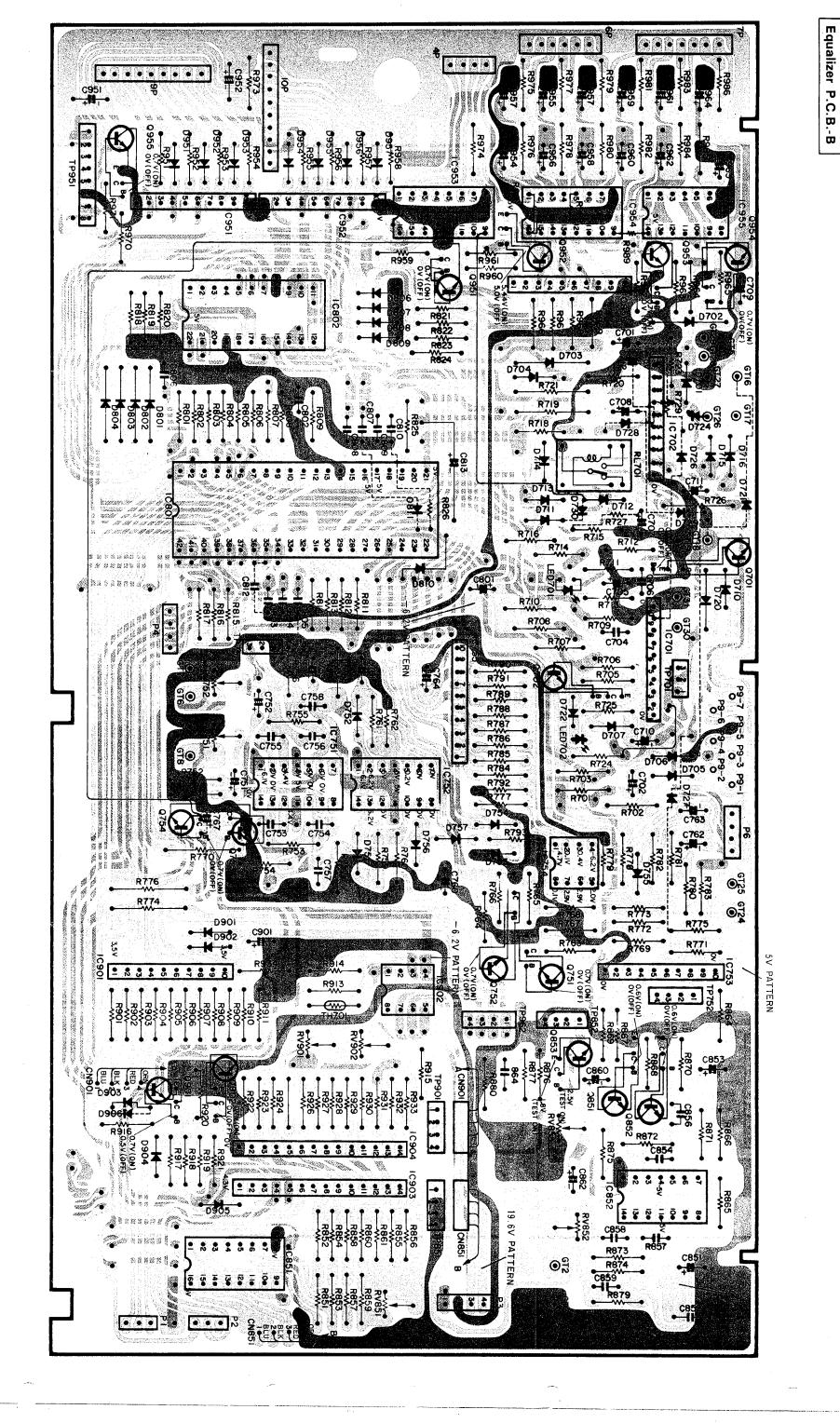

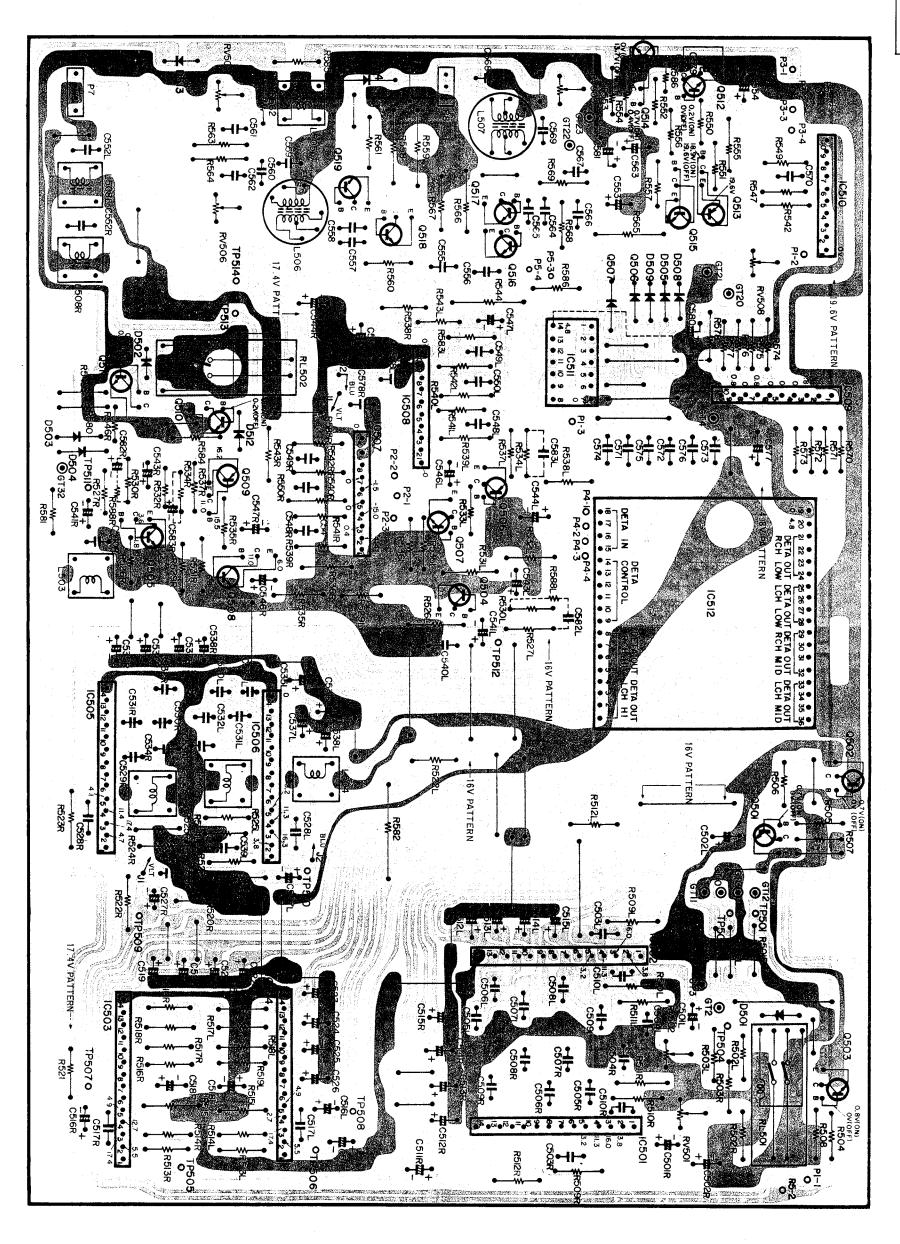

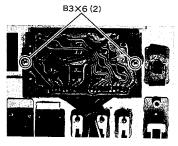

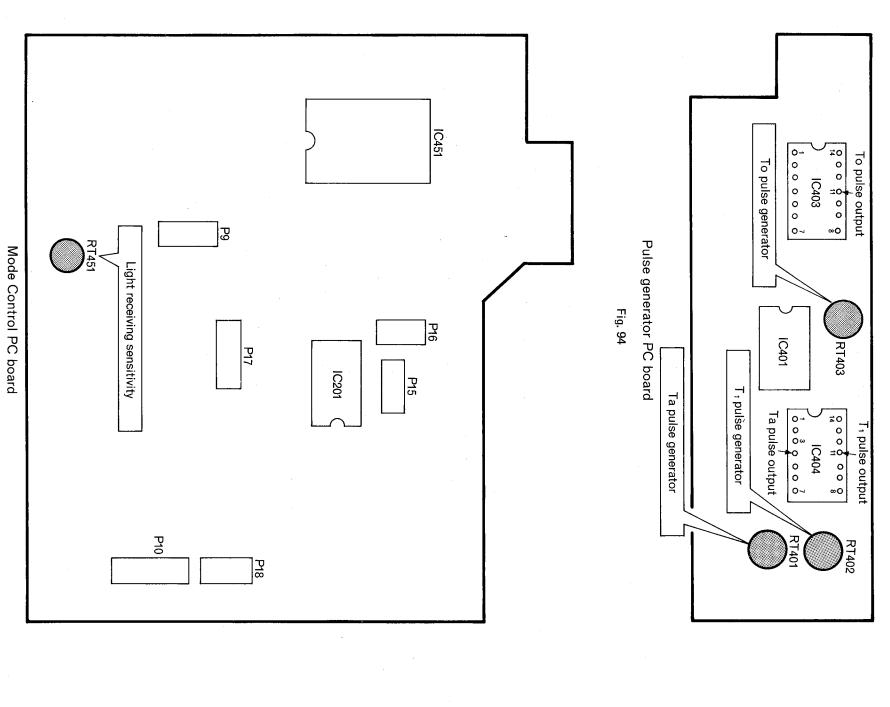

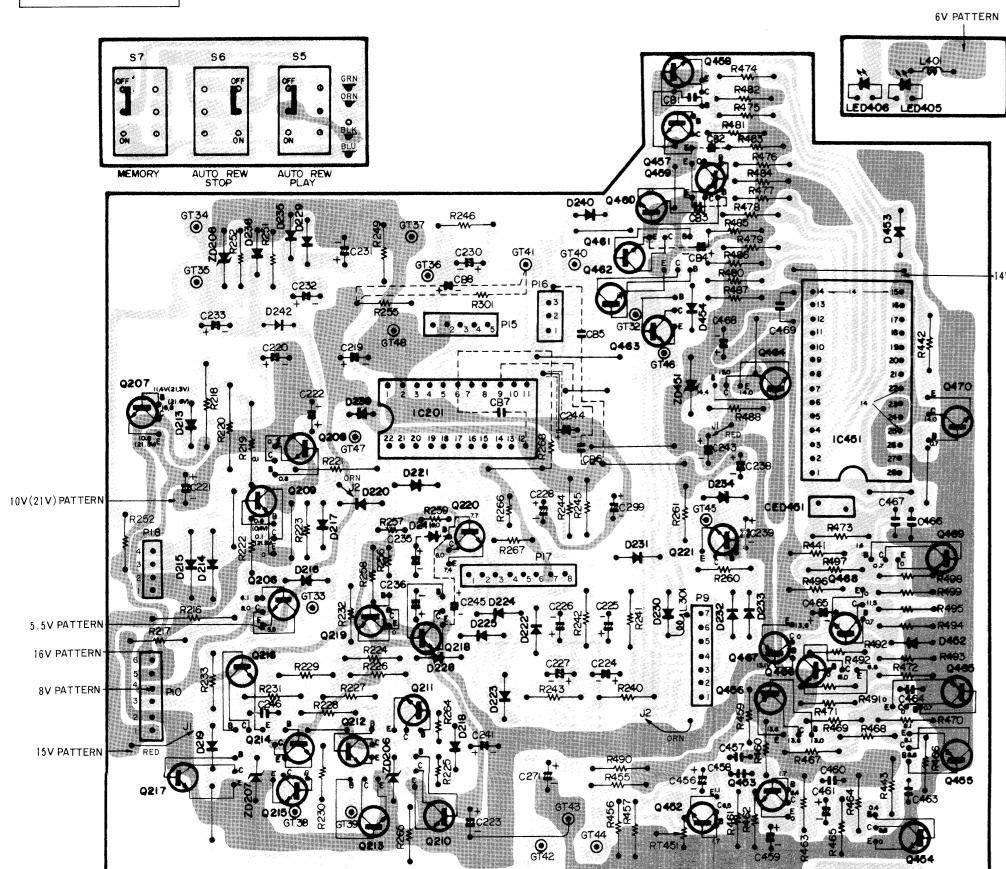

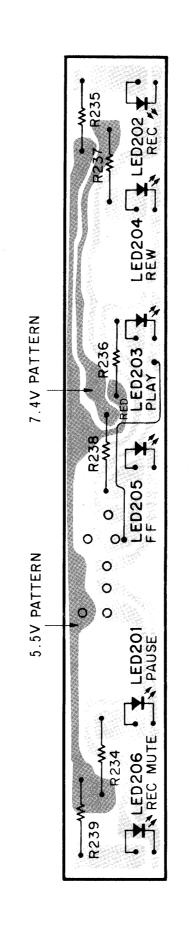

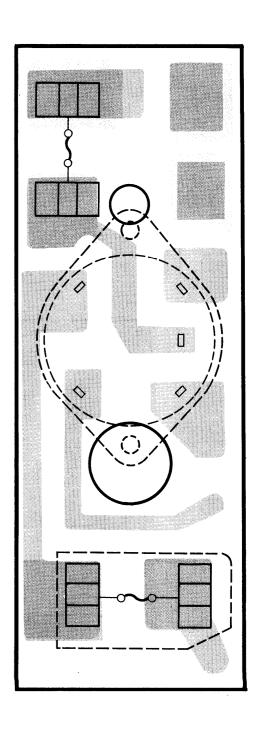

### **CIRCUIT BOARD DIAGRAM**

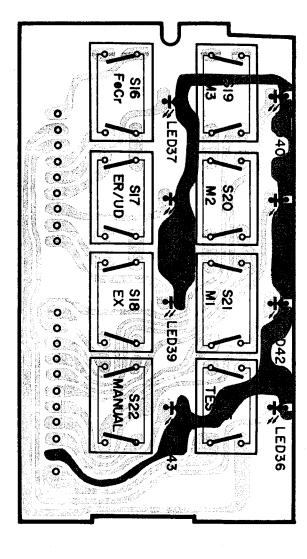

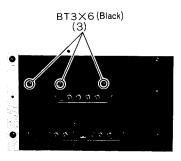

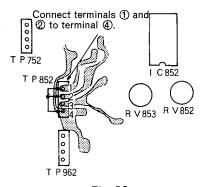

### Transmission P.C.B.-A

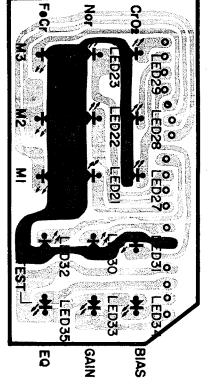

### Light Receiving P.C.B.

ATRS/Memory Indicator P.C.B.

Switch P.C.B.-B

o o

၀ ၀

စ ဥ ဋ

\_\_w\ ∕R32L

아 <mark>원 열</mark> ၀ 등 급

0 0

0

S23 RESET

$\mathbf{0}_{j}$

J5R

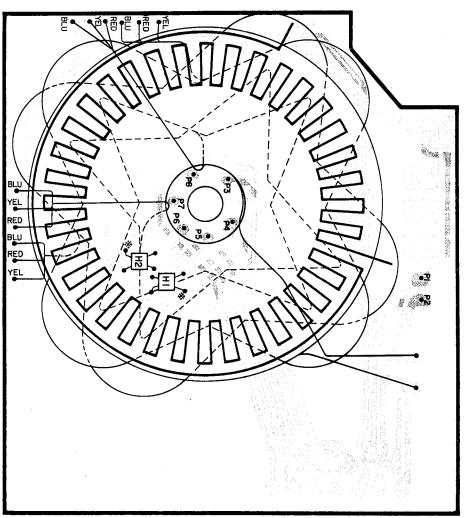

DD Motor Drive/Speed Detection P.C.B.

● (35) ● (35) ● (45) ● (45) ● (45) ● (45)

**⊕**0/√

●4.0 ●0.0 ●1.0 ●1.0 ●1.0

3.0 5.0 1.70 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.00 0.

CONNECT THE HOLE TERMINAL

TO THE \*\* PATTERN THAT

THE TERMINAL ON THE RED

POINT SIDE SHOWS IN THE

PRINTED CIRCUIT BOARD.

DD Motor Control P.C.B.

D-5500

- 10 -

-5-

- 6 <u>|</u>

### **TECHNICAL INFORMATION OF ATRS**

### 1. Operation and Description of Each Mode

| Page                         | 18                                                                                                                                                                                 | 10<br>37                                                                                                                                                                                                                                                                                                                                                                                                                                                    | L 4 1 8 1                                                                                                                                                                                                                   | 12<br>13<br>20<br>21<br>20<br>20<br>27<br>16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12<br>13<br>14<br>16<br>22<br>33<br>33<br>33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12 81                                                                     |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Description Description item | <ol> <li>Preservation of power turn off time<br/>data.</li> </ol>                                                                                                                  | <ol> <li>Initial reset at power-on.</li> <li>Stop and reset circuits in remote control section.</li> </ol>                                                                                                                                                                                                                                                                                                                                                  | <ol> <li>Cassette detection circuit</li> <li>Stop signal generator circuit</li> <li>Data preservation at power-off</li> </ol>                                                                                               | <ol> <li>Tape selector selection</li> <li>Memory selector</li> <li>Recording/playback circuit outline</li> <li>Gain control circuit</li> <li>Playback high frequency range compensation circuit</li> <li>Data transfer circuit in recording equalizer section</li> <li>Recording bias circuit</li> <li>Memory indicator circuit</li> <li>Battery alarm circuit</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Test stop circuit     Test selection     Test data transfer to memory     Stop signal generator circuit     Memory indicator circuit     Test-in-process indicator     Playback gain detector circuit     Test signal generator circuit     Tape length transported detector circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Power-off detection     Data storage at power-off                         |

| Deck operation               | * The status (tape/memory position) immediately before the power is turned off and data obtained by tests are moved to an external memory (IC802) which is backed-up by a battery. | * The microcomputers in the remote control section and main control section (IC451 and IC801) are maintained in the reset state until the power supply is stable. At the same time, the stop signal is generated in the remote control section to prevent error operations at the beginning of power-on and the amplifier section is muted.  * After the reset is released (the stop signal is removed), data is moved in from the external memory (IC802). | * The mechanism control section is forced into the stop mode.  * The tape selector is switched to the NOR position after reset.  * Only the memory indicators of memory registers containing data (M1 – M3 and TEST) light. | * For CrO2 tape, the CrO2 tape position is automatically selected, and the tape selector is automatically switched to NOR for other tapes.  * The memory position selected before power-off is selected if it contains data, or the MANUAL mode is selected; i.e., memory registers M1 — M3 are not held unless they contain data.  * Data from the selected memory register is sent as time-shared data to the equalizer section and continuously to the bias section to control gain.  * The voltage of the back-up battery is compared with a reference voltage. If the battery voltage is higher than or equal to the reference voltage, an indicator which functions as a power indicator is continuously lit: if the comparison finds that the voltage of the back-up battery is lower than the reference voltage, the indicator flashes to battery alarm. | * The external signal input is cut off and the test signal from the internal oscillator is input to the recording equalizer circuits (low, medium and high frequency ranges).  The oscillation signal is charged over for each test circuit, and recorded and played back to detect the gain in the playback gain detector circuit to obtain optimum equalization and bias values. The tests are performed in the following sequence:  1. Sensitivity 2. Bias 3. Sensitivity 4. Medium range equalization 5. High range equalization  * Approx. 20 sec are required for all the tests.  * Changing the tape selector is inhibited during the test.  * If the mode is changed (if any button other than REC/PLAY is pushed), the test stops.  * The length of tape transported from the beginning of the test to the completion of the high frequency range equalization test is measured.  * If a tape is determined to be unsuitable by the test, the test is stopped and the test indicator flashes.  * When the high frequency equalization test is completed, the REW signal is issued and the tape is rewound to the test start point.  * After the test completion, the test data is transferred to the external memory when the test button and one of the memory buttons are pushed simultaneously. | * When power-off is detected, data is transferred to the external memory. |

| Deck status                  | Power-off                                                                                                                                                                          | Immediately<br>after power on                                                                                                                                                                                                                                                                                                                                                                                                                               | Cassette<br>Holder<br>Open                                                                                                                                                                                                  | Cassette Holder Closed or Operation State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Power O State                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Immediately<br>after<br>Power-off                                         |

### 2. Initial Start Circuit when the power is switched ON

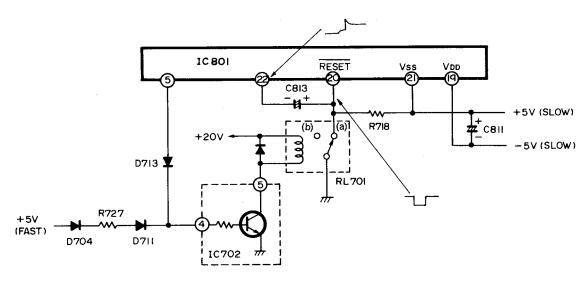

Fig. 3

### 1) Operation when power is switched OFF

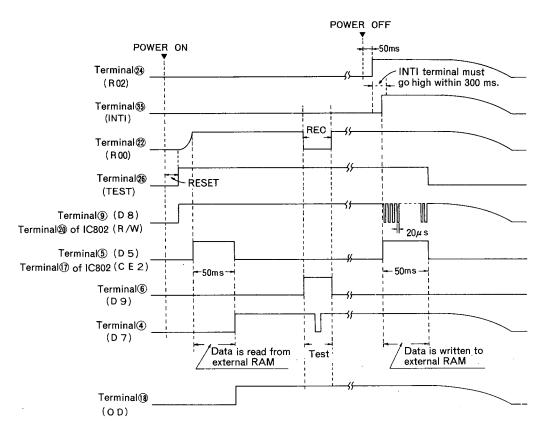

When the power is turned on, microcomputer IC801 transfers the status immediately before power-off and other storage data from the external RAM and operates on the basis on this data. The data transfer from the external RAM is performed by the program start section of the microcomputer. To ensure that the program is started from the beginning when the power is turned on, an initial reset circuit is provided. Three powers supplies are provided by this circuit with different rise times.

- (A) + 5V (FAST)

- B + 5V (SLOW) and -5V (SLOW)

- C + 20V

Though IC702 enters the operation state when the +5V (FAST) supply rises, contact (a) of relay (RL701) is closed since the +20V supply has not yet risen. Then, the -5V (SLOW) and +5V (SLOW) supplies rise to be fed to the microcomputer which enters the operation mode at this time. Since relay contact (a) is closed at this time, however, terminal (20) of IC801 is at low level (the microcomputer is in the reset state when this terminal is at low level), the microcomputer is reset. The subsequent rise of the +20V supply actuates the relay and contact (b) is closed to supply the high level to terminal (20) of IC801 and the reset is removed. The microcomputer checks the voltage at terminal (22) and starts operating the from biginning of program when terminal (22) is at high level.

### 2) Operation immediately after power-off

When the power is turned off, the relay is actuated (contact (b) is closed) to prevent resetting before the microcomputer data has been transferred to the external memory (IC802). Terminal (5) of IC801 goes to high level after detecting that power is turned off to perform data transmission to the external RAM and keep IC702 in the operating state.

### 3. Power-off, Cassette and Stop mode stop detection

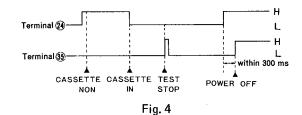

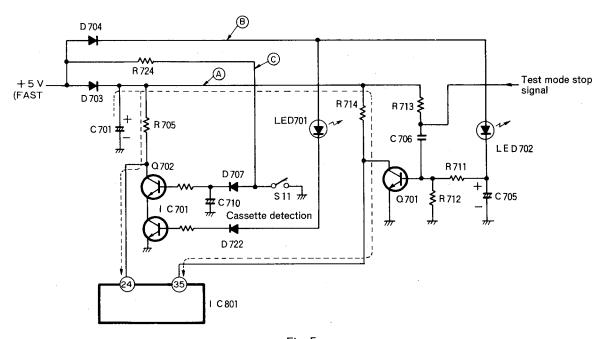

Terminals (24) and (35) of the microcomputer (IC801) detects power-off, whether a cassette is loaded and test mode stop by changes in level as shown in Fig. 4.

Fig. 5

### 1) Power-off detection

When the power is turned off, the external memory (IC802) is operated by the batteries and data stored in the internal memory of the microcomputer is transferred to the external memory and held there. When the power is turned off, this is detected immediately, and the data is transferred to the external memory before an electrolytic capacitor is discharged. The microcomputer is provided with a program that detects power-off when terminal (35) changes from low to high 300ms after terminal (24) changes from low to high. The following circuit is provided so that this program takes effect.

The +5V (FAST) supply is switched by D703 and D704 as shown in the figure and held by C701, C705 and C710. The +5V (FAST) supply is further divided into the three supplies (A), (B), and (C). Their voltages fall in the order of (B), (C) and (A) when the power is turned off according to their time constants. Since the voltages of lines (B) and (C) fall first, IC701 and Q702 are cut off and the voltage at C701 is fed to terminal (24) of IC801 through R705 to change it from low to high. Then, the discharge from C705 through R711 and R712 causes Q701 to be cut off so the voltage of C701 is fed to terminal (35) of IC801 through R714.

With high level at both terminals (24) and (35), IC801 detects power-off. In order to avoid errors due to the instantaneous disconnection of power, the level change at terminal (35) is tested later than terminal (24).

### 2) Cassette detection

A cassette detection function is provided to reset the tape selector when the cassette tape holder remains open for 360ms or longer, detecting a tape change (the NOR. position is selected after reset).

Opening the cassette tape holder causes S11 to be opened which in turn cuts off Q702 to feed the high level of +5V supply (A) to terminal (24) of IC801 through R705. At the same time, the mechanism section is forced into the stop mode until the cassette tape holder is closed.

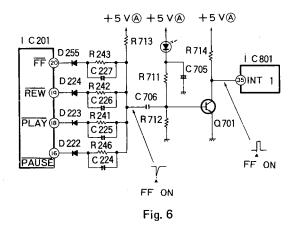

### 3) Test mode stop detection

Changing the mode during testing causes operation of the mechanism to be stopped and the test mode stop instruction to be executed by the microcomputer.

If the mode is changed (if any operation button is pushed) during testing, the output terminal of IC201 corresponding to the operation button pushed becomes low. If the FF operation button is pushed, terminal (20) of IC201 becomes low and a charging current flows to C227 through R713 and D225 until C227 is fully charged. At this time, C706 is discharged through C227, and the voltage change at the junction of R713 and C225 is fed to the base of Q701 through C706, cutting Q701 off which generates a positive pulse at terminal (35) of IC801. The microcomputer detects this pulse and stops the test.

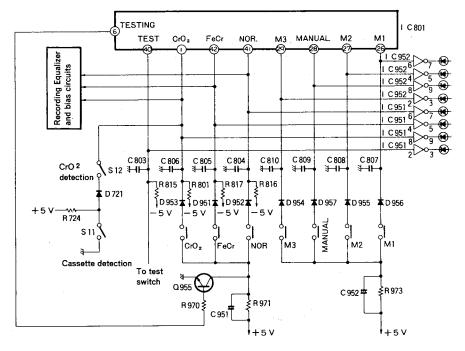

### 4. Tape selector/Memory selection

Fig. 7

### 1) Tape selector selection

Pushing a desired tape selector button causes high level to be applied to the microcomputer terminal associated with the button. The microcomputer detects this high level and, after checking that no other tape selector button has been pushed, holds the terminal at the high level. This high level signal is used to control the electronic switches in the recording equalizer circuit, recording bias circuit and the playback equalizer circuit and these circuits supply data giving the basic operation characteristics in accordance with the tape selected by the selector button. The high level signal also lights the associated tape indicator.

When a CrO<sub>2</sub> tape is used, it is detected whether the CrO<sub>2</sub> detection tabs are present or not on the cassette half and the CrO<sub>2</sub> position is automatically selected. For other tapes, however, the NORMAL position most frequently used is selected by a microcomputer program in the clear state since the automatic detection other types of tape impossible.

If the power is turned off without the cassette tape holder being opened, the selector position immediately before the power is turned off is preserved.

Tape selection is inhibited during testing. Since Q955 is on

### 2) Memory Selection

the same time, the contents of the selected memory are sent out with time-sharing to the recording equalizer When one of the compensation data selection button switches M1 through M3, and MANUAL is pushed, the high contains data corresponding to this terminal, holds the signal and, after checking with the switch pushed. The microcomputer detects this level is applied to the microcomputer terminal associated terminal, the associated memory indicator is lighted, and at terminal at the high level. With this high level signal at the that the external memory

section and continuously to the recording bias section.

## 5. Test Mode Selection

data already stored by a previous test is selected. If play-In order to prevent any test operation due to an erroneous operation, the selected test is started when the unit enters the leader tape section is tested, the test is stopped and the test indicator flashes. medium frequency range test because an unsuitable tape or back gain cannot be determined by the sensitivity test or started until the test data is stored in the memory or until the test mode. The test indicator lights from when a test is the tape transport mode after the recording mode is held in

circuit in this unit: The PLAY and REC outputs of IC201 The record/playback mode is detected by the following

핂

§R 701

control Q221 through an OR circuit composed of D233

signals are correct, and it is on in the other modes. If the ing the record and playback signals at terminals (22) and (23). unit is not in the record/playback pause mode by examinat the high level and starts the test after checking that the puter. At this time, the microcomputer holds terminal (40) test switch is set ON in the record/playback mode, a high Q221 is cut off when both the record and playback mode level signal is applied to terminal (40) of the microcom-

# 6. Test Data Transfer to Memory

D-5500

D-5500

Q221 returns to the on state when the test is completed to external started is applied instead. the voltage across C239 which was charged when the test remove the high level signal supplied to the test switch and memory button (M1 - M3) are pushed simultaneously. The data obtained from the test is transferred to the memory when the TEST button and desired

If the desired memory button and TEST button are pushed

simultaneously, since terminal (40) of the microcomputer is detected at this terminal after the reset, the microcomthen checks the level of this terminal again. If the high level was set to the high level when the test was completed, the microcomputer resets terminal (40) to the low level and transfers the data to the selected memory. puter determines that the TEST button is pushed, and

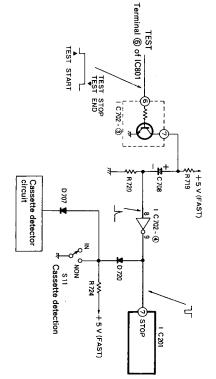

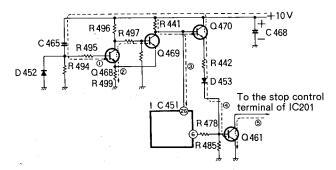

# 7. Stop Signal Generator Circuit

Fig. 9

The stop signal is automatically generated in the following

switches to NON and the stop signal is generated until

cassette detection switch (S11) as shown in Fig. 9

holder is opened (see the explanation on the cassette elapse of a predetermined time after the cassette

circuit is provided to detect tape replacement by the the cassette holder is closed. The cassette detector

detector circuit).

R815

(D 1)

- 2 ω When no playback signal is detected because an unsuitable tape or leader tape section is tested.

- applied

REW or PAUSE operation), the connection of the while the mechanism is in action (during the FF, When the cassette holder is open, or it is opened

$\widehat{\Xi}$ When a test terminates and the tape is rewound to the

this voltage is shaped and inverted by IC702 to be signal is also generated when terminal (8) of IC702 control section. The output at terminal (8) of IC702 pulse with a larger width is generated in the remote circuit when power is turned on, and another stop control IC(IC201). A pulse is thus generated by this When the cassette holder is open. becomes low by discharging C708 immediately after unsuitable or a mode change is performed. The stop the rise of the +5V (FAST) supply. The waveform of produced across R720 until C708 is fully charged by When the power is turned on, a voltage drop is terminates, or is stopped because the tested tape is is held at the high level by the test mode signal tion as when power is turned on. (terminal (6) of IC801) during testing; until the test C702 (terminal (8) becomes on by the same operato the stop input terminal of the mode

Fig. 8

1 C 701

(R01)

### . Battery Alarm Circuit

The status immediately before power is turned off and test data are transferred to the external RAM (IC802) which is put in the operating state by the batteries at this time to preserve the data. A battery alarm circuit is provided to check if the output voltage of the battery is below a predetermined value when power is turned on.

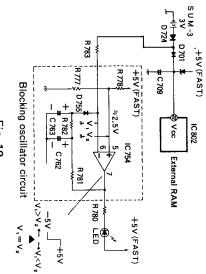

A blocking oscillator circuit is formed by IC754 and the peripheral circuits as shown in Fig. 10.

The voltage at terminal (5) of IC754 is set at approx. 2.5V divided by R778 and R777. This reference voltage and the output voltage of the batteries are compared.

The output of IC754 is negative when the voltage at terminal (6) (V1) is higher than the reference voltage (V2), and positive when V1 is lower than V2.

Since the output of IC754 becomes negative when the battery voltage rises over the reference voltage, the LED lights and functions as the power indicator.

Since the output of IC754 becomes positive when the battery voltage drops below the reference voltage, the LED goes out and capacitors C762 and C763 are charged. When the voltage at the positive terminal of C763 rises to the refference voltage (V2), the IC output reverses and the LED comes on and capacitors C762 and 763 are discharged. The LED flashes as this action is repeated.

### 9. IC HD7414P

HD7414P is a BCD to decimal decoder IC which is used obtain a decimal output from 4-digit binary data (BCD). The output corresponding decimal values 0 to 9 is 0, or low. BCD code input A is the least significant bit (LSB) and input D is the most significant bit (MSB). The input and output codes are shown in the following table:

Fig. 10

| $\neg$     | <del>2</del> ] |   |   |   |   |   | _ |   | —т       | ٦           | -             |

|------------|----------------|---|---|---|---|---|---|---|----------|-------------|---------------|

|            | SS D           | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0        | <del></del> | -             |

| Input      | C              | 0 | 0 | 0 | 0 | 1 | Ц | 1 | ۳        | 0           | 0             |

| Ħ          | В              | 0 | 0 | Н | 1 | 0 | 0 | 1 | ₩.       | 0           | 0             |

|            | (LSB)          | 0 | 1 | 0 | 1 | 0 | 1 | 0 | ᅵ        | 0           | ר             |

|            | Ϋ́             | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1        | 1           |               |

|            | Υ,             | ₩ | 0 | 1 | 1 | 1 | 1 | 1 | 1        | 1           | 1             |

|            | Υ2             | 1 | 1 | 0 | 1 | 1 | 1 | 1 | Ţ        | 1           | 1             |

|            | Ya             | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1        | 1           | 1             |

| Output     | Y              | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1        | 1           | Н             |

| it         | Y <sub>6</sub> | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1        | 1           | 1             |

|            | βЧ             | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1        | 1           |               |

|            | Ye Y7          | 1 | ۳ | 1 | 1 | 1 | 1 | 1 | 0        | 1           | Н             |

|            | Y <sub>8</sub> | 1 | 1 | 1 | 1 | 1 | 1 | 1 | <b>ب</b> | 0           | ш             |

| 1 <b>I</b> | Y              |   |   |   | Ī |   |   | l | ١        | T           | $\overline{}$ |

Table 1

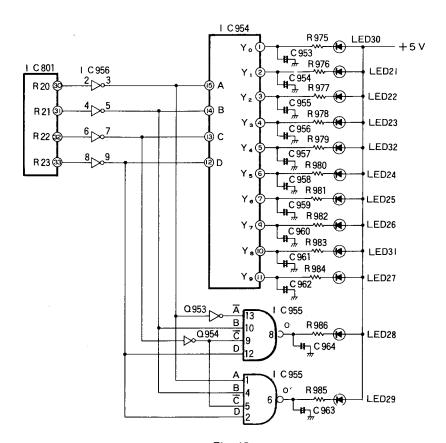

# 10. Memory Indicator Circuit

The microcomputer can store and maintain a maximum of four sets of test data in memories M1 to M3 and TEST for up the three tape selector positions. The test data is transferred to a intended memory by simultaneously pushing the desired memory button and TEST button. If data is already contained in the selected memory, the old data is replaced by the new data. Twelve (12) LEDs are arranged in a matrix form as shown in Fig. 11 as external displays for the contents of the four memories M1 to M3 and TEST.

Fig. 11

are "0000" to "1001", i.e., decimal 0 to 9, inverters  $\Omega 953$  and  $\Omega 954$ , and a dual 4 input NAND gate are added to obtained. Unused LEDs flash each time the bias value varies "1011". Table 2 shows the data code used to light the circuit is provided between the microcomputer (IC801) and control data increases. playback gain changes from "0000" until the peak value is varied by one step, the control data used to detect the converter control signals. Thus, each time the bias value is form a logic circuit that decodes input data "1010" and decoder IC(IC954). Since the decimal outputs from IC954 are inverted by IC956 and fed to the BCD to decimal circuit. The 4-bit signals at terminals (30) to (33) of IC801 the twelve LEDs. Fig. 12 shows the memory indicator the 4-bit control signals, a BCD (binary) to decimal decoder microcomputer. To encode information bits 0 to 12 into flashes LEDs not in use to indicate that a test is in progress. program displays the contents of the external memory and capacitors C953 to C962. During testing a microcomputer The contents of a memory register within the microcombias point more, LEDs flash since the variations of the by one step. As the control data value gets close to the peak in common with the test time playback gain detection D/A LEDs. The 4-bit memory indicator control signals are used LEDs are controlled by four (4)-bit control signals from the puter are checked by fine-sharing, output and held by latch

| 32          | 30          | 31          |

|-------------|-------------|-------------|

| <b>\$</b>   | <b>©</b> 22 | <b>©</b> 27 |

| <b>©</b> 25 | <b>©</b> 23 | <b>©</b> 28 |

| <b>8</b> 26 | <b>©</b> 23 | <b>©</b> 29 |

Numbers show symbol No. of LEDS.

(Refer to table 2)

Fig. 12

| Microcomputer<br>Output IC954 I |      |      |     | Int | out | : IC954 Output |   |    |     |    |    |     |     | IC955- ②       |     |    |                |   |                         | ICS | 955 | Refer to Fig. 12 |   |   |   |   |    |         |

|---------------------------------|------|------|-----|-----|-----|----------------|---|----|-----|----|----|-----|-----|----------------|-----|----|----------------|---|-------------------------|-----|-----|------------------|---|---|---|---|----|---------|

| R <sub>23</sub>                 | R 22 | R 21 | R20 | D   | С   | В              | Α | Υo | Y 1 | Υ₂ | Υз | Y 4 | Y 5 | Υ <sub>6</sub> | Y 7 | Υs | Υ <sub>9</sub> | D | $\overline{\mathbb{C}}$ | В   | Ā   | 0                | D | C | В | Α | o′ | LED lit |

| 0                               | 0    | 0    | 0   | 1   | 1   | 1              | 1 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 1 | О                       | 1   | 0   | 1                | 1 | О | 1 | 1 | 1  |         |

| 0                               | Ο    | 0    | 1   | 1   | 1   | 1              | 0 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 1 | 0                       | 1   | 1   | 1                | 1 | 0 | 1 | 0 | 1  | -       |

| 0                               | 0    | 1    | 0   | 1   | 1   | 0              | 1 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 1 | О                       | Ο   | 0   | 1                | 1 | О | 0 | 1 | 1  | _       |

| 0                               | Ο    | 1    | 1   | 1   | 1   | 0              | 0 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 1 | О                       | 0   | 1   | 1                | 1 | О | О | 0 | 1  | _       |

| 0                               | 1    | 0    | 0   | 1   | 0   | 1              | 1 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 1 | 1                       | 1   | 0   | 1                | 1 | 1 | 1 | 1 | 0  | LED29   |

| 0                               | 1    | 0    | 1   | 1   | 0   | 1              | 0 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 1 | 1                       | 1   | 1   | Ο                | 1 | 1 | 1 | 0 | 1  | LED28   |

| 0                               | 1    | 1    | 0   | 1   | 0   | 0              | 1 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 0              | 1 | 1                       | 0   | 0   | 1                | 1 | 1 | 0 | 1 | 1  | LED27   |

| 0                               | 1    | 1    | 1   | 1   | 0   | 0              | 0 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 0  | 1              | 1 | 1                       | Ο   | 1   | 1                | 1 | 1 | 0 | О | 1  | LED31   |

| 1                               | Ο    | 0    | 0   | 0   | 1   | 1              | 1 | 1  | 1   | 1  | 1  | 1   | 1   | 1              | 0   | 1  | 1              | 0 | 0                       | .1  | 0   | 1.               | 0 | Ο | 1 | 1 | 1  | LED26   |

| 1                               | Ο    | 0    | 1   | 0   | 1   | 1              | 0 | 1  | 1   | 1  | 1  | 1   | 1   | 0              | 1   | 1  | 1              | 0 | О                       | 1   | 1   | 1                | 0 | Ο | 1 | 0 | 1  | LED25   |

| 1                               | 0    | 1    | 0   | 0   | 1   | 0              | 1 | 1  | 1   | 1  | 1  | 1   | 0   | 1              | 1   | 1  | 1              | 0 | Ó                       | 0   | О   | 1                | 0 | Ο | 0 | 1 | 1  | LED24   |

| 1                               | 0    | 1    | 1   | 0   | 1   | 0              | 0 | 1  | 1   | 1  | 1  | 0   | 1   | 1              | 1   | 1  | 1              | 0 | О                       | О   | 1   | 1                | 0 | Ο | О | 0 | 1  | LED32   |

| 1                               | 1    | 0    | 0   | 0   | 0   | 1              | 1 | 1  | 1   | 1  | 0  | 1   | 1   | 1              | 1   | 1  | 1              | 0 | 1                       | 1   | О   | 1                | 0 | 1 | 1 | 1 | 1  | LED23   |

| 1                               | 1    | 0    | 1   | 0   | 0   | 1              | 0 | 1  | 1   | 0  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 0 | 1                       | 1   | 1   | 1                | 0 | 1 | 1 | 0 | 1  | LED22   |

| 1                               | 1    | 1    | 0   | 0   | 0   | 0              | 1 | 1  | Ο   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 0 | 1                       | О   | О   | 1                | 0 | 1 | О | 1 | 1  | LED21   |

| 1                               | 1    | 1    | _ 1 | 0   | Ο   | 0              | 0 | 0  | 1   | 1  | 1  | 1   | 1   | 1              | 1   | 1  | 1              | 0 | 1                       | 0   | 1   | 1                | 0 | 1 | 0 | 0 | 1  | LED30   |

Table 2

Fig. 13

### 11. Data Storage when power is turned off

This unit is provided with a function that, when the power is turned off the test data is preserved and the existing status (tape selector and compensation data memory positions) is held. (tape selector and compensation data memory positions are not preserved when the power is turned off with the cassette tape holder opened.)

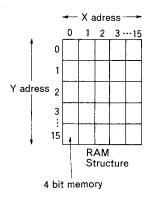

The memory in which data is stored, the data stored in which can be changed and read out is called a RAM (random access memory), and test data in this deck is stored in a RAM. The RAM's contents are preserved as long as the power is supplied. Since the power supply of the microcomputer is removed when the power is turned off, an exclusive RAM is provided outside microcomputer, and immediately after power-off is detected, data is transferred to the RAM whose power supply is maintained by the back-up batteries.

The microcomputer transfers the data to the external memory by execution of a data transfer instruction in which X and Y addresses are selected and the microcomputer is synchronized with the memory as data becomes ready to be transferred.

Static RAM HM435101 (256 words x 4-bits) with low power consumption and a maximum stand-by current of 15 A is used for the external memory (IC802).

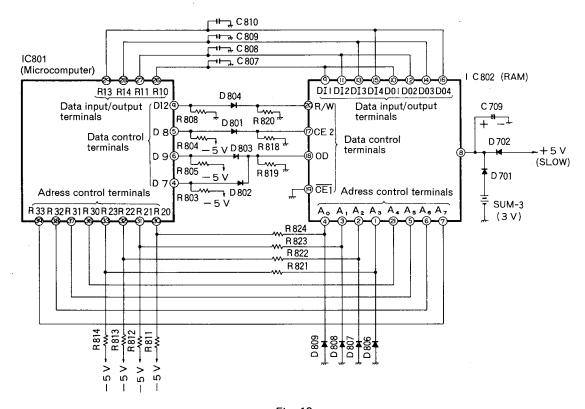

Fig. 14

Since both X and Y addresses run from 0 to 15, 8-bit address lines (4 bits x 2) are required, and since 4-bit data is stored in each address, four data lines are required. Further, 3-bit control lines are necessary as the signal lines between the microcomputer and RAM in addition to the address and data lines so there is a total 15 signal lines. In order to reduce the number of microcomputer terminals needed, the terminals that are used to control the recording equalizer circuit are used as the external RAM control terminals once power-off is detected.

Fig.16 shows the circuit between the microcomputer and the external RAM.

Lines  $A_0 - A_7$  of the external RAM (IC802) are the address lines selected by the microcomputer.  $DI_1 - DI_4$ and  $DO_1 - DO_4$  are the RAM's data input and output lines respectively. The lines for the same bits are connected and used as common input/output lines. The data input/output lines are switched between input and output by control signal OD. When OD is low, the RAM is in the input mode and, when OD is high, the RAM is in the output mode. Control signal R/W controls the data transfer timing between the microcomputer and the RAM. When R/W is high, the microcomputer sends out selected data along the data lines and, when it is low, the external RAM sotres the data on the data lines into the address selected by the microcomputer. Control signal CE allows the data on the data lines to be input to the microcomputer and data to be output along the data lines from the microcomputer. In addition, CE is used to synchronize data transfer between the microcomputer and the external RAM. When no data is being read or written, or when data is stored, this signal is held at the low level. This signal is also used to prevent the initial reset signal generation circuit from operating until data transfer terminates (see the explanation of the power-off time initial reset circuit).

When power is turned on, the data transferred to the external RAM when the power was turned off previously is moved into the microcomputer. This data transfer operation takes place when the reset signal is removed from the microcomputer and terminal (22) of IC801 becomes high. See the timing diagram as shown in Fig. 15.

Fig. 15

Fig. 16

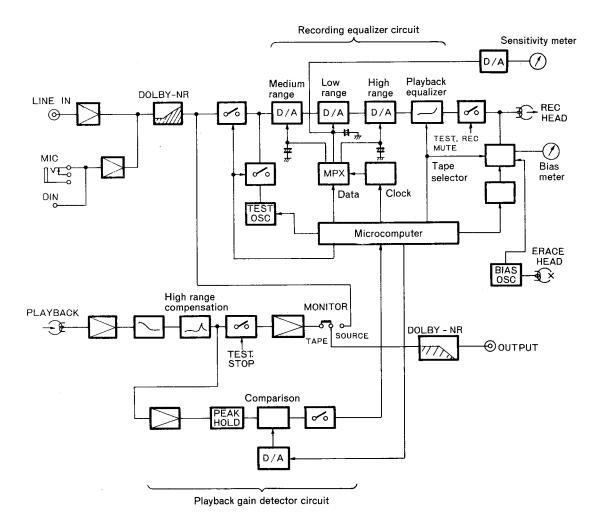

### 12. Recording/Playback Circuit Block Diagram

Fig. 17

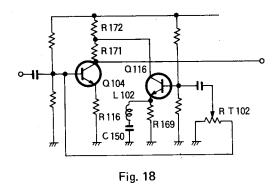

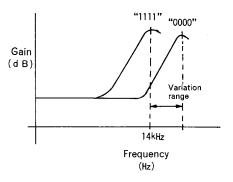

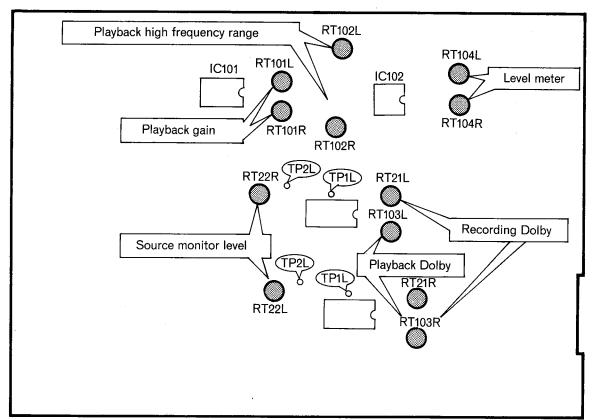

### 13. Playback High Frequency Range Compensation Circuit

This is newly developed circuit used in the D-5500; it compensates for variations in high frequency range due to loss at the playback head because of a non-uniform gap. Principle of Operation

Amplification gain of Q104 (K1) is given by:

$$K_1 = \frac{R171 + R172}{R116}$$

and amplification gain of Q116 (K2) is given by

$$K_2 \doteq \frac{R172}{ZE}$$

where ZE = R169//(ZC + ZL)

$$\begin{cases}

ZC = -j \frac{1}{\omega C_{150}} \\

ZL = j \omega L_{102}

\end{cases}$$

These two amplification gains are added across R172 as shown below assuming the attenuation due to RT102 to be k:

$$K = K_1 + k \cdot K_2$$

=\frac{R171 + R172}{R116} + k \cdot \frac{R172}{ZE}

Thus, the peaking effect in the high frequency range varies as K is changed.

### 14. Gain Control Circuit

The gain of the following circuits is controlled by the microcomputer:

- 1. Low frequency range sensitivity compensation circuit

- 2. Medium frequency range compensation circuit

- 3. High frequency range compensation circuit

- 4. Recording bias fine adjustment circuit

- 5. Recording sensitivity meter control circuit

- 6. Playback gain detector circuit

Data input to or output from the microcomputer is processed as "Hi" and "Lo" binary values, and sizes and values are represented by several binary digits. The voltage and gain, etc. of an amplifier circuit or other analog circuit cannot be directly controlled by these digital values. That is, voltage and gain, etc. must be controlled after the data is converted to a form "understandable" by the respective circuits.

Conversion is done by circuits called digital/analog converters (D/A converter).

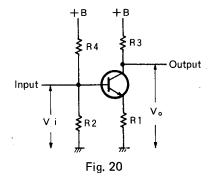

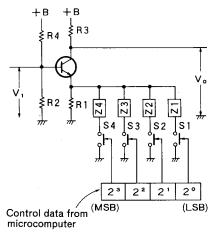

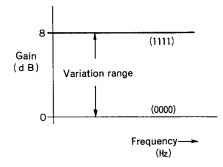

### 1) Principle of D/A converter (4-bit control signals)

An increase of the emitter resistor (R1) in the circuit on the left causes a reduction in gain since the voltage drop across R1 has reverse phase to the input voltage. To apply this principle, impedances Z1 - Z4 are connected in parallel with R1 and Z1 - Z4 are grounded through switches S1 - S4 respectively which are closed by control data from microcomputer as follows:

Fig. 21

Z4: Z3: Z2: Z1 = 1:2:4:8.

S1 is closed when bit 20 is 1.

S2 is closed when bit 2<sup>1</sup> is 1.

S3 is closed when bit  $2^2$  is 1.

S4 is closed when bit  $2^3$  is 1.

A bit is the minimum increment in which data can be represented and four binary digits are output. The bit representing the least significant binary digit is called "LSB" and the bit representing the most significant binary digit is called "MSB".

Fig. 22

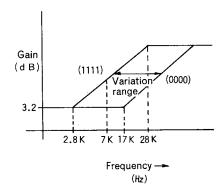

If a 4-bit binary number is increased step by step from "0000" to "1111" (equivalent to decimal "0" to "15") following the above relationship and the input is constant, the gain increases in 16 steps as shown in Fig. 22. As indicated in the figure, the minimum gain is determined by R1 and the variation rate per step is determined by Z4.

Further, by making impedances Z1 — Z4 with pure resistance (R), capacitance (C) and inductance (L), and varying the control data, the gains in specific frequency ranges can be changed.

### 2) When Z1 - Z4 has pure resistance (R)

If the input voltage is constant throughout the frequency range, the output voltage is constant regardless of frequency because the output voltage is divided by pure resistance.

Fig. 23

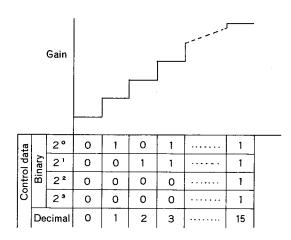

### 3) When $Z_1 - Z_4$ are composed of pure resistance (R) and capacitance

Since capacitance (C) is provided in parallel with resistance (R2), the gain is flat until  $f_1$  at which the composite impedance of R2 and C is equal to R1, or above it, the output is doubled as the frequency is doubled; i.e., the output increases at a rate of 6 dB per octave, since  $X_C$  is inversely proportional to frequency. If C is changed, point  $f_1$  varies for the reason explained above.

Fig. 24

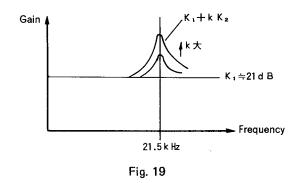

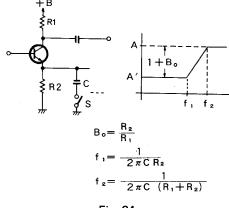

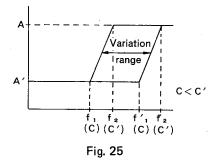

### When Z<sub>1</sub> - Z<sub>2</sub> are composed of resistance (R), capacitance (C) and inductance (L)

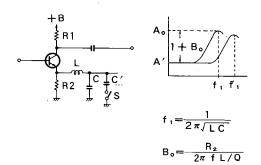

Insertion of a serial resonance circuit composed of L and C in parallel with resistance ( $R_2$ ) causes a steep rise in gain at resonance frequency ( $f_1$ ). If C is changed further, the tuned frequency ( $f_1$ ) varies.

Fig. 26

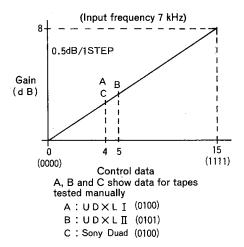

D/A converter consisting of resistors are used in the low frequency range sensitivity compensation circuit, recording bias fine adjustment circuit, and playback gain detector circuit; a D/A converter consisting of capacitors is used for the medium frequency range compensation circuit; and a D/A converter circuit consisting of resistors, capacitors and coils is used for the high frequency range compensation circuit.

### 5) Low frequency range sensitivity compensation circuit

Fig.. 27

Fig. 28

### 6) Medium frequency range compensation circuit

Fig. 29

Fig. 30

### 7) High frequency range compensation circuit

Fig. 31

Fig. 32

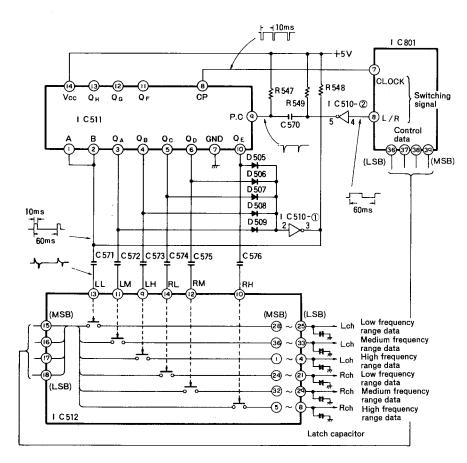

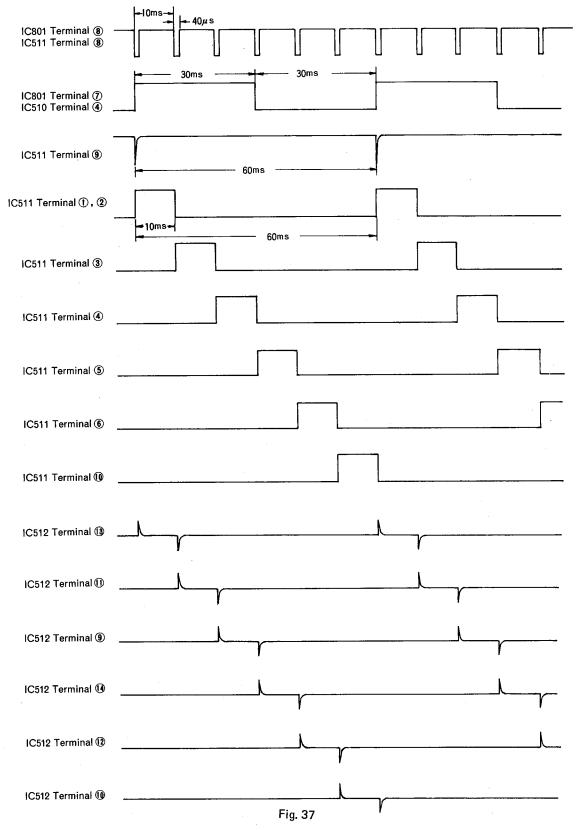

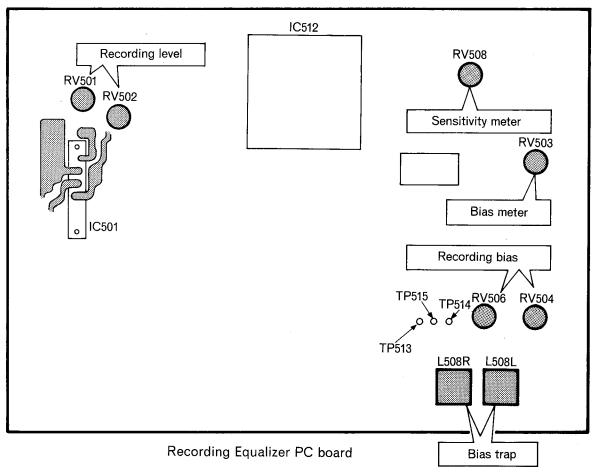

### 15. Data Transfer Circuit in Recording Equalizer Section

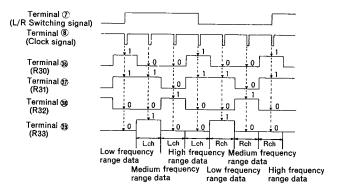

Each of the low, medium and high frequency range recording equalizer sections is controlled by 4-bit binary data, and a total of 24 bits of control data is required for these sections since there are six equalizer circuits including both the L and R channels. These control data signals are controlled by the microcomputer. To lessen the number of input/output terminals of the microcomputer used, each group of 4-bit control signals and 2-bit switching signals are output form the microcomputer using time sharing using a

6-channel multiplexer (IC512).

Fig. 33 shows the data control circuits. The recording equalizer control signals at terminals (36) — (39) of the microcomputer are output in the time sharing made in synchrozation with the switching signals at terminals (7) and (8), and applied to input terminals (15) — (18) of IC512. From there, they are distributed to each recording equalizer circuit by a switching signals produced by IC511.

Fig. 33

### Contents of control data in manual FeCr tape position

Fig. 34

### 1) Shift resistor (IC511)

IC511 is a shift register that converts serial input signals arriving bit serially to bit parallel signals.

Fig. 35

The internal circuit of IC511 is composed of eight (8) RS flip-flop as shown in Fig. 35. When either input A or B is Lo, output  $\Omega_A$  of the first flip-flop does not go Hi if the clock pulse at terminal CP repeats a Hi/Lo transition. When the CP input changes from Lo to Hi with both inputs A and B at the Hi level, output  $\Omega_A$  is set Hi. When the CP input next changes from Lo to Hi, the second flip-flop is set Hi by the same principle, and the subsequent flip-flop operate in sequence as the CP input changes from Lo to Hi.

To reset these flip-flop, the PC terminal is set Lo.

The clock signal as shown in Fig. 35 is applied to terminal (8) of IC511, and the L/R switching signal is applied to terminal (9). The L/R switching signal output from the microcomputer is fed to IC511 through an inverter (IC510) and differential circuit (R547 and C570), and the internal flip-flop are reset by the rising edge of this pulse. Terminals (1) and (2) are input terminals used to control generation of the first output pulse (L ch low frequency range control data switching signal).

Terminals (1) and (2) are connected, and the output of an inverter (IC510) to which flip-flop outputs  $\mathrm{Q}_{A}-\mathrm{Q}_{E}$  are fed to these terminals through OR diodes (D505 – D509). Thus, if any flip-flop output is Hi, the first pulse is prevented since terminals (1) and (2) are held at Lo.

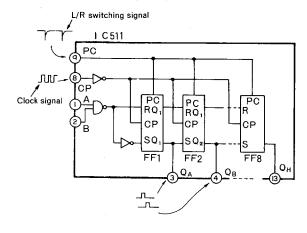

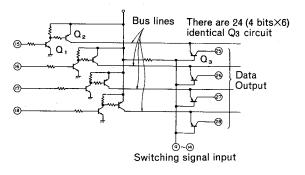

### 2) Multiplexer (IC512)

Fig. 36

The internal circuit of this multiplexer is shown above (Fig. 36). The control data signals from the microcomputer are applied to terminals (15) - (18). When a control data bit (e. g., terminal (15) is 1, Q1 and Q2 conduct, and data signal 1 is output on the bus line. When a negative trigger pulse is input to one of terminals (9) - (14) (e.g., terminal (9), Q3 conducts and the control data signal is sent to the circuit associated with terminal (9). This signal is further maintained by a latch capacitor.

### 3) Operation of data transfer circuit

The output terminals of all the internal flip-flops in IC511 are Lo in the initial state since they are reset by the rising edge of the L/R switching signal. Since all the flip-flop outputs are Lo, the output at terminal (1) of IC510 is Hi and terminals (1) and (2) of IC511 are Hi. The rising edge of the clock signal at terminal 8 sets, the first flip-flop to 1 and output terminal (3) becomes H. This output goes through D509, is inverted by IC510 and produces the Lo level at terminals (1) and (2). Thus, a Hi pulse is generated at terminals (1) and (2) of IC511 from the rise of the L/R switching signal to the rise of the clock signal. This pulse is fed to terminal (13) of the multiplexer (IC512) through capacitor C571. At this time, the L ch low frequency range circuit control data is input to terminals (15) - (18) of IC512 so that the data from output terminals (25) - (28) is transferred when the pulse falls. This data is maintained by latch capacitors to control the low frequency range compensation circuit. The subsequent operations are performed by the switching pulses generated by the identical principle to allow the proper control data routings. The control data is transferred in the following sequence:

- 1. L ch low frequency range compensation circuit

- 2. L ch medium frequency range compensation circuit

- 3. L ch high frequency range compensation circuit

- 4. R ch low frequency range compensation circuit

- 5. R ch medium frequency range compensation circuit

- 6. R ch high frequency range compensation circuit

When the data transfer to all the above circuit is completed, the flip-flops are reset by the rising edge of the L/R switching signal, and the same operation is repeated.

The recording equalizer control data is output from the

microcomputer 5 ms before the fall of the clock (at which time data is read by each circuit), so that the data is stored at its middle to prevent data for another circuit from being read by mistake.

### 4) Switching signal generation timing diagram

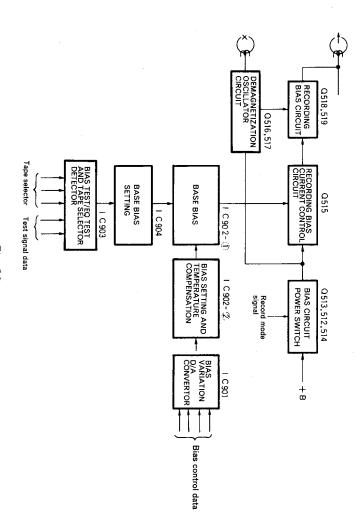

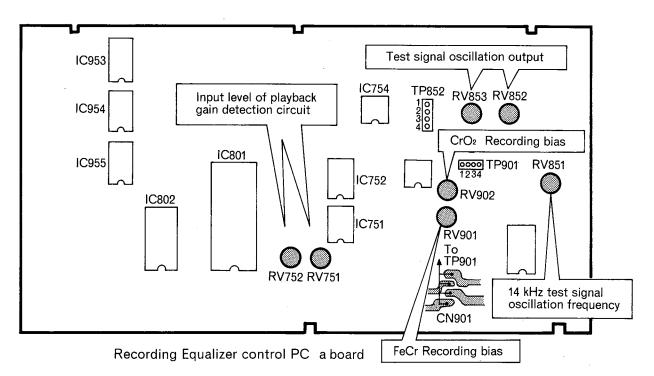

## 16. Bias Oscillator Circuit

Fig. 38

### 1) Oscillator circuit

This is the demagnetization oscillator circuit composed of Q516 and Q517 which oscillates by feedback from the collectors of the two transistors to the base of the other transistors so as to repeat mutual ON/OFF switching. The output of the demagnetization oscillator is fed to the base of transistor Q518 (or Q519) making up the recording bias circuit in combination with Q519 (or Q518) so that it oscillates in synchronization with the demagnetization oscillator circuit so that the two oscillation circuits causes no beats. Because the recording bias circuit is isolated from the demagnetization circuit, the latter is not affected by variation in recording bias; so that it has sufficient demagnetizing efficiency.

C569 in the demagnetization oscillator is used to ensure that the circuit starts oscillation. The series resonance circuit composed of L505 and C560 in the recording bias circuit suppresses distortion of the bias current.

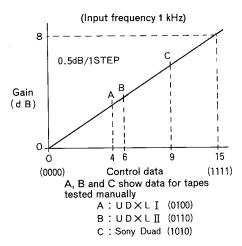

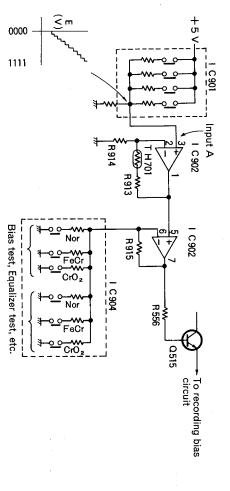

# Variable recording bias circuit and temperature compensation circuit

In the variable recording bias circuit, a 16 step stair wave voltage is generated by adding the 4-bit bias control data output from the microcomputer which controls D/A converter IC901 in the vaviable recording bias circuit as shown in Fig. 39. This voltage is applied to terminal (3) in the first stage of IC902 whose output signal is divided by R913, TH701 and R914. The voltage across R714 is fed to the inverting input of the first stage of IC902 to control its output. TH701 is a temperature compensation thermister and increases the bias in accordance with the temperature characteristics of the head as the temperature varies.

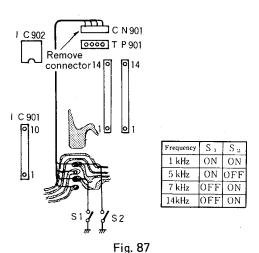

Bias/EQ Test and tape selector detection circuit

Fig. 39

Whether the recording bias circuit or recording equalizer circuit is to be tested is determined by a circuit composed of IC903, Q901, Q902, D903, D904 and D906 where the test signal switching data (2 bits) from the microcomputer is analyzed, and then the bias value is selected in accordance with the characteristics of the tape by the tape selector signal. In the recording bias test, a 5 kHz test signal is recorded to obtain the peak playback gain. If a test higher frequency is selected in this test, the bias value is decreased so as to be able to detect the peak point within the D/A converter variation range since the peak point of the playback output signal changes to a lower value of bias current.

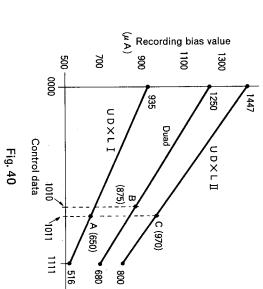

4) Bias setting

The switches in IC904 as shown in Fig. 39 are opened or closed by the Bias/EQ Test and tape selector detection circuit to control the voltage at terminal (6) in the second stage of IC902. The bias is established according to the difference of the voltage applied to terminal (5) from this control signal. The base voltage of the bias current control transistor (Q515) is controlled by this.

Fig. 40 shows the recording bias variations of this unit. A base bias value is determined according to the tape selector switch position and, in addition, the base bias is varied through a D/A converter. In the manual mode, the recording bias values are set at A, B and C according to tape selector switch setting.

A: UDXLI (650,4A)

B: Duad (875µA)

C: UDXLII (970µA)

# 17. Test-in-progress Indicator

codes of IC953 corresponding to the microcomputer output signals are shown in the table below. DECIMAL decoder IC (IC953). The input/output signal control sognals from the microcomputer through a BCD/ GAIN). The display indicators are switched by taking control signals are generated from the 2-bit test frequency incorporated in the test circuits. 3-bit indicator selection advantage of difference in test frequency of the oscillators To inform the operator of progress of the test, the circuit being tested is displayed by an indicator (EQ, BIAS and BIAS and

during the test by using these output signals: During testthrough IC953 is lit unless the test frequency is 14 kHz ing, Q951 and Q952 are on to apply the +5V supply to the The following circuit is provided to operate the three LEDs \_ED anodes. Thus, the LED whose cathode grounded

| 14 kHz | 7 kHz (EQ) | 5 kHz (BIAS) | 1 kHz (GAIN) | Test frequency | Microsomparci Carbar | Microcompute |

|--------|------------|--------------|--------------|----------------|----------------------|--------------|

| 1      | 1          | 0            | 0            | D7             | 9                    | <u> </u>     |

| _      | 0          | 1            | 0            | D8             | 2                    | 2            |

| _      | _          | 0            | 0            | œ              | Input                |              |

| _      | 0          | 1            | 0            | Þ              | Ĕ                    | _            |

| _      | _          | _            | 0            | <b>~</b>       | 0                    | HD7414P      |

| _      |            | 0            | _            | <b>Y</b> 1     | Output               | 4P           |

| _      | 0          | _            | _            | Y2             |                      |              |

Requirement:

Terminals C and D mus be at the 0 level.

Fig. 41

| D80                                            | I C801 |

|------------------------------------------------|--------|

| (a) (b) (c) (c) (c) (c) (c) (c) (c) (c) (c) (c | IC 953 |

| "BIAS" FEOTO LEDS                              | LED33  |

| 34 SR960<br>R961<br>34 SR960<br>R959<br>2951   |        |

| +5 V<br>R961<br>R961<br>80<br>80<br>8959       |        |

Fig. 42

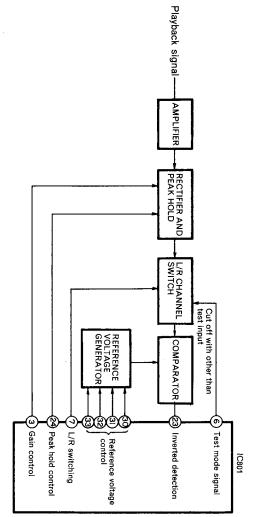

# 18. Playback Gain Detector Circuit

characteristics and recording bias value is determined based on the playback gain which is obtained by recording and playing back the internal test signal. A playback gain The control data used to select the recording equalizer

> value to be detected with the limited level change: detector circuit is provided to determine this playback gain. The circuit has the following construction to allow the peak

Fig. 43

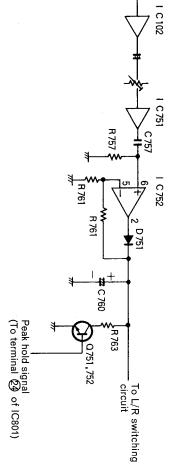

# 1) Amplifier and rectifier peak hold circuit

D-5500

D-5500

for R ch) and is then fed to terminal (5) of IC752. If the across C760 is halved by R760 and R759 (R761 and R762 terminal is rectified by D751 and charges C760. The voltage voltage at terminal (5). The signal produced at the output the voltage at terminal (6) is higher than the reference R757. The amplification gain of IC752 is 1 or more when Fig. 44, the playback signal appears as a voltage drop across After being amplified by IC102 and IC751 as shown in

> playback gain is obtained. and is held by the same principle. Q751 and Q752 discharge gain peak or the level changes, the value before the voltage C760 by terminal decrease voltage at terminal (5) of IC752 goes below the playback is held by D751 and C760. If the input voltage at a command from the microcomputer before the (6) further increases, the peak point is detected

Fig. 44

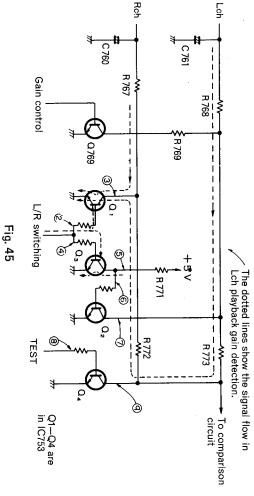

## L/R channel switch

channels are switched in synchronization with the detection in the comparison circuit at the next stage, the L and R timing output from the microcomputer. To detect the peak value for each of the L and R channels

Q1 and Q3 in IC753 conduct while Q2 is cut off to mute the L/R switch signal from the microcomputer is Hi, and When detecting the peak value of the L ch playback signal, output signal voltage is given by: playback signal voltage across R772 at the sam time. The the R ch playback signal by Q1 and to produce a L ch

When detecting the R ch playback signal output, the L/R

while Q2 is on. The output signal voltage at this time is by: switch signal is Lo, and Q1 and Q3 in IC753 are cut off

"1111". generates the reference voltage in the bias test reaches detected decreased by 4 dB when the playback gain peak cannot be Q769 conducts and the playback input signal level is even if the D/A converter control data that

parison circuit output to 1. Q4 is cut off in testing and is on otherwise to fix the com-

**- 30 -**

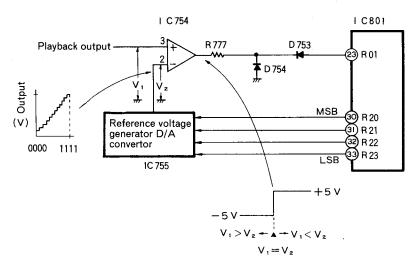

### 3) Comparison and peak detection circuits

IC755 and its associated resistors makes up the D/A converter that generates an analog voltage from the 4-bit playback gain detection data from the microcomputer. This output voltage is fed to terminal (2) of the comparison circuit (IC754) shown in Fig. 46, and the playback output voltage is fed to the other input terminal (3). The output voltage of IC754 reverses when the reference voltage (V2), increasing in increments from the minimum value, agrees

with the playback output voltage (V1). The microcomputer reads the inverted output signal and the reference voltage control data at this time determines the playback gain. The maximum voltage of the reference voltage generator circuit is limited and if the playback output voltage is greater than the maximum reference voltage, Q769 is switched on to decrease the playback input level by 4 dB.

Fig. 46

### 19. Test Signal Oscillator Circuit

Fig. 47

When obtaining appropriate control data for the low (1 kHz), medium (7 kHz) and high (14 kHz) frequency range compensation circuits in the recording equalizer section, and the recording bias circuit (5 kHz), test circuit are switched together with the frequency of the test signal oscillator circuit.

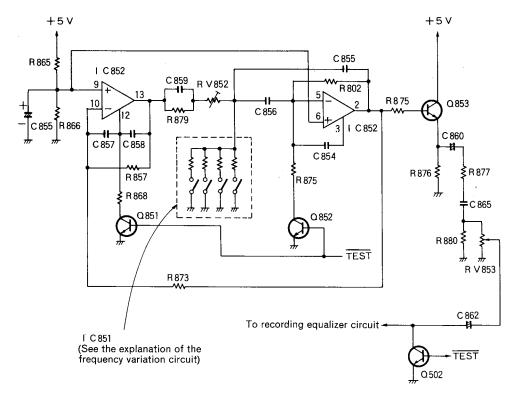

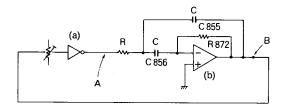

### 1) Principle of oscillation

An simplified diagram of the test signal generator circuit is shown below:

Fig. 48

The transfer function between A and B is obtained by the following formula:

$$f = \frac{1}{2\pi C \sqrt{R \cdot R872}}$$

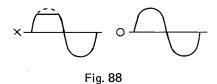

The circuit forms a band-pass filter with a center frequency of f. Since amplifier (b) is an inverting amplifier. oscillations are obtained by feeding-back the output voltage at point B to point A after inverting the signal by amplifier (a). The oscillation is adjusted to a point where the sinusoidal waveform is not clipped with the amount of feedback controlled by RV852.

R in the above formula is the compound resistance consisting of the output impedance of amplifier (a) and frequency variation resistors (R851 — R860), and the oscillation frequency increases as the value of R is decreased.

The actual circuit is as shown in Fig. 47.

Q851 and Q852 are cut off in the test mode, and are on otherwise to prevent oscillation.

The output of the oscillator circuit from terminal (2) of IC852 is amplified by Q853, adjusted to the same output level as when 0VU-20 dB is input and then supplied to the recording equalizer circuit. The test oscillator output is muted by Q502 other than in test mode.

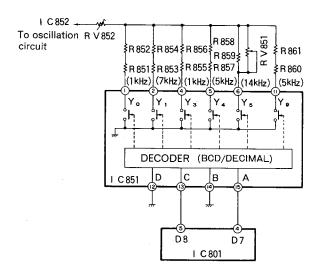

### 2) Oscillation frequency variation control

The oscillation frequency is changed by varying R as previously described. 2-bit switching signals are output from terminals (4) and (5) of IC801 to control the oscillation frequency variation and these control the output of IC851. The table on the left shows oscillation frequency variation instruction input data from the microcomputer and the associated output data. "0" represents the open collector state. To oscillate the circuit at 1 kHz, output terminal (1) is grounded when the input data is "00".

| Inpu | t Data |   | Oscilla-<br>tion fre- |   |   |        |

|------|--------|---|-----------------------|---|---|--------|

| (5)  | (3)    | 1 | 5                     | 2 | 6 | quency |

| _0   | 0      | 0 | 1                     | 1 | 1 | 1 kHz  |

| 0    | 1      | 1 | 0                     | 1 | 1 | 5 kHz  |

| 11   | 0      | 1 | 1                     | 0 | 1 | 7 kHz  |

| 1    | 1      | 1 | 1                     | 1 | 0 | 14 kHz |

Requirement:

Terminals (12) and (14) must be at 0V.

The circuit oscillates at 1 kHz with a resistor of the value set for 1 kHz connected between terminal (1) of IC851 and the junction of RV852 and C856. Two resistors are connected at each of output terminals (4) and (11) of IC851 for oscillations of 1 kHz and 5 kHz respectively for adjustment in the factory.

Fig. 49

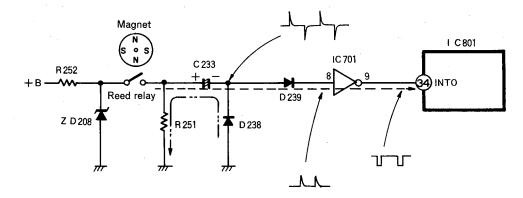

### 20. Transported Tape Length Measurement Circuit

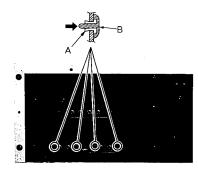

Fig. 50

During testing, the length of transported tape from the beginning of the test (when the test button switch is pushed in the REC/PLAY mode) until the termination of the entire circuit test (termination of the high frequency range compensation test) is measured and the tape is rewound to the start point after the test terminates.

The number of times the reel disc turns is counted by a reed relay and magnet attached to the pulley shaft of the tape counter as shown in the above diagram. Revolutions of the magnet cause the reed relay to repeatedly close and open. A voltage drop is produced across R251 when the reed relay contacts are closed causing the Lo level at terminal (34) of IC801 through C233, D239 and IC701. When the reed relay contacts open, C233 is discharged through D238 and R251 causing the output of IC701 to become Hi. Thus, terminal (34) of IC801 repeats Hi/Lo change-over as the reed relay repeats its closeing and opening and opening action. When terminal (34) changes from Lo to Hi, the microcomputer program is interrupted to add 1 to the reel disc counter in the microcomputer. The tape is automatically rewound to the start point after the high frequency range compensation circuit test terminates. During the rewind operation, 1 is subtracted from the reel disc counter in the microcomputer each time terminal (34) of IC801 changes from Lo to Hi. When the reel disc counter value reaches "0", the test mode output terminal (6) of IC801 changes from Hi to Lo to open the stop signal generator circuit (see the explanation on the stop signal generator circuit).

### Interrupt

An interrupt causes suspension of the program being executed in order to reply to an interrupt request arising from peripheral conditions, etc. Operation results obtained thus far are temporarily stored together with the program step number for future execution and the execution of program processing is interrupted. The execution of the interrupted program is resumed when the interrupt processing program execution is terminated.

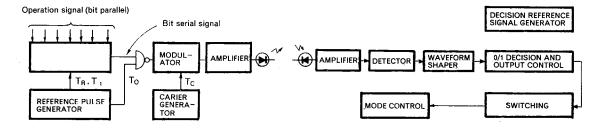

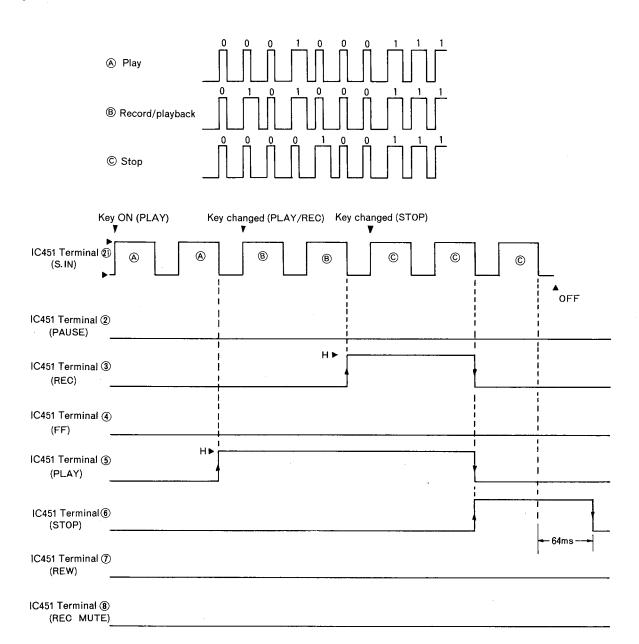

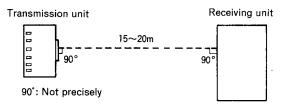

### 21. Remote Control System

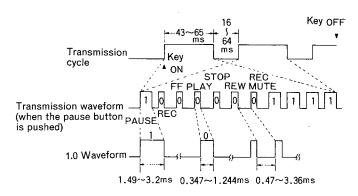

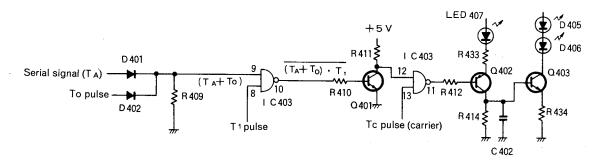

The remote control transmitter section generates a pulse train from push button information. A pushed button corresponds to a 1 pulse signal value in the pulse train while buttons not pushed are represent by pulse signals' values. Each push button corresponds to a specific pulse signal position in the train. This pulse train is pulse width modulated at 50 kHz and drives an infra-red ray emission diode. The receiver section captures this infra-red ray with a

photo diode and associated circuit through an infra-red filter. The captured signal is amplified, detected, its waveform is shaped and then it is supplied to the microcomputer (IC451). The microcomputer performs a "1" and "0" decision on the supplied signal and then discriminate each operation signal from the pulse train to output a single pulse operation signal. The operation pulse signal drives a switching transistor to control the mode control IC(IC201).

Fig. 51

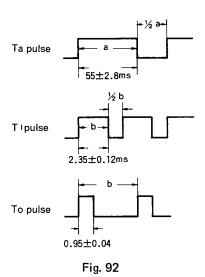

### 1) Signal pulses

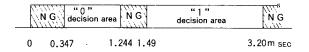

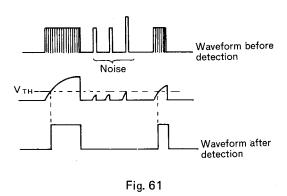

Because the "1" and "0" values of the arriving signal are determined based on the clock signal (400 kHz) of the microcomputer, margins are provided in the "1"/"0" decision as shown in the figure below in order to allow variations of the clock frequency, arriving signal pulses and threshold level of the detection circuit. Furthermore the microcomputer is provided with a program which examines the input signal twice and presence of an operating input signal is decided when the two test results match to prevent error action.

Fig. 52

Fig. 53

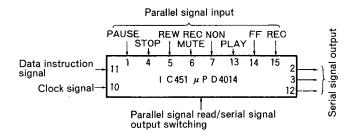

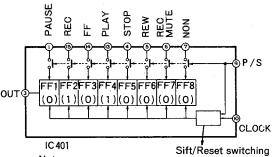

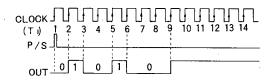

### 2) Prallel/serial converter (IC451)

IC451 is a parallel/serial converter in which the bit parallel signals applied to terminals (1), (4), (5), (6), (7), (11), (13), (14) and (15) are set to an internal memory at the rising edge of the clock signal supplied to terminal (10) when terminal (9) is at the Hi level, and the data in the internal memory is sequentially converted to bit serial data at the rising edge of the input clock signal. Terminal (11) is held at the Hi level during data processing.

Fig. 54

Fig. 55

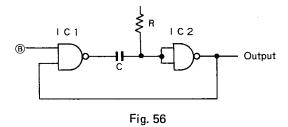

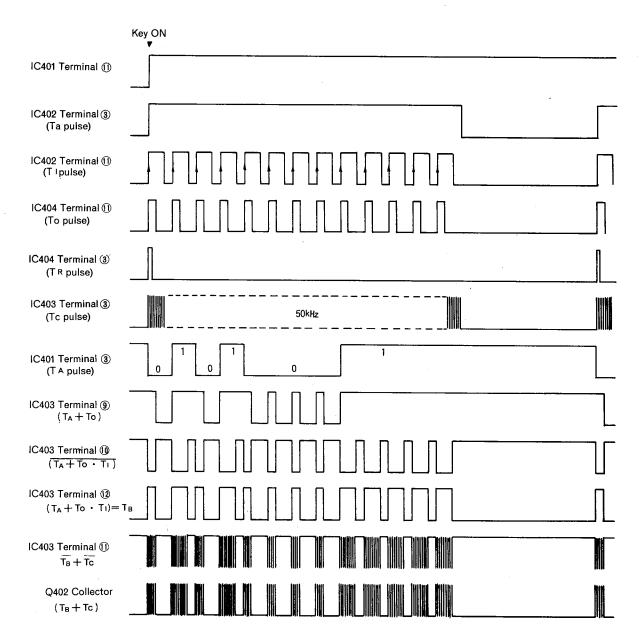

### 3) Ta, Ti and Tc pulse generator circuit

Each Ta, Ti and Tc pulse generator circuit is an non stable multi-vibrator circuit composed of two NAND circuit (or two NOR circuits) and a combination of a C and Rs. The duration of the positive cycle is adjusted by RT and, for the Ta and Ti pulses only, the negative cycle duration is set at approx. 50% of the positive cycle duration by a by-pass resistor which is made effective by the switching action of a diode connected in series with the resistor.

### 4) To and Tr pulse generator circuits

Each of the To and Tr pulse generator circuits is a monostable multivibrator composed of two NAND circuits and a combination of C and R. This circuit generates one pulse each time terminal A changes from Lo to Hi.

### **Circuit Operation**

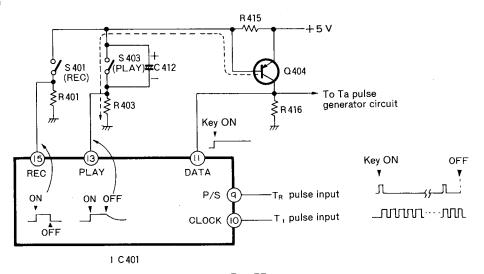

Fig. 57

The circuit operation is explained assuming that both the REC and PLAY buttons are pushed simultaneously. When both the REC and PLAY buttons are pushed simultaneously, the contacts of S401 and S403 are closed to supply current through R415, S401, R401 and through S403 and R403 from the +5V source. The voltage drops produced across R401 and R403 cause terminals (13) and (15) of

IC401 to be set to the Hi level. C412 connected in parallel with S403 is instantaneously discharged once S403 is closed and slowly charged through R415 while S403 is closed so as to act as if, S403 were closed until the second Ta pulse falls (approx. 0.14s to 0.17s) by charging C403 when the button switch is pushed for a very short period of time. When S401 and S403 are closed, Q404 is switched on to start the