# JVC

# SERVICE MANUAL

### **DVD DIGITAL THEATER SYSTEM**

## **TH-A10**

### **Area Suffix TH-A10**

3U ···· Maiaysia, Thailand, **Philippines** 4U ---- Brazil, Mexico, Peru

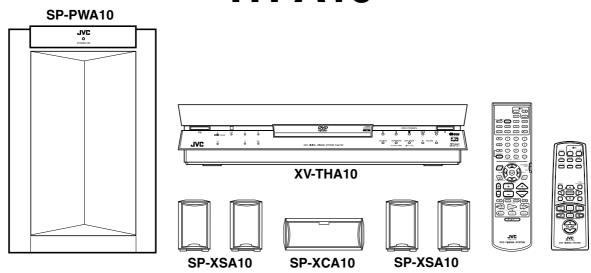

|         | (DVD player)/XV-TH-/ | A10                              |  |  |

|---------|----------------------|----------------------------------|--|--|

| TII 440 | CD TUA10             | SP-PWA10 (Powered subwoofer)     |  |  |

| TH-A10  | SP-THA10             | SP-XCA10 (Center speaker)        |  |  |

|         | (Speaker section)    | SP-XSA10 (Satellite speaker) x 4 |  |  |

#### **Contents**

| Safety precautions1-2             | Disassembly method 1-17       |

|-----------------------------------|-------------------------------|

| Preventing static electricity 1-3 | Main adjustment 1-21          |

| Dismantling and assembling        | Precautions for service 1-24  |

| the traverse unit 1-4             | Description of major ICs 1-25 |

| Disassembly method 1-5            | -                             |

### Safety precautions

- 1. This design of this product contains special hardware and many circuits and components specially for safety purposes. For continued protection, no changes should be made to the original design unless authorized in writing by the manufacturer. Replacement parts must be identical to those used in the original circuits. Services should be performed by qualified personnel only.

- 2. Alterations of the design or circuitry of the product should not be made. Any design alterations of the product should not be made. Any design alterations or additions will void the manufacturer's warranty and will further relieve the manufacture of responsibility for personal injury or property damage resulting therefrom.

- 3. Many electrical and mechanical parts in the products have special safety-related characteristics. These characteristics are often not evident from visual inspection nor can the protection afforded by them necessarily be obtained by using replacement components rated for higher voltage, wattage, etc. Replacement parts which have these special safety characteristics are identified in the Parts List of Service Manual. Electrical components having such features are identified by shading on the schematics and by (1) on the Parts List in the Service Manual. The use of a substitute replacement which does not have the same safety characteristics as the recommended replacement parts shown in the Parts List of Service Manual may create shock, fire, or other hazards.

- 4. The leads in the products are routed and dressed with ties, clamps, tubings, barriers and the like to be separated from live parts, high temperature parts, moving parts and/or sharp edges for the prevention of electric shock and fire hazard. When service is required, the original lead routing and dress should be observed, and it should be confirmed that they have been returned to normal, after re-assembling.

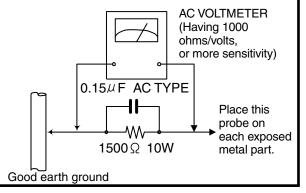

- 5. Leakage currnet check (Electrical shock hazard testing)

After re-assembling the product, always perform an isolation check on the exposed metal parts of the product (antenna terminals, knobs, metal cabinet, screw heads, headphone jack, control shafts, etc.) to be sure the product is safe to operate without danger of electrical shock.

Do not use a line isolation transformer during this check.

- ◆ Plug the AC line cord directly into the AC outlet. Using a "Leakage Current Tester", measure the leakage current from each exposed metal parts of the cabinet, particularly any exposed metal part having a return path to the chassis, to a known good earth ground. Any leakage current must not exceed 0.5mA AC (r.m.s.)

- Alternate check method

Plug the AC line cord directly into the AC outlet. Use an AC voltmeter having, 1,000 ohms per volt or more sensitivity in the following manner. Connect a 1,500 \(\Omega\) 10W resistor paralleled by

a 0.15  $\mu {\rm F}$  AC-type capacitor between an exposed metal part and a known good earth ground.

Measure the AC voltage across the resistor with the AC voltmeter.

Move the resistor connection to each exposed metal part, particularly any exposed metal part having a return path to the chassis, and meausre the AC voltage across the resistor. Now, reverse the plug in the AC outlet and repeat each measurement. voltage measured Any must not exceed 0.75 V AC (r.m.s.). This corresponds to 0.5 mA AC (r.m.s.).

### Warning

- 1. This equipment has been designed and manufactured to meet international safety standards.

- 2. It is the legal responsibility of the repairer to ensure that these safety standards are maintained.

- 3. Repairs must be made in accordance with the relevant safety standards.

- 4. It is essential that safety critical components are replaced by approved parts.

- 5. If mains voltage selector is provided, check setting for local voltage.

<u>AUTION</u> Burrs formed during molding may be left over on some parts of the chassis. Therefore, pay attention to such burrs in the case of preforming repair of this system.

### **Preventing static electricity**

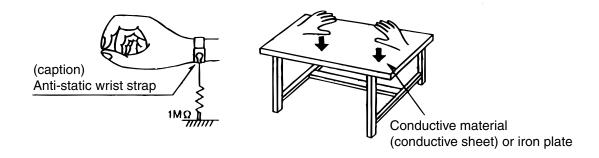

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs.

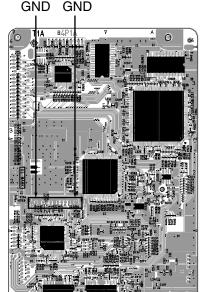

### 1.1. Grounding to prevent damage by static electricity

Static electricity in the work area can destroy the optical pickup (laser diode) in devices such as DVD players. Be careful to use proper grounding in the area where repairs are being performed.

#### 1.1.1. Ground the workbench

1. Ground the workbench by laying conductive material (such as a conductive sheet) or an iron plate over it before placing the traverse unit (optical pickup) on it.

### 1.1.2. Ground yourself

1. Use an anti-static wrist strap to release any static electricity built up in your body.

### 1.1.3. Handling the optical pickup

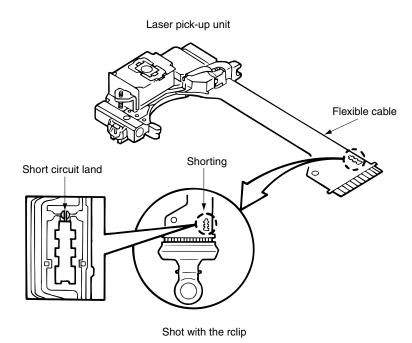

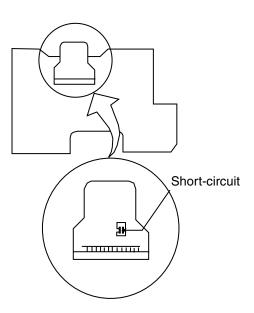

- 1. In order to maintain quality during transport and before installation, both sides of the laser diode on the replacement optical pickup are shorted. After replacement, return the shorted parts to their original condition. (Refer to the text.)

- 2. Do not use a tester to check the condition of the laser diode in the optical pickup. The tester's internal power source can easily destroy the laser diode.

### 1.2. Handling the traverse unit (optical pickup)

- 1. Do not subject the traverse unit (optical pickup) to strong shocks, as it is a sensitive, complex unit.

- 2. Cut off the shorted part of the flexible cable using nippers, etc. after replacing the optical pickup. For specific details, refer to the replacement procedure in the text. Remove the anti-static pin when replacing the traverse unit. Be careful not to take too long a time when attaching it to the connector.

- 3. Handle the flexible cable carefully as it may break when subjected to strong force.

- 4. It is not possible to adjust the semi-fixed resistor that adjusts the laser power. Do not turn it

### Dismantling and assembling the traverse unit

### 1. Notice regarding replacement of optical pickup

Electrostatic discharge (ESD), which occurs when static electricity stored in the body, fabric, etc. is discharged, can destroy the laser diode in the traverse unit (optical pickup). Take care to prevent this when performing repairs to the optical pickup or connected devices.

(Refer to the section regarding anti-static measures.)

- 1. Do not touch the area around the laser diode and actuator.

- 2. Do not check the laser diode using a tester, as the diode may easily be destroyed.

- 3. It is recommended that you use a grounded soldering iron when shorting or removing the laser diode. Recommended soldering iron: HAKKO ESD-compatible product

- 4. Solder the land on the optical pickup's flexible cable.

- Note: Short the land after shorting the terminal on the flexible cable using a clip, etc., when using an ungrounded soldering iron.

- Note: After shorting the laser diode according to the procedure above, remove the solder according to the text explanation.

1-4

### **Disassembly method**

### <Main body>

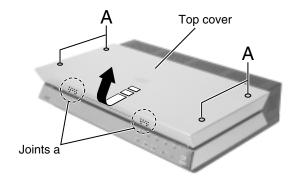

### ■Removing the top cover

(See Fig.1 and 2)

- 1. Remove the four screws A attaching the top cover (Use an Allen wrench).

- 2. Lift up the front part of the top cover to release the two joints a and remove the top cover toward the front.

Fig.1

Top cover

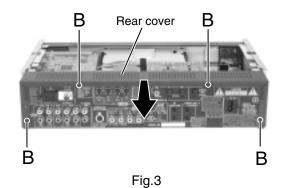

### ■Removing the rear cover (See Fig. 3)

- Prior to performing the following procedure, remove the top cover.

- Remove the four screws B attaching the rear cover on the back of the body. Pull out the rear cover backward.

Fig.2

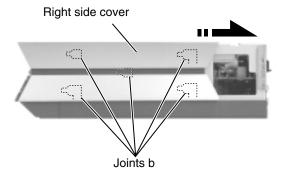

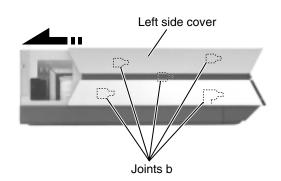

# ■Removing the right and left side covers (See Fig. 4 and 5)

- Prior to performing the following procedure, remove the top cover and the rear cover.

- 1. Move the left side cover backward to release the five joint hooks b and remove the left side cover outward.

- 2. Remove the right side cover in the same way.

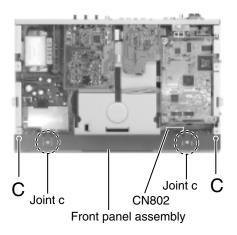

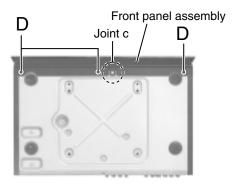

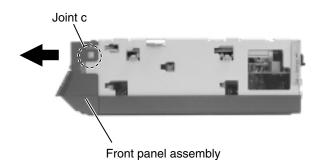

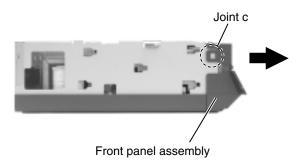

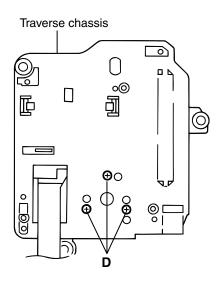

# ■Removing the front panel assembly (See Fig. 6 to 9)

- Prior to performing the following procedure, remove the top cover, the rear cover and the side covers.

- 1. Disconnect the harness from connector CN802 on the main board on the upper side of the body.

- 2. Remove the two screws C on the upper side of the body.

- 3. Remove the three screws D on the bottom of the body.

- 4. Release the five joints c and detach the front panel assembly toward the front.

Fig.6

Fig.7

Fig.9

Fig.8

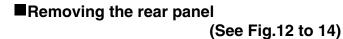

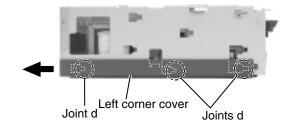

# ■ Removing the right and left corner covers (See Fig.10 and 11)

- Prior to performing the following procedure, remove the top cover, the rear cover, the side covers and the front panel assembly.

- It is not necessary to remove the front panel assembly.

- 1. Move the left corner cover backward to release the three joint hooks d.

- 2. Remove the right corner cover in the same way.

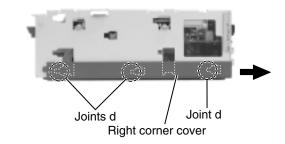

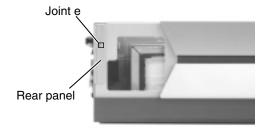

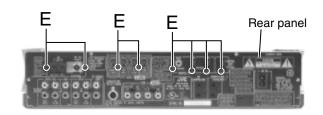

- Prior to performing the following procedure, remove the top cover and the rear cover.

- 1. Remove the eighteen screws E and the one screw F attaching the rear panel.

- 2. Release the two joints e on both sides of the body.

Fig.10

Fig.11

Fig.12

Fig.12 Fig.12

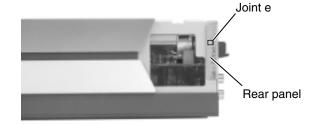

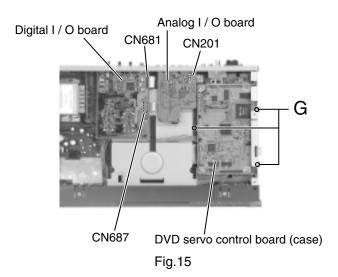

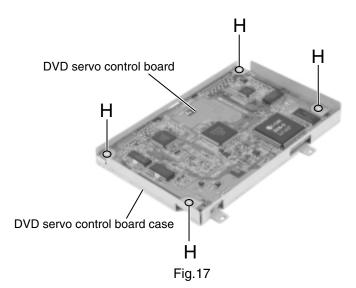

# ■ Removing the DVD servo control board (See Fig.15 to 17)

- Prior to performing the following procedure, remcover and the right side cover.ove the top cover, the rear

- 1. Remove the three screws G and pull the DVD servo control board case upward.

- Disconnect the harness from connector CN501 and CN503, and the card wire from CN101, CN103 and CN502 of the DVD servo control board on the underside of the DVD servo control board case.

- 3. Remove the four screws H attaching the DVD servo control board.

Fig.16

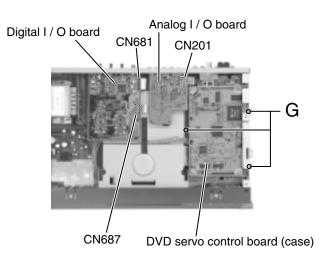

# ■Removing the analog I / O board / the digital I / O board (See Fig.18 and 19)

- Prior to performing the following procedure, remove the top cover and the rear cover.

- Remove the two screws E attaching the analog I / O board on the back of the body.

- 2. Disconnect the card wire from connector CN201 on the analog I / O board.

- 3. Remove the four screws E attaching the digital I / O board on the back of the body.

- 4. Disconnect the card wire from connector CN681 and CN687 on the digital I / O board.

Fig.18

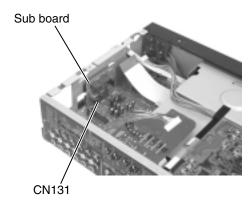

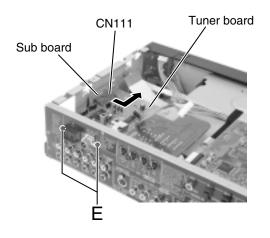

# ■Removing the tuner board / the sub board (See Fig.20 and 21)

- Prior to performing the following procedure, remove the top cover, the rear cover and the DVD servo control board case.

- 1. Remove the two screws E attaching the tuner board on the back of the body.

- Disconnect connector CN111 on the tuner board from the sub board.

- 3. Disconnect connector CN131 on the sub board from the main board.

Fig.19

Fig.21

Fig.20

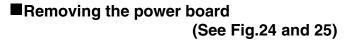

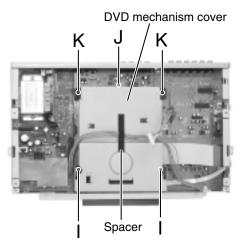

## Removing the DVD mechanism assembly (See Fig.22 and 23)

- Prior to performing the following procedure, remove the top cover, the rear cover, the front panel assembly, the DVD servo control board case, the analog I / O board, the digital I / O board and the tuner board.

- 1. Disconnect the harnesses from the spacer on the upper side of the DVD mechanism cover.

- 2. Remove the two screws I and the one screw J attaching the DVD mechanism cover.

- 3. Remove the two screws K attaching the DVD mechanism assembly.

- 4. Remove the DVD mechanism assembly upward while pulling it backward.

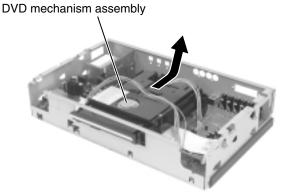

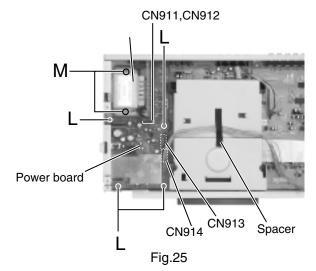

- Prior to performing the following procedure, remove the top cover, the rear cover, the front panel assembly, the DVD servo control board case and the digital I / O board.

- 1. Disconnect the harness from the spacer on the upper side of the DVD mechanism cover.

- 2. Remove the two screws E attaching the power board on the back of the body.

- 3. Disconnect the harness from connector CN911 and CN912 on the power board.

- Remove the four screws L attaching the power board.

- Disconnect connector CN913 and CN914 of the power board from the main board by pulling out them respectively.

Fig.22

Fig.23

Power transformer assembly

CN911,CN912

L

Power board

CN914

CN913

Spacer

Fig.25

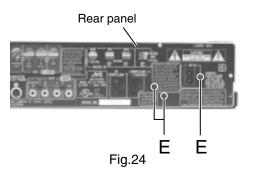

### ■ Removing the power transformer assembly (See Fig.24 and 25)

- · Prior to performing the following procedures, remove the top cover and the rear cover.

- 1. Disconnect the harnesses from connector CN911 and CN912 on the power board.

- 2. Remove the two screws M attaching the power transformer assembly.

- 3. Remove the screw E attaching the power transformer assembly on the back of the body.

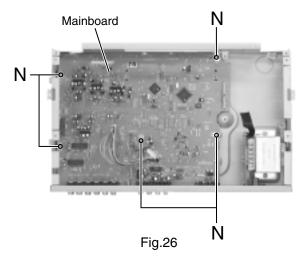

- · Prior to performing the following procedure, remove the top cover, the rear cover, the front panel assembly, the rear panel, the DVD mechanism assembly, the power board and the sub board.

- 1. Remove the four DVD spacers on the upper side of the main board.

- 2. Remove the five screws N attaching the main board.

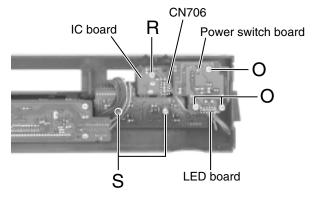

· Prior to performing the following procedure, remove the top cover, the rear cover, the side covers and the front panel assembly.

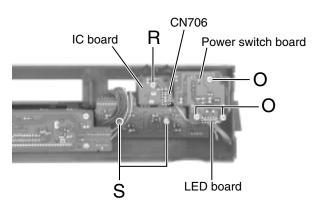

### ■Removing the power switch board (See Fig.27)

- 1. Dithe harness from connector CN705 on the power switch board.sconnect

- 2. Remove the three screws O attaching the power switch board.

Fig.27

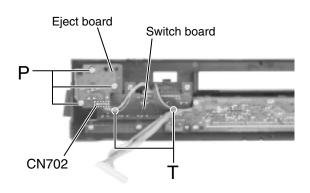

### ■Removing the eject board (See Fig.28)

- 1. Disconnect the harness from connector CN702 on the eject board.

- 2. Remove the three screws P attaching the eject board.

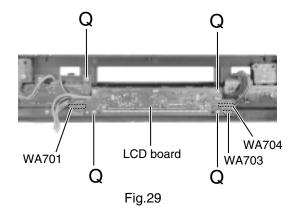

### ■ Removing the LCD board (See Fig.29)

- 1. Remove the four screws Q attaching the LCD board.

- 2. Unsolder WA701, WA703 and WA704 on the LCD board.

### ■ Removing the IC board (See Fig.27)

- 1. Remove the screw R attaching the IC board.

- 2. Disconnect the harness from connector CN706 on the IC board.

### ■ Removing the LED board (See Fig.27)

- Prior to performing the following procedure, remove the LCD board and the IC board.

- 1. Disconnect the harness from connector CN705 on the power switch board.

- 2. Remove the two screws S attaching the LED board.

### ■ Removing the switch board (See Fig.28)

- Prior to performing the following procedure, remove the LCD board.

- 1. Disconnect the harness from connector CN702 on the eject board.

- 2. Remove the two screws T attaching the switch board.

Fig.28

Fig.27

### <Removing DVD mechanism unit>

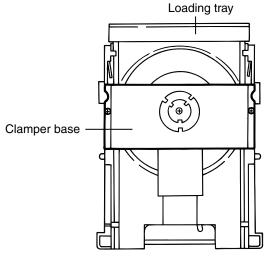

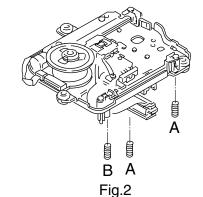

- Removing the clamper base (refer to Figure 1)

- o Remove the top cover.

- o Remove the DVD mechanism unit.

- 1. Remove the two screws at A fixing the clamper base.

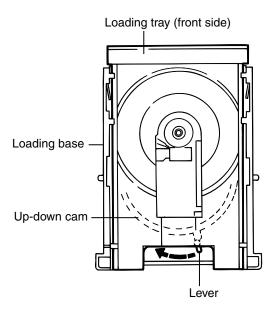

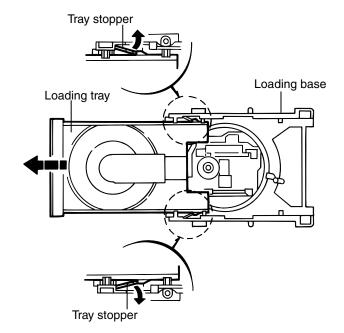

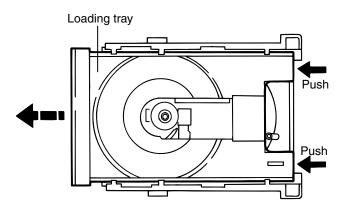

■ Removing the loading tray (refer to Figures 2 - 4)

- o Remove the clamper base.

- 1. Turn the up-down cam lever clockwise (in the direction of the arrow in Figure 2) to lower the position of the mechanism.

- 2. Manually set the loading tray to the fully-open position.

- 3. Stretch the tray stoppers on both sides of the loading base outward and pull out the tray.

Figure 1

Figure 2

Figure 4

Figure 3

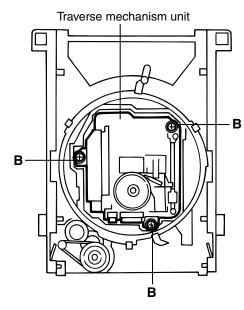

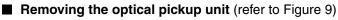

#### ■ Removing the traverse mechanism unit (refer to Figure 5)

- o Remove the loading tray.

- 1. Remove the three screws at B fixing the traverse mechanism unit.

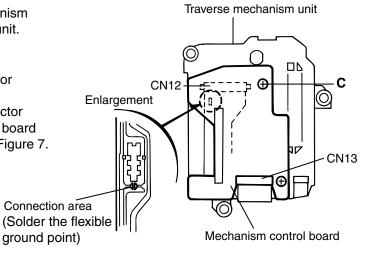

#### Protecting the optical pickup

o Solder the flexible ground point on the optical pickup when replacing the pickup or before detaching the mechanism control board. When assembling the unit, remove the solder last.

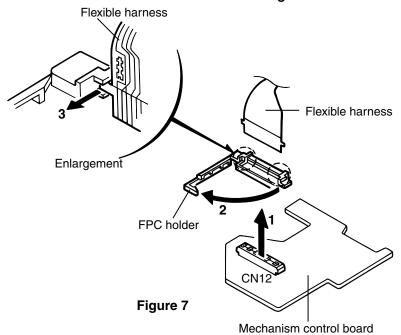

### ■ Removing the mechanism control board (refer to Figures 6 - 7)

- o Remove the traverse unit. (Can be detached without detaching the T-mechanism unit.)

- 1. Remove the two screws at C fixing the mechanism control base from the bottom of the traverse unit.

- 2. Pull out the CN12 connector and detach the mechanism control board.

- 3. Remove the card wire from the CN13 connector on the mechanism control board.

- 4. Pull out the FPC holder from the CN12 connector on the reverse side of the mechanism control board and remove the flexible harness, referring to Figure 7.

Figure 5

Figure 6

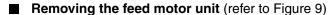

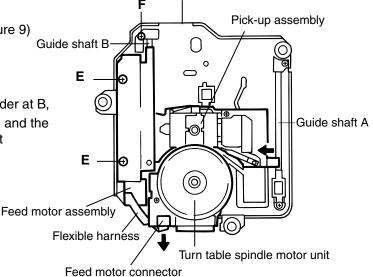

- Removeing the turntable and spindle motor assemby (refer to Figures 8 9)

- o Remove the traverse mechanism unit.

- o Solder the flexible ground point on the optical pickup. (Figure 6)

- o Remove the mechanism control board.

- 1. Remove the flexible harness from the feed motor connector on the spindle motor board assembly.

- Remove the three screws at D fixing the spindle motor from the bottom of the traverse chassis.

- o Remove the traverse mechanism unit.

- o Remove the mechanism control board.

- 1. Remove the FPC from the feed motor connector on the turntable spindle motor board.

- 2. Remove the two screws at E fixing the feed motor unit.

Figure 8

Traverse mechanism unit

- o Remove the traverse mechanism unit.

- o Remove the mechanism control board.

- o Remove the feed motor unit.

- Remove the screw at F fixing the guide shaft holder at B, then simultaneously remove the guide shaft at B and the optical pickup unit. While doing so, slide the unit horizontally away from the guide shaft at A.

Figure 9

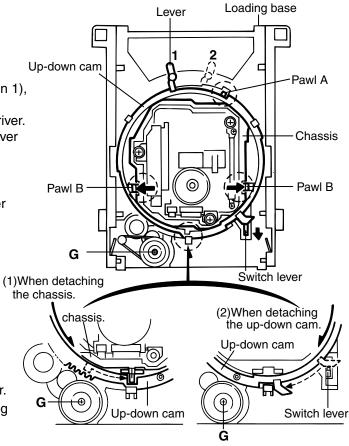

### ■ Removeing the loading mechanism parts (refer to Figures 10 - 11)

- o Remove the clamper base.

- o Remove the disk tray.

- Turn the lever counterclockwise until it stops (position 1), while pushing the switch lever in the direction of the arrow and pushing up the pawl at A using a screwdriver.

- 2. Stretch the two pawls at B outward using a screwdriver and remove the chassis.

- 3. Turn the lever clockwise (position 2) to remove the up-down cam.

- 4. Remove the pulley gear and the pulley gear belt after removing the screw at G fixing the pulley gear.

- 5. Pull out drive gear 2 then drive gear 1.

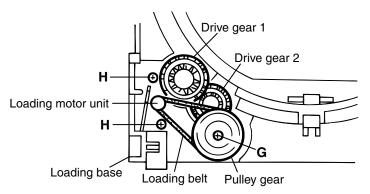

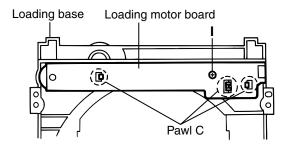

### ■ Removing the loading motor board (refer to Figures 11 - 12)

- o Remove the clamper base.

- o Remove the disk tray.

- 1. Remove the loading belt.

- 2. Remove the two screws at H fixing the loading motor.

- 3. Remove the screw at I and the three pawls at C fixing the loading motor base from the reverse side of the loading base.

Figure 10

Figure 11

Figure 12

### **Disassembly method**

### <Speaker>

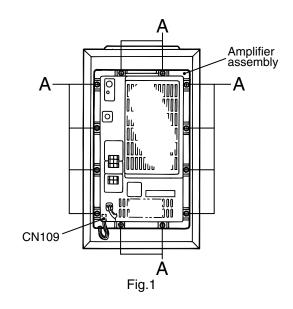

# ■Removing the amplifier assembly (See Fig.1)

- 1. Remove the twelve screws A attaching the amplifier assembly on the back of the body.

- 2. Move the amplifier assembly backward and disconnect the harness from connector CN109 in the lower part of the amplifier assembly.

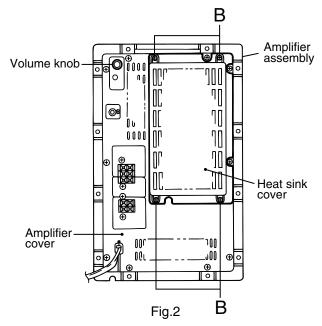

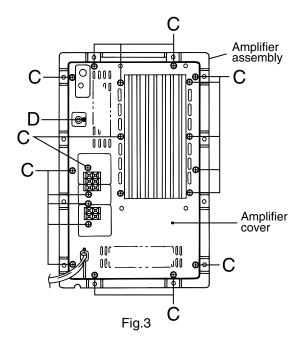

# ■Removing the heat sink cover and the amplifier cover (See Fig.2 and 3)

- Prior to performing the following procedure, remove the amplifier assembly.

- 1. Pull out the volume knob.

- 2. Remove the four screws B attaching the heat sink cover.

- 3. Remove the twenty screws C and the one screw D attaching the amplifier cover.

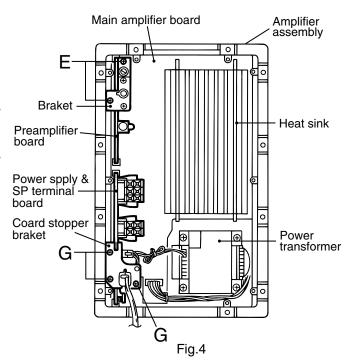

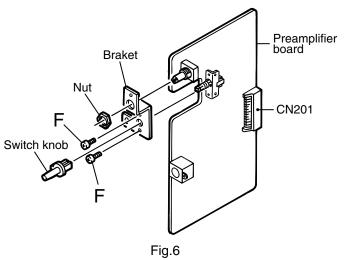

# ■ Removing the preamplifier board (See Fig.4 to 6)

- Prior to performing the following procedure, remove the heat sink cover and the amplifier cover.

- 1. Remove the two screws E attaching the preamplifier board to the bracket.

- 2. Disconnect connector CN201 on the preamplifier board from the main amplifier board.

- 3. Pull out the switch knob.

- Remove the nut and the two screws F attaching the bracket.

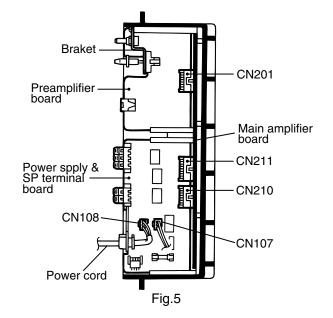

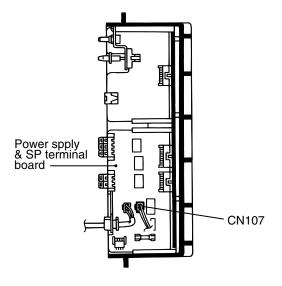

### ■Removing the power spply & SP terminal board (See Fig.4and 5)

- Prior to performing the following procedure, remove the heat sink cover and the amplifier cover.

- 1. Remove the three screws G attaching the coard stopper braket.

- 2. Disconnect connector CN210 and CN211 on the power spply & SP terminal board from the main amplifier board.

- 3. Disconnect the power cord from connector CN108 on the power spply & SP terminal board and the harness from CN107.

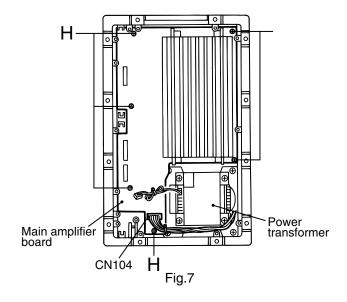

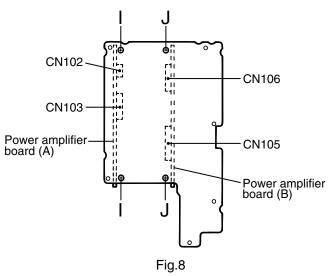

# ■Removing the Power Amplifier Board(See Fig.7 and 8)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier cover, the preamplifier board and the power spply & SP terminal board.

- 1. Disconnect the harness from connector CN104 on the power amplifier board.

- Remove the six screws H and the power amplifier board with the heat sink.

- Remove the two screws I attaching the power amplifier board (A) and the two screws J attaching the power amplifier board (B) on the underside of the power amplifier board.

- Disconnect connector CN102 and CN103 on the power amplifier board (A) and CN105 and CN106 on the power amplifier board (B) from the power amplifier board respectively.

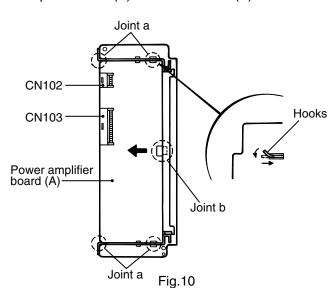

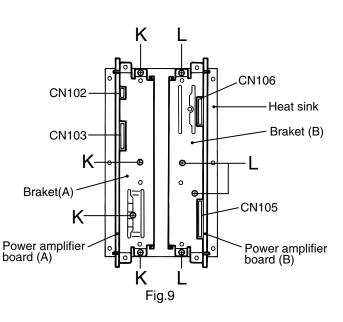

# ■Removing the power amplifier board (A) (See Fig.9 and 10)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier cover, the preamplifier board, the power spply & SP terminal board and the power amplifier board.

- 1. Remove the four screws K attaching the power amplifier board (A) to the heat sink.

- 2. Release the four joint hooks a bent and attached to the outside of the power amplifier board (A).

- 3. Move the power amplifier board (A) in the direction of the arrow to release joint b and remove the power amplifier board (A) from the bracket (A).

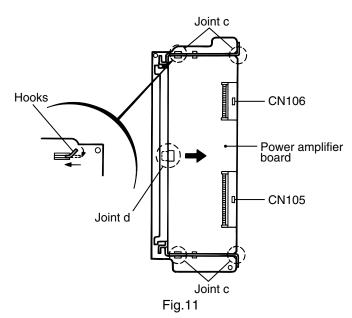

## ■Removing the power amplifier board (B) (See Fig.9 and 11)

- Prior to performing the following procedure, remove the heat sink cover, the amplifier cover, the preamplifier board, the power spply & SP terminal board and the main amplifier board.

- Remove the four screws L attaching the power amplifier board (B) to the heat sink.

- 2. Release the four joint hooks c bent and attached to the outside of the power amplifier board (B).

- 3. Move the power amplifier board (B) in the direction of the arrow to release joint d and remove the power amplifier board (B) from the bracket (B).

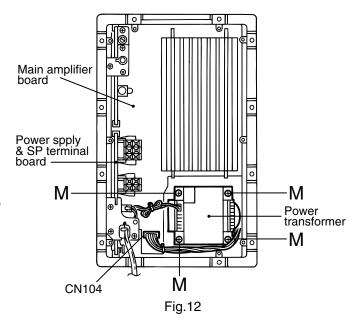

# ■Removing the power transformer (See Fig.12 and 13)

- Prior to performing the following procedure, remove the amplifier cover.

- 1. Disconnect the harness from connector CN104 on the main amplifier board.

- 2. Disconnect the harness from connector CN107 on the power spply & SP terminal board.

- 3. Remove the four screws M attaching the power transformer.

Fig.13

### Main adjustment

Adjustment and confirmation matter

(1) Auto adjustment method

If microprocessor (IC401, IC402, IC714, IC716) or DVD Prek-up is replaced, initialize the DVD player in the following matter:

- 1. Initialize the DVD player in the following matter:

- 1) Make sure that no disc is on the tray.

- 2) Insert the power pulag to the outret while pressing "PLAY" and "OPEN/CLOSE" button at the same time.

- FL Display indicate ¥; Region cord.

- 3) Press Enter button. And EEPROM initialize start.

- 4) When indicate "96kHz EEPROM" on the display, initialize finished.

Note: During the EEPROM initialization the keys may not be operated.

Press the "POWER" key to initiate the STAND-BY mode and the test mode will then be cancelled.

### (2) Confirmation of DVD RF level

- 1. The oscilloscope is connected between P1 and GND.

- 2.Reproduction of the test disc (VT-501) made by JVC.

- 3.It is confirmed that RF LEVEL is 350 mVp-p 150 mVp-p.

- 4. When there is disorder in the waveform road cuts etc, test disk is exchanged and measured.

#### (3) Confirmation of CD jitter level and RF level

- 1. The CD jitter meter is connected between GND and P12. The RF level is observed at the same time.

- 2. The first test disk(CTS-1000) made of JVC is reproduced.

- 3.It is confirmed that RF LEVEL is 360 100mVp-p.

- 5. When there is disorder in the waveform road cuts etc, test disk is exchanged and measured.

P12

and

and

DVD SERVO CONTROL PWB

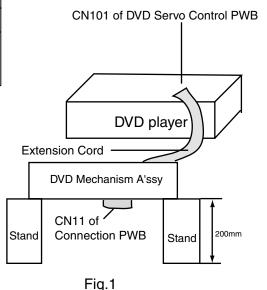

### (4) Flap adjustment of the Pick-up guide shaft

- 1) Make sure that there is no disc on the tray.

- 2) Press both the "PLAY" and "OPEN/CLOSE" keys of the main unit to activate the primary power and \* \* \*( \* \*; Version3, \*\*); Region cord) will be displayed on the FL indicator.

Note: If the FL indicator display stops and remains at "TEST 0", unplug the power cord from the outlet and after waiting at least 1 second, plug it in again. After the tray open/close procedure has completed, unplug it again and then perform the initialization procedure again.

- 3) Press the "OPEN/CLOSE" key of the main unit to draw the tray out.

\*Place the test disk (VT-501) on the tray and then press the "OPEN/CLOSE" key.

(Note: Pushing the tray to close it is not possible.)

- 4) Press the "PLAY" key of the main unit.

- 5) The "JIT 0000" is displayed on the FL indicator. Set the FL indicator figure value to its minimum by adjusting the pickup guide shaft flap. \* The test mode is cancelled when the power is turned off.

| Measurement                              |   | djustment point | Mode               | Disc   |  |  |  |

|------------------------------------------|---|-----------------|--------------------|--------|--|--|--|

| _                                        | ı | Refer to Fig.2  | Reproduction part  | VT-501 |  |  |  |

| Measurement machine                      |   | connections     | Extension cord No. |        |  |  |  |

| No need                                  |   | Refer to Fig.1  | QUQ110-3740AM      |        |  |  |  |

| General tool : Hex-head wrench (1.27 mm) |   |                 |                    |        |  |  |  |

"Flap adjustment" of the Pick-up guide shaft adjusts "Tangential adjustment machine screw" A and "Tilt adjustment machine screw" B from the DVD Mechanism A'ssy bottom.

- 1. The part at the center on the DVD test disc is reproduced.

- 2. The flap adjustment screws is turned alternately and adjusted like clearly seeing the waveform of CN104"1" to the way.

#### Note

- 1. The tangential adjustment is done finish and, then, tilt is adjusted.

- 2.The repeat the adjustment 2-3 times, for best result.

- 3. The final adjustment should be tilt adjustment.

### Confirmation after adjustment.

Confirm to reproduce video CD and CD after the DVD test disc is adjusted and to find abnormality.

### (5) About keeping the disc

As for the DVD test disc, plane accuracy is demanded. Please note the keeping place on the disc.

- 1. Please do not put the disc directly on the work desk etc. after uses .

- 2. To keep the planarity of the disc, politely handle ,and please put in a special case and keep the disc vertically after uses .

- Please keep keeping the disc in a cool place where direct sunshine and the air-conditioning wind do not drive.

- 3. When the disc curves, an accurate adjustment cannot be done. Please exchange for a new test disc and adjust optics.

- 4. Other discs might not be able to be reproduced when adjusting on a curved disc.

#### Point of adjustment

- \* Please execute the static electricity protection measures before starting the adjustment.

- \* When the following parts are exchanged, optical adjustment "Adjust the flap of the disc motor" is necessary.

- 1. The disc motor was exchanged.

- 2. The laser pick up was exchanged.

- 3. The traverse motor unit was exchanged.

#### Note

Additionally, please adjust the flap of the disc motor when the picture quality deterioration is seen .The basic adjustment though, is unnecessary for part exchange in the traverse.

An optical adjustment in the laser pick up cannot be done.

Please adjust the flap of the disc motor after exchanging the laser pick up.

<sup>\*</sup> When the traverse unit is exchanged, the adjustment is basically unnecessary.

### **Precautions for Service**

### Handling of Traverse Unit and Laser Pickup

- 1. Do not touch any peripheral element of the pickup or the actuator.

- 2. The traverse unit and the pickup are precision devices and therefore must not be subjected to strong shock.

- 3. Do not use a tester to examine the laser diode. (The diode can easily be destroyed by the internal power supply of the tester.)

- 4. To replace the traverse unit, pull out the metal short pin for protection from charging.

- 5. When replacing the pickup, after mounting a new pickup, remove the solder on the short land which is provided at the center of the flexible wire to open the circuit.

- 6. Half-fixed resistors for laser power adjustment are adjusted in pairs at shipment to match the characteristics of the optical block.

- Do not change the setting of these half-fixed resistors for laser power adjustment.

### Destruction of Traverse Unit and Laser Pickup by Static Electricity

Laser diodes are easily destroyed by static electricity charged on clothing or the human body. Before repairing peripheral elements of the traverse unit or pickup, be sure to take the following electrostatic protection:

- 1. Wear an antistatic wrist wrap.

- 2. With a conductive sheet or a steel plate on the workbench on which the traverse unit or the pick up is to be repaired, ground the sheet or the plate.

- 3. After removing the flexible wire from the connector (CN101), short-circuit the flexible wire by the metal clip.

- 4. Short-circuit the laser diode by soldering the land which is provided at the center of the flexible wire for the pickup. After completing the repair, remove the solder to open the circuit.

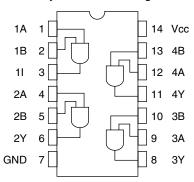

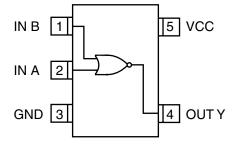

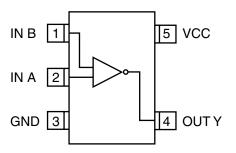

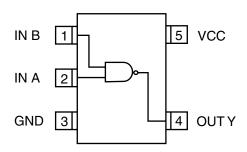

### Discription of major IC's

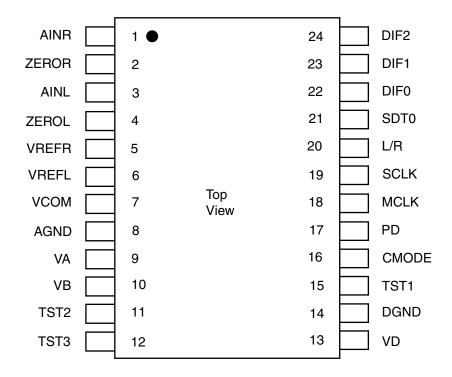

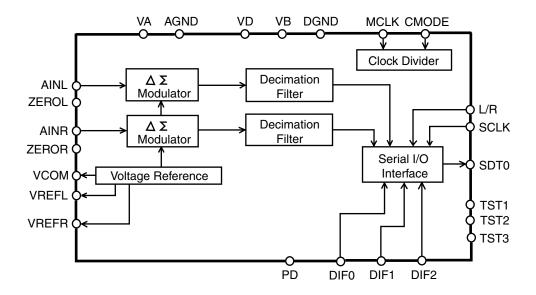

### ■ AK5330 (IC701) : A/D Converter

1. Terminal layout

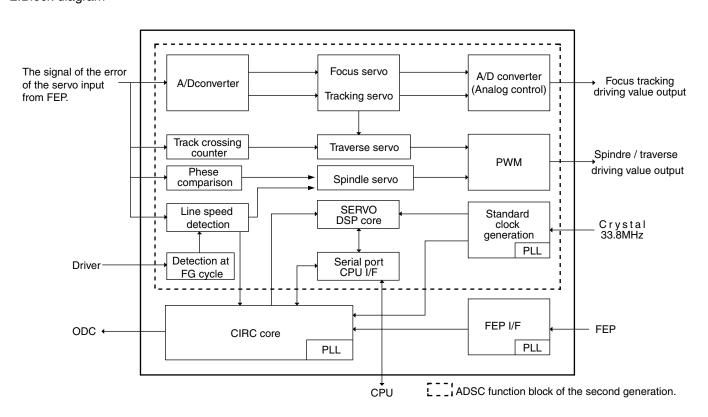

#### 2. Block diagram

### 3. Pin function

| No. | Pin Name  | I/O      | Function                                                     |  |  |

|-----|-----------|----------|--------------------------------------------------------------|--|--|

| 1   | AINR      | I        | Rch Analog Input Pin                                         |  |  |

| 2   | ZEROR     | I        | Rch Zero Input Pin                                           |  |  |

| 3   | AINL      | I        | Lch Analog Input Pin                                         |  |  |

| 4   | ZEROL     | I        | Lch Zero Input Pin                                           |  |  |

| 5   | VREFR     | 0        | Rch Vopltage Reference Output Pin. 2.5V                      |  |  |

|     |           |          | Normally connected to AGND with a 0.1uF ceramic capacitor    |  |  |

|     |           |          | in parallel with an electrolytic capacitor less than 10uF.   |  |  |

| 6   | VREFL     | 0        | Lch Vopltage Reference Output Pin. 2.5V                      |  |  |

|     |           |          | Normally connected to AGND with a 0.1uF ceramic capacitor    |  |  |

|     |           |          | in parallel with an electrolytic capacitor less than 10uF.   |  |  |

| 7   | VCOM      | 0        | Voltage Common Output Pin. 2.5V                              |  |  |

|     |           |          | Normally connected to AGND with a 0.1uF ceramic capacitor    |  |  |

|     |           |          | in parallel with an electrolytic capacitor less than 10uF.   |  |  |

| 8   | AGND      | -        | Analog Ground Pin                                            |  |  |

| 9   | VA        | -        | Analog Supply Pin, +5V                                       |  |  |

| 10  | VB        | -        | Substrate Voltage Supply Pin, +5V                            |  |  |

| 11  | TST2      | I/O      | Test Pins (Pull-down pin)                                    |  |  |

| 12  | TST3      | I/O      | Must be left floating.                                       |  |  |

| 13  | VD        | -        | Digital power Supply Pin, +5V                                |  |  |

| 14  | DGND      | -        | Digital Ground Pin                                           |  |  |

| 15  | TST1      | ı        | Test Pin (Pull-down pin)                                     |  |  |

|     |           |          | Must be left floating or connected to DGND.                  |  |  |

| 16  | CMODE     | ı        | Master Clock Select Pin                                      |  |  |

|     |           |          | "L" : MCLK=256fs, "H" : MCLK=384fs                           |  |  |

| 17  | PD        | ı        | Power-Down Pin                                               |  |  |

|     |           |          | When "H", the circuit is in power-down mode,Upon             |  |  |

|     |           |          | returning to "L", the AK5330 starts an offset calibration    |  |  |

|     |           |          | cycle.A calibration cycle should always be initiated after   |  |  |

|     |           |          | power-up.                                                    |  |  |

| 18  | MCLK      | I        | Master Clock Input Pin                                       |  |  |

| 19  | SCLK      | I        | Serial Data Clock Pin                                        |  |  |

|     |           |          | Output data is clocked out on the falling edge of SCLK.      |  |  |

|     |           |          | Input data is clocked in on the rising edge of SCLK. SCLK    |  |  |

|     |           |          | requires a continuously supplied clock at any frequency from |  |  |

|     |           |          | 32fs to 64fs.                                                |  |  |

| 20  | L/R       | ı        | Left/Right Channel Select Pin                                |  |  |

|     |           |          | The fs clock is input to this pin.                           |  |  |

|     |           |          | "H" : Lch, "L" : Rch                                         |  |  |

| 21  | SDT0      | 0        | Serial Data Output Pin                                       |  |  |

|     | -         |          | Data bits are presented MSB first, in 2's complement format. |  |  |

|     |           |          | This pin is "L" in the power-down mode.                      |  |  |

| 22  | DIF0      | ı        | Serial Interface Format Pin                                  |  |  |

| 23  | DIF1      | '        | Correspond to 8 modes.                                       |  |  |

| 24  | DIF2      | ·        |                                                              |  |  |

|     | ~ · · · · | <u> </u> |                                                              |  |  |

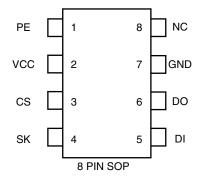

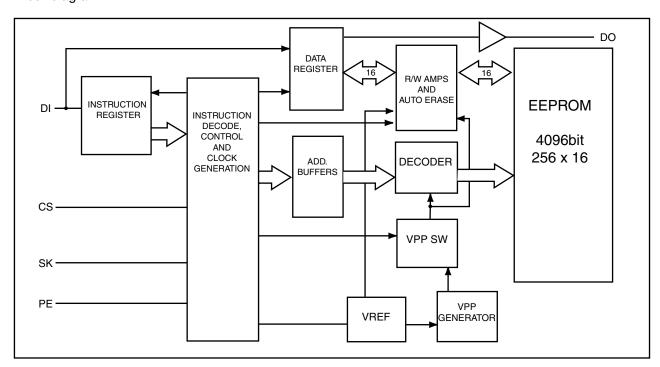

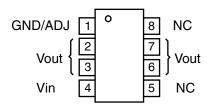

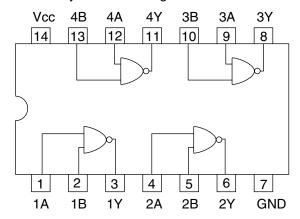

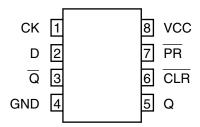

### ■ AK93C65AF-X (IC590) : EEPROM

### 1.Pin layout

### 2.Block diagram

#### 3.Pin function

| Pin no. | Symbol | Function                                        |  |  |  |

|---------|--------|-------------------------------------------------|--|--|--|

| 1       | PE     | Program enable (With built-in pull-up resistor) |  |  |  |

| 2       | VCC    | Power supply                                    |  |  |  |

| 3       | CS     | Chip selection                                  |  |  |  |

| 4       | SK     | Cereal clock input                              |  |  |  |

| 5       | DI     | Cereal data input                               |  |  |  |

| 6       | DO     | Cereal data output                              |  |  |  |

| 7       | GND    | Ground                                          |  |  |  |

| 8       | NC     | No connection                                   |  |  |  |

NOTE : The pull-up resistor of the PE pin is about 2.5M  $\Omega$  (VCC=5V)

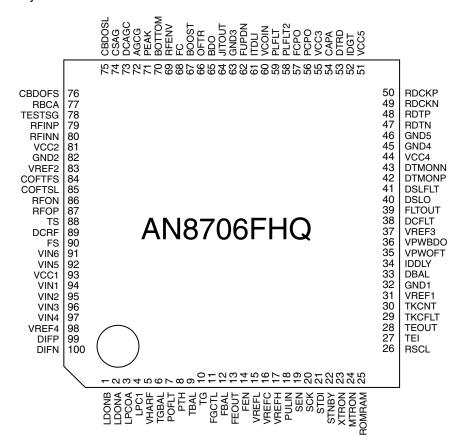

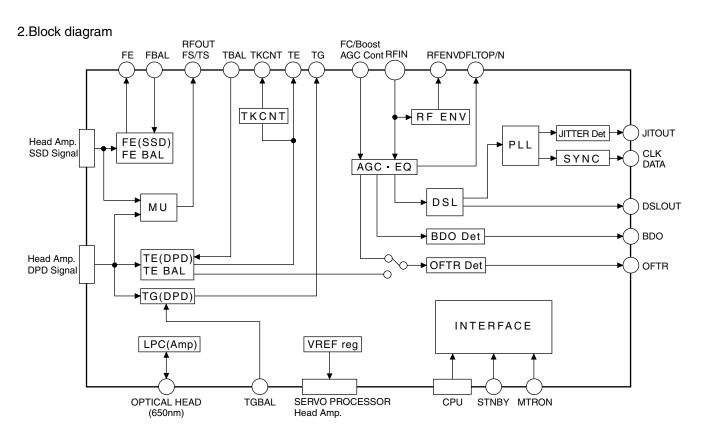

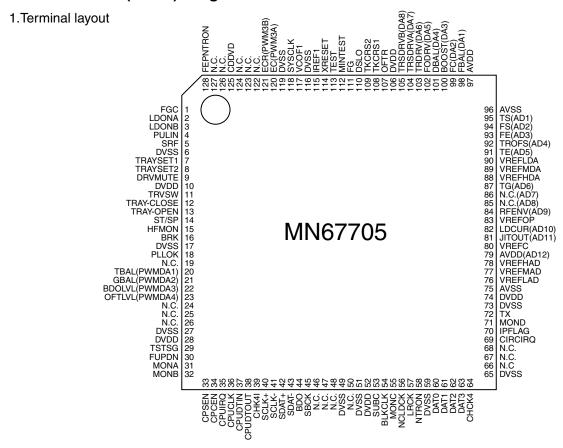

### ■ AN8706FHQ (IC101): Front end processor

#### 1.Pin layout

3.Pin function

| unction |        |      | AN8706FHQ (1/2)                                                              |

|---------|--------|------|------------------------------------------------------------------------------|

| Pin No. | Symbol | 1/0  | Functions                                                                    |

| 1       | LDONB  | I    | Laser ON (CD Head) terminal                                                  |

| 2       | LDONA  | ı    | Laser ON (DVD Head) terminal                                                 |

| 3       | LPCOA  | 0    | Laser drive output terminal                                                  |

| 4       | LPC1   | ı    | Laser PIN input terminal                                                     |

| 5       | VHARF  | 0    | VHALF voltage output terminal                                                |

| 6       | TGBAL  | ı    | Tangential phase balance control terminal                                    |

| 7       | POFLT  | 0    | Track detection Threshold value level terminal                               |

| 8       | PTH    | ı    | Track detection Threshold value level terminal                               |

| 9       | TBAL   | ı    | Tracking balance control terminal                                            |

| 10      | TG     | 0    | Tangential phase error signal output terminal                                |

| 11      | FGCTL  | ı    | Focus amplifier Gain control terminal                                        |

| 12      | FBAL   | ı    | Focus balance control terminal                                               |

| 13      | FEOUT  | 0    | Focus error signal output terminal                                           |

| 14      | FEN    | Ī    | Focus error output amplifier reversing input terminal                        |

| 15      | VREFL  | 0    | VREFL voltage output terminal                                                |

| 16      | VREFC  | 0    | VREFC voltage output terminal                                                |

| 17      | VREFH  | 0    | VREFH voltage output terminal                                                |

| 18      | PULIN  | I    | DSL,PLL drawing mode switch terminal                                         |

| 19      | SEN    | ı    | SEN(Cereal data input terminal)                                              |

| 20      | SCK    | ı    | SCK(Cereal data input terminal)                                              |

| 21      | STDI   | ı    | STDI(Cereal data input terminal)                                             |

|         |        | ı    | , ,                                                                          |

| 22      | STNBY  | -    | Standby mode control terminal                                                |

| 23      | XTRON  | I    | Tracking OFF holding input terminal                                          |

| 24      | MTRON  | I    | Monitor output ON/OFF switch terminal                                        |

| 25      | ROMRAM | 1    | ROM · RAM switch terminal                                                    |

| 26      | RSCL   | 0    | Standard current source terminal                                             |

| 27      | TEI    | 1    | Tracking error output Amp reversing input terminal                           |

| 28      | TEOUT  | 0    | Tracking error signal output terminal                                        |

| 29      | TKCFLT | 0    | Track count detection filter terminal                                        |

| 30      | TKCNT  | 0    | Track count output terminal                                                  |

| 31      | VREF1  | 0    | VREF1 voltage output terminal                                                |

| 32      | GND1   | 0    | Earth terminal 1                                                             |

| 33      | DBAL   | <br> | Data slice offset adjustment terminal                                        |

| 34      | IDDLY  | <br> | Data slice delay adjustment terminal                                         |

| 35      | VPWOFT | <br> | OFTR detection level setting terminal                                        |

| 36      | VPWBDO |      | BDO detection level setting terminal                                         |

| 37      | VREF3  | 0    | VREF3 voltage output terminal                                                |

| 38      | DCFLT  | 0    | Capacity connection terminal for data slice input filter                     |

| 39      | FLTOUT | 0    | Filter amplifier output terminal                                             |

| 40      | DSLO   | 0    | Data slice single data output terminal                                       |

| 41      | DSLFLT | 0    | Constant filter terminal when data is sliceddelly                            |

| 42      | DTMONP | 0    | PLL differential motion 2 making to value edge signal moniter output (+)     |

| 43      | DTMONN | 0    | PLL differential motion 2 making to value edge signal moniter output (-)     |

| 44      | VCC4   | I    | Power terminal 4 (5V)                                                        |

| 45      | GND4   | 0    | Earth terminal 4                                                             |

| 46      | GND5   | 0    | Earth terminal 5                                                             |

| 47      | RDTN   | 0    | PLL differential motion making to synchronization RF signal reversing output |

| 48      | RDTP   | 0    | PLL differential motion making to synchronization RF signal rotation output  |

| 49      | RDCKN  | 0    | PLL differential motion making synchronization clock reversing output        |

| 50      | RDCKP  | 0    | PLL differential motion making synchronization clock rotation output         |

AN8706FHQ(2/2)

|         |         |     | AN8706FHQ(2/2)                                                    |

|---------|---------|-----|-------------------------------------------------------------------|

| Pin No. | Symbol  | I/O | Functions                                                         |

| 51      | VCC5    | I   | Power terminal 5 (3.3V)                                           |

| 52      | IDGT    | I   | Data slice part address part gate signal input terminal (For RAM) |

| 53      | DTRD    | I   | Data slice data read signal input terminal(For RAM)               |

| 54      | CAPA    | ı   | Data slice CAPA(Address)signal input terminal (For RAM)           |

| 55      | VCC3    | I   | Power terminal 3 (5V)                                             |

| 56      | PCPO    | 0   | PLL phase gain set terminal                                       |

| 57      | FCPO    | 0   | PLL frequency gain set terminal                                   |

| 58      | PLFLT2  | 0   | PLL low region filter terminal                                    |

| 59      | PLFLT   | 0   | PLL high region filter terminal                                   |

| 60      | VCOIN   | I   | PLL VCO input terminal                                            |

| 61      | ITDLI   | 0   | PLL jitter free current ripple removal filter terminal            |

| 62      | FUPDN   | I   | PLL frequency control input terminal                              |

| 63      | GND3    | 0   | Earth terminal 3                                                  |

| 64      | JITOUT  | 0   | Detection signal output of jitter                                 |

| 65      | BDO     | 0   | BDO output terminal                                               |

| 66      | OFTR    | 0   | OFTR output terminal                                              |

| 67      | BOOST   | ı   | Booth control terminal for filter                                 |

| 68      | FC      | ı   | FC control terminal for filter                                    |

| 69      | RFENV   | 0   | RF enve output terminal                                           |

| 70      | воттом  | 0   | Bottom enve detection filter terminal                             |

| 71      | PEAK    | 0   | Peak enve detection filter terminal                               |

| 72      | AGCG    | 0   | AGC amplifier gain control terminal                               |

| 73      | DCAGC   | 0   | AGC amp filter terminal                                           |

| 74      | CSAG    | 0   | Sag cancellation circuit filter terminal                          |

| 75      | CBDOSL  | 0   | BDO detection capacitor terminal                                  |

| 76      | CBDOFS  | 0   | BDO detection capacitor terminal                                  |

| 77      | RBCA    | 0   | BCA detection level setting terminal                              |

| 78      | TESTSG  | ı   | TEST signal input terminal                                        |

| 79      | RFINP   | ı   | RF signal positive moving input terminal                          |

| 80      | RFINN   | ı   | RF signal reversing input terminal                                |

| 81      | VCC2    | ı   | Power terminal 2 (5V)                                             |

| 82      | GND2    | 0   | Earth terminal 2                                                  |

| 83      | VREF2   | 0   | VREF2 voltage output terminal                                     |

| 84      | COFTFS  | 0   | OFTR detection capacitor terminal                                 |

| 85      | COFTFL  | 0   | OFTR detection capacitor terminal                                 |

| 86      | RFON    | 0   | RF signal output terminal P                                       |

| 87      | RFOP    | 0   | RF signal output terminal N                                       |

| 88      | TS      | 0   | All addition amplifier (DVD) output terminal                      |

| 89      | DCRF    | 0   | All addition amplifier capacitor terminal                         |

| 90      | FS      | 0   | All addition amplifier (CD) output terminal                       |

| 91      | VIN6    | Ī   | Focus input of external division into two terminal                |

| 92      | VIN5    | i   | Focus input of external division into two terminal                |

| 93      | VCC1    | i   | Power terminal 1 (5V)                                             |

| 94      | VIN1    | i   | External division into four (DVD/CD) RF input terminal 1          |

| 95      | VIN2    | i   | External division into four (DVD/CD) RF input terminal 2          |

| 96      | VIN3    | i   | External division into four (DVD/CD) RF input terminal 3          |

| 97      | VIN4    | i   | External division into four (DVD/CD) RF input terminal 4          |

| 98      | VREF4   | 0   | VREF4 voltage output terminal                                     |

| 99      | DIFP    | 0   | RF signal (RAM) output terminal P                                 |

| 100     | DIFN    | 0   | RF signal (RAM) output terminal N                                 |

| 100     | ווט ווט |     | THE SIGNAL (FIZIVI) OULPUT TOTALINATIVE                           |

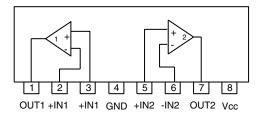

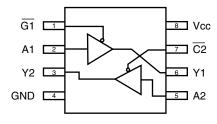

### ■ BA15218N (IC32 / IC35) : Dual Ope. Amp.

### ■ MC33269D-X (IC555) : Regurator

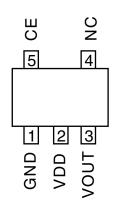

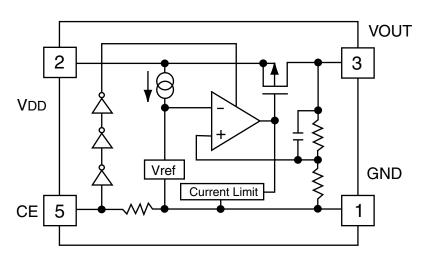

### ■ RN5RZ20BA-X(IC102) : High cycle module

### 1.Terminal layout

### 2.Block diagram

### 3.Pin function

| Pin No. | Pin name | Function             |  |  |  |

|---------|----------|----------------------|--|--|--|

| 1       | GND      | Ground terminal      |  |  |  |

| 2       | VDD      | Input terminal       |  |  |  |

| 3       | VOUT     | Output terminal      |  |  |  |

| 4       | NC       | No connection        |  |  |  |

| 5       | CE       | Chip enable terminal |  |  |  |

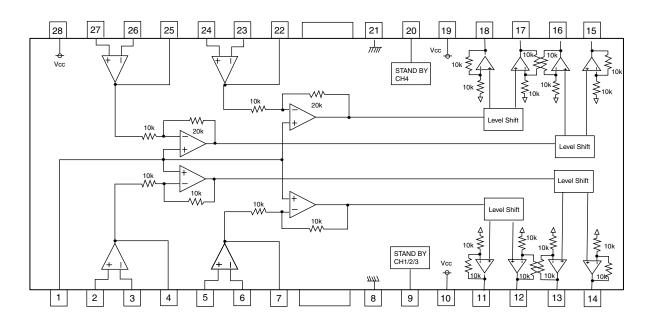

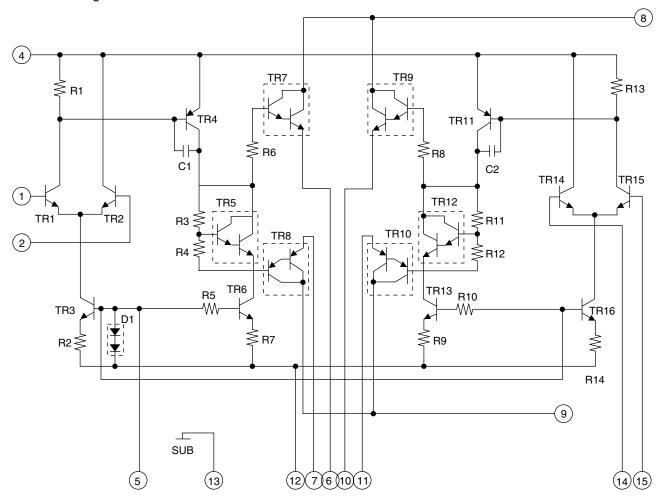

### ■ BA5983FM (IC271) : 4CH DRIVER

### 1.Block Diagram

### 2.Pin Function

| Pin No. | Symbol   | I/O | Function                           | Pin No. | Symbol   | I/O | Function                           |

|---------|----------|-----|------------------------------------|---------|----------|-----|------------------------------------|

| 1       | BLAS IN  | Ι   | Input for Bias-amplifier           | 15      | VO4(+)   | 0   | Non inverted output of CH4         |

| 2       | OPIN1(+) | 1   | Non inverting input for CH1 OP-AMP | 16      | VO4(-)   | 0   | Inverted output of CH4             |

| 3       | OPIN1(-) | _   | Inverting input for CH1 OP-AMP     | 17      | VO3(+)   | 0   | Non inverted output of CH3         |

| 4       | OPOUT1   | 0   | Output for CH1 OP-AMP              | 18      | VO3(-)   | 0   | Inverted output of CH3             |

| 5       | OPIN2(+) | _   | Non inverting input for CH2 OP-AMP | 19      | PowVcc2  | -   | Vcc for CH3/4 power block          |

| 6       | OPIN2(-) | _   | Inverting input for CH2 OP-AMP     | 20      | STBY2    | I   | Input for Ch4 stand by control     |

| 7       | OPOUT2   | 0   | Output for CH2 OP-AMP              | 21      | GND      | -   | Substrate ground                   |

| 8       | GND      | -   | Substrate ground                   | 22      | OPOUT3   | 0   | Output for CH3 OP-AMP              |

| 9       | STBY1    | Ι   | Input for CH1/2/3 stand by control | 23      | OPIN3(-) | ı   | Inverting input for CH3 OP-AMP     |

| 10      | PowVcc1  | -   | Vcc for CH1/2 power block          | 24      | OPIN3(+) | ı   | Non inverting input for CH3 OP-AMP |

| 11      | VO2(-)   | 0   | Inverted output of CH2             | 25      | OPOUT4   | 0   | Output for CH4 OP-AMP              |

| 12      | VO2(+)   | 0   | Non inverted outpur of CH2         | 26      | OPIN4(-) | I   | Inverting input for CH4 OP-AMP     |

| 13      | VO1(-)   | 0   | Inverted output of CH1             | 27      | OPIN4(+) | ı   | Non inverting input for CH4 OP-AMP |

| 14      | VO1(+)   | 0   | Non inverted outpur of CH1         | 28      | PreVcc   | -   | Vcc for pre block                  |

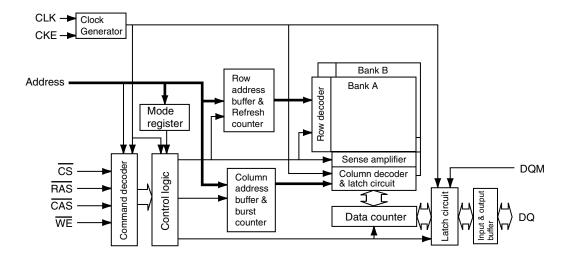

### ■ HY57V161610DTC8 or KM416S1120DT-G8 (IC504,IC505): 16MB SDRAM

### 1.Block diagram

### 2.Pin function

| Pin No. | Symbol | Description           | Pin No. | Symbol  | Description          |

|---------|--------|-----------------------|---------|---------|----------------------|

| 1       | VCC    | Power supply          | 26      | VSS     | Connect to GND       |

| 2,3     | DQ0,1  | Data input/output     | 27~32   | A4~9    | Address inputs       |

| 4       | VSS    | Connect to GND        | 33      | NC      | Non connect          |

| 5,6     | DQ2,3  | Data input/output     | 34      | CKE     | Clock enable         |

| 7       | VDD    | Power supply          | 35      | CLK     | System clock input   |

| 8,9     | DQ4,5  | Data input/output     | 36      | UDQM    | Upper DQ mask enable |

| 10      | VSS    | Connect to GND        | 37      | NC      | Non connect          |

| 11,12   | DQ6,7  | Data input/output     | 38      | VCC     | Power supply         |

| 13      | VCC    | Power supply          | 39,40   | DQ8,9   | Data input/output    |

| 14      | LDQM   | Lower DQ mask enable  | 41      | VSS     | Connect to GND       |

| 15      | WE     | Write enable          | 42,43   | DQ10,11 | Data input/output    |

| 16      | CAS    | Column address strobe | 44      | VDD     | Power supply         |

| 17      | RAS    | Row address strobe    | 45,46   | DQ12,13 | Data input/output    |

| 18      | CS     | Chip enable           | 47      | VSS     | Connect to GND       |

| 19,20   | A11,10 | Address inputs        | 48,49   | DQ14,15 | Data input/output    |

| 21~24   | A0~3   | Address inputs        | 50      | VSS     | Connect to GND       |

| 25      | VCC    | Power supply          |         |         |                      |

### ■ JCE8011(IC551):GRAPHIC CONTROLLER

| Pin No. | Symbol   | I/O | Function                                              |

|---------|----------|-----|-------------------------------------------------------|

| 1~8     | VD0~7    | 1   | DVD Image signal input (Multi plex data Y,Cr,Cb)      |

| 9       | VCLKI    | 1   | Dot clock signal input (27MHz)                        |

| 10      | HSYNCI   | - 1 | The horizontal synchronous signal input               |

| 11      | VSYNCI   | I   | Vertical synchronous signal input                     |

| 12      | VCC      | -   | Power supply                                          |

| 13      | VCLKD    | 0   | Dot clock signal output (27MHz)                       |

| 14      | HSYNCO   | 0   | 'H' blanking output                                   |

| 15      | VSYNCO   | 0   | 'V' blanking output                                   |

| 16~23   | DOUT0~7  | 0   | Digital data output                                   |

| 24      | TEST     | -   | Test terminal (Uses as GND usually)                   |

| 25      | RESETB   | Ι   | System reset signal                                   |

| 26      | GND      | -   | Connect to GND                                        |

| 27      | NTB      | I   | Mode switching NTSC(low) / PAL(high)                  |

| 28      | DTSF0    | I   | Taking timing shift of VD input                       |

| 29      | DTSFI    | - 1 | Taking timing shift of VD input                       |

| 30      | VIDEG    | I   | Taking edge specification of VD input (0:up , 1:down) |

| 31      | DOSF0    | 1   | Timing shift input of output data                     |

| 32      | DOSF1    | - 1 | Timing shift input of output data                     |

| 33      | XVRST    | 0   | Non connect                                           |

| 34      | F1       | 0   | Field Identification signal output                    |

| 35      | HBL      | 0   | 'H' blanking output                                   |

| 36      | VBL      | 0   | 'V' blanking output                                   |

| 37      | VOEDG    | I   | Output timing setting of DOUT (0:up , 1:down)         |

| 38      | VCC      | -   | Power supply                                          |

| 39~46   | FRD7~0   | I   | Field memory read data input                          |

| 47      | GND      | -   | Connect to GND                                        |

| 48      | FRCK     | 0   | Field memory read clock                               |

| 49      | FWCK     | 0   | Field memory write clock                              |

| 50      | FREB     | 0   | Field memory read enable                              |

| 51      | FWEB     | 0   | Field memory write enable                             |

| 52      | FRRSTB   | 0   | Field memory read address reset                       |

| 53      | FWRSTB   | 0   | Field memory write address reset                      |

| 54~61   | FWD7~0   | 0   | Field memory write data output                        |

| 62      | VCC      | -   | Power supply                                          |

| 63~70   | CHD7~0   | I   | Character ROM data                                    |

| 71      | GND      | -   | Connect to GND                                        |

| 72      | CHOEB    | 0   | Character ROM output enable                           |

| 73~82   | CHA19~10 | 0   | Character ROM address output                          |

| 83      | VCC      | -   | Power supply                                          |

| 84~93   | CHA9~0   | 0   | Character ROM address output                          |

| 94      | GND      | -   | Connect to GND                                        |

| 95      | ACK      | 0   |                                                       |

| 96      | CS1B     | I   | Serial data chip select for graphic control           |

| 97      | CS2B     | I   | Serial data chip select for encoder control           |

| 98      | SCK      | I   | Serial clock input                                    |

| 99      | RXD      | 1   | Serial input data                                     |

| 100     | TXD      | 0   | Serial output data                                    |

#### ■ MC44724AVFU (IC554) : VIDEO ENCODER CVBS/Cb/B2Vdd C/Cr/R2Vdd ] Y/G2Vdd **□**F/Vsync Hsync 1.Terminal layout 2.Block diagrams ]EXT 64 Y/G1Vdd CVBS/Cb/B1Vdd C/Cr/R1Vdd Y/G1 C/Cr/R1Vdd ChipA DVdd DVdd D 48 1 Sync\_ generator CCwss gen DVss 🗖 0 <del>1</del>≥ DVss □ 33 16 CVBS/Cb/B1 CVBS/Cb/B1 C/Cr/R1 DAC 17 32 H.V <sub>Y</sub> off\_set 0 🔼 DVIN[7:0] **┌** DEMAX TP[8:1] C/Cr/R1 Vref1 iBIAS1 TVIN Output Selector TP[0]IN sub carrier gen ☐ Y/G2 ☐ Y/G2 ☐ CVBS/Cb/B2 ☐ CVBS/Cb/B2 0⊒⊠ RGB matrix CVBS/CI C/Cr/R2 C/Cr/R2 Vref2 DAVdd DAVss 0-5 Clock [ Reset [ **TEST** 12C / SPI PAL/NTSC | SDA/SI SO SCL/SCK SEL TEST |

#### 3.Pin function

| <u> </u> |               | _   | · · · · · · · · · · · · · · · · · · ·       | ı - |         |     |                                                  |

|----------|---------------|-----|---------------------------------------------|-----|---------|-----|--------------------------------------------------|

| No.      | Symbol        | I/O | Function                                    | No. | Symbol  | I/O | Function                                         |

| 1        | CVBS/Cb/B1    | 0   | Analog composite drive signal (+)           | 33  | SO      | -   | Non connect                                      |

| 2        | CVBS/Cb/B1    | 0   | Analog composite drive signal (-)           | 34  | SDA/SI  | ı   | SPI Mode : Serial data input                     |

| 3        | CVBS/Cb/B1Vdd | -   | Power supply for CVBS/Cb/B DAC1             | 35  | SCL/SCK | ı   | Serial clock input                               |

| 4        | Y/G1          | 0   | Analog brightness signal/G drive signal (+) | 36  | SEL     | 1   | Power supply for serial data,chip select,digital |

| 5        | Y/G1          | 0   | Analog brightness signal/G drive signal (-) | 37  | DVdd    |     | Power supply for digital circuit                 |

| 6        | Y/G1/Vdd      | -   | Power supply for Y/G DAC                    | 38  | DVss    |     | Digital ground                                   |

| 7        | C/Cr/R1       | 0   | Analog chroma signal (+)                    | 39  | DVIN7   | I/O | Y data input / test data I/O                     |

| 8        | C/Cr/R1       | 0   | Analog chroma signal (-)                    | 40  | DVIN6   | 9   | Y data input / test data I/O                     |

| 9        | C/Cr/R1Vdd    | -   | Power supply for C/Cr/RDAC                  | 41  | DVIN5   | 9   | Y data input / test data I/O                     |

| 10       | DAVss         | -   | Connect to ground for DAC                   | 42  | DVIN4   | 9   | Y data input / test data I/O                     |

| 11       | TBIAS1        | 0   | Standard BIAS for DAC1                      | 43  | DVIN3   | I/O | Y data input / test data I/O                     |

| 12       | Vref1         | -   | Standard voltage for DAC1                   | 44  | DVIN2   | I/O | Y data input / test data I/O                     |

| 13       | DAVdd         | -   | Power supply for DAC                        | 45  | DVIN1   | I/O | Y data input / test data I/O                     |

| 14       | Vref2         | -   | Standard voltage for DAC2                   | 46  | DVIN0   | I/O | Y data input / test data I/O                     |

| 15       | TBIAS2        | 0   | Standard BIAS for DAC2                      | 47  | TVIN    | ı   | VIDEO mute on Reset(0:nomal, 1:mute)             |

| 16       | NC            | -   | Non connect                                 | 48  | EXT     | I/O | Frame output / VBI information input             |

| 17       | CVBS/Cb/B2    | 0   | Analog composite drive signal (+)           | 49  | F/Vsyac | I/O | Frame / Vertical, synchronous I/O                |

| 18       | CVBS/Cb/B2    | 0   | Analog composite drive signal (-)           | 50  | Chsyac  | I/O | The horizontal, synchronous I/O                  |

| 19       | CVBS/Cb/B2Vdd | -   | Power supply for CVBS/Cb/B DAC2             | 51  | DATST   | ı   | Data input                                       |

| 20       | Y/G2          | 0   | Analog brightness signal/G drive signal (+) | 52  | TP-8    | I/O | Multiplex data input                             |

| 21       | Y/G2          | 0   | Analog brightness signal/G drive signal (-) | 53  | TP7     | I/O | Multiplex data input                             |

| 22       | Y/GVdd        | -   | Power supply for Y/G DAC                    | 54  | TP6     | I/O | Multiplex data input                             |

| 23       | C/Cr/R2       | 0   | Analog chroma signal (+)                    | 55  | TP5     | I/O | Multiplex data input                             |

| 24       | C/Cr/R2       | 0   | Analog chroma signal (-)                    | 56  | DVss    | -   | Ground for digital circuit                       |

| 25       | C/Cr/R2Vdd    | -   | Power supply for C/Cr/RDAC2                 | 57  | DVdd    | -   | Power supply for digital circuit                 |

| 26       | ChipA         | -   | Chip address selection                      | 58  | TP4     | I/O | Data input / Test data I/O                       |

| 27       | TEST          | I   | Connect to test pin                         | 59  | TP3     | I/O | Data input / Test data I/O                       |

| 28       | DVdd          | -   | Digital ground                              | 60  | TP2     | I/O | Data input / Test data I/O                       |

| 29       | CLOCK         | I   | Clock signal input (27MHz)                  | 61  | TP1     | I/O | Data input / Test data I/O                       |

| 30       | DVss          | -   | Power supply for digital circuit            | 62  | TP0     | I/O | Data input / Test data I/O                       |

| 31       | Reset         | I   | Reset signal input L:ON                     | 63  | DLVdd   | -   | Power supply for D/A converter                   |

| 32       | PAL/NTSC      | I   | Selection NTSC/PAL NTSC:L PAL:H             | 64  | DLVss   | -   | Ground for D/A converter                         |

|          | 1             |     |                                             |     |         |     |                                                  |

### ■ MN102LP25G-01(IC401):UNIT CPU

| Pin No. | Symbol     | I/O | Function                     | Pin No.  | Symbol           | I/O      | Function                                        |

|---------|------------|-----|------------------------------|----------|------------------|----------|-------------------------------------------------|

| 1       | WAIT       | 1   | Micon wait signal input      | 51       | SWCLOSE          | ,, 0     | Detection switch of tray close                  |

| 2       | RE         | Ö   | Read enable                  | 52       | SWOPEN           | i        | Detection switch of tray open                   |

| 3       | MUTE       | ō   | Driver mute                  | 53       | ADSCEN           | Ö        | Serial enable signal for ADSC                   |

| 4       | WEM        | ō   | Write enable                 | 54       | VDD              | -        | Non connect                                     |

| 5       | CS0        | ō   | Non connect                  | 55       | EFPEN            | 0        | Serial enable signal for FEP                    |

| 6       | CS1        | ō   | Chip select for ODC          | 56       | SLEEP            | ō        | Standby signal for FEP                          |

| 7       | CS2        | ō   | Chip select for ZIVA         | 57       | BUSY             | Ĭ        | Communication busy                              |

| 8       | CS3        | ō   | Chip select for outer ROM    | 58       | REQ              | Ö        | Communication Request                           |

| 9       | TCLOSE     | ō   | Tray close signal output     | 59       | WEROM            | ō        | Non connect                                     |

| 10      | TOPEN      | ō   | Tray open signal output      | 60       | WPROM            | ō        | Non connect                                     |

| 11      | LSIRST     | Ĭ   | LSI reset                    | 61       | VSS              | -        | Power supply                                    |

| 12      | WORD       | Ö   | Bus selection input          | 62       | EECS             | 0        | Chip select signal for EEPROM                   |

| 13      | A0         | ō   | Address bus 0 for CPU        | 63       | EECK             | ō        | Clock signal for EEPROM                         |

| 14      | A1         | ō   | Address bus 1 for CPU        | 64       | EEDI             | Ť        | Input data for EEPROM                           |

| 15      | A2         | ō   | Address bus 2 for CPU        | 65       | EEDO             | Ö        | Output data for EEPROM                          |

| 16      | A3         | 0   | Address bus 3 for CPU        | 66       | VDD              | -        | Power supply                                    |

| 17      | VDD        | -   | Power supply                 | 67       | SCLK0            | ī        | Communication clock                             |

| 18      | SYSCLK     | 0   | System clock signal output   | 68       | S2UDT            | i        | Communication input data                        |

| 19      | VSS        | -   | Power supply                 | 69       | S2SDT            | 0        | Communication output data                       |

| 20      | XI         | -   | Non connect                  | 70       | CPSCK            | 0        | Clock for ADSC serial                           |

| 21      | XO         | -   | Non connect                  | 71       | SDIN             | Ť        | ADSC serial data input                          |

| 22      | VDD        | -   | Power supply                 | 72       | SDOUT            | 0        | ADSC serial data input  ADSC serial data output |

| 23      | OSCI       | 1   | Clock signal input(13.5MHz)  | 73       | 30001            | -        | Non connect                                     |

| 24      | OSCO       | -   | Non connect                  | 74       | -                | -        | Non connect                                     |

| 25      | MODE       | -   | CPU Mode selection input     | 75       | -<br>NMI         | -        | Non connect                                     |

| 26      | A4         | 0   | Address bus 4 for CPU        | 76       | ADSCIRQ          | -        | Interrupt input of ADSC                         |

| 27      |            | 0   | Address bus 5 for CPU        | 77       | ODCIRQ           | 1        | Interrupt input of ADSC                         |

| 28      | A5<br>A6   | 0   | Address bus 6 for CPU        | 78       |                  | 1        | Interrupt input of ZIVA                         |

| 29      |            | 0   | Address bus 7 for CPU        | 78       | DECIRQ<br>WAKEUP | 0        | Non connect                                     |

| 30      | A7         | 0   | Address bus 8 for CPU        | 80       |                  | <u> </u> | Non connect                                     |

| 31      | 8A         | 0   | Address bus 9 for CPU        |          | ODCIRQ2          | 1        |                                                 |

| 32      | A9         | 0   | Address bus 10 for CPU       | 81<br>82 | ADSEP<br>RST     | !        | Address data selection input Reset input        |

| 33      | A10<br>A11 | 0   | Address bus 11 for CPU       | 83       | VDD              | -        | Power supply                                    |

| 34      | VDD        | -   | Power supply                 |          | TEST1            | -        | Test signal 1 input                             |

| 35      |            | 0   | Address bus 12 for CPU       | 84       | TEST1            | !        | <u> </u>                                        |

| 36      | A12        | 0   |                              | 85       |                  | !        | Test signal 2 input                             |

| 37      | A13        |     | Address bus 13 for CPU       | 86       | TEST3            | !        | Test signal 3 input                             |

|         | A14        | 0   | Address bus 14 for CPU       | 87       | TEST4            |          | Test signal 4 input                             |

| 38      | A15        | 0   | Address bus 15 for CPU       | 88       | TEST5            |          | Test signal 5 input                             |

| 39      | A16        | 0   | Address bus 16 for CPU       | 89       | TEST6            |          | Test signal 7 input                             |

| 40      | A17        | 0   | Address bus 17 for CPU       | 90       | TEST7            |          | Test signal 7 input                             |

| 41      | A18        | 0   | Address bus 18 for CPU       | 91       | TEST8            | ı        | Test signal 8 input                             |

| 42      | A19        | 0   | Address bus 19 for CPU       | 92       | VSS              | -        | Power supply                                    |

| 43      | VSS        | -   | Power supply                 | 93       | D0               | 1/0      | Data bus 0 of CPU                               |

| 44      | A20        | 0   | Address bus 20 for CPU       | 94       | D1               | 1/0      | Data bus 1 of CPU                               |

| 45      | -          | -   | Non connect                  | 95       | D2               | 1/0      | Data bus 2 of CPU                               |

| 46      | STOP       | -   | Non connect                  | 96       | D3               | 1/0      | Data bus 3 of CPU                               |

| 47      | ADPD       | -   | Non connect                  | 97       | D4               | 1/0      | Data bus 4 of CPU                               |

| 48      | -          | -   | Non connect                  | 98       | D5               | 1/0      | Data bus 5 of CPU                               |

| 49      | -          | -   | Non connect                  | 99       | D6               | 1/0      | Data bus 6 of CPU                               |

| 50      | TRVSW      |     | Detection switch of traverse | 100      | D7               | I/O      | Data bus 7 of CPU                               |

|         |            |     | inside                       |          |                  |          |                                                 |

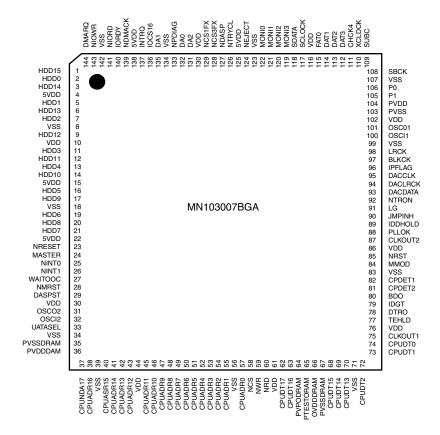

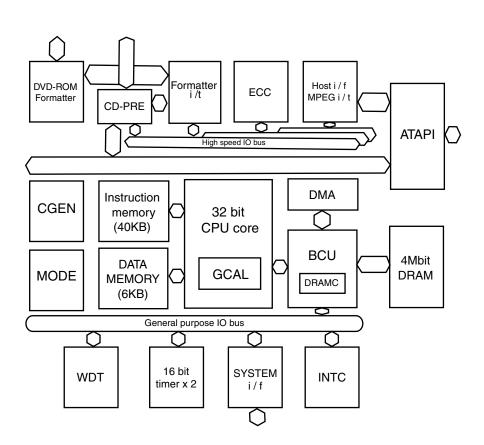

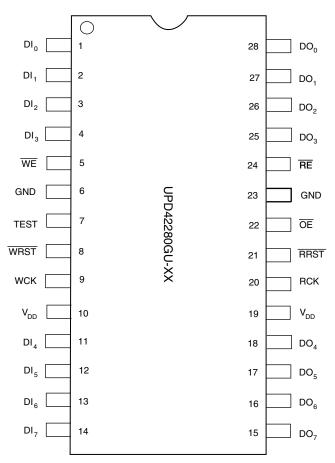

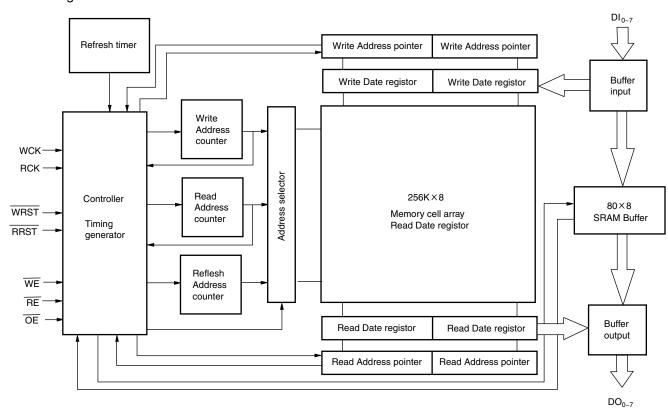

### MN103007BGA (IC301): Optical disc controller

#### 1.Terminal layout

### 3.Function

MN103007BGA(1/2)

|         |          |     |                                |         |           |     | MN103007BGA(1/2)               |

|---------|----------|-----|--------------------------------|---------|-----------|-----|--------------------------------|

| Pin NO. | Symbol   | I/O | Function                       | Pin NO. | Symbol    | I/O | Function                       |

| 1       | HDD15    | I/O | ATAPI data                     | 48      | CPUADR8   | ı   | System control address         |

| 2       | HDD0     | I/O | ATAPI data                     | 49      | CPUADR7   | I   | System control address         |

| 3       | HDD14    | I/O | ATAPI data                     | 50      | CPUADR6   | ı   | System control address         |

| 4       | 5VDD     |     |                                | 51      | CPUADR5   | ı   | System control address         |

| 5       | HDD1     | I/O | ATAPI data                     | 52      | CPUADR4   | ı   | System control address         |

| 6       | HDD13    | I/O | ATAPI data                     | 53      | CPUADR3   | ı   | System control address         |

| 7       | HDD2     | I/O | ATAPI data                     | 54      | CPUADR2   | ı   | System control address         |

| 8       | VSS      |     |                                | 55      | CPUADR1   | I   | System control address         |

| 9       | HDD12    | I/O | ATAPI data                     | 56      | VSS       |     | GND                            |

| 10      | VDD      |     |                                | 57      | CPUADR0   | ı   | System control address         |

| 11      | HDD3     | I/O | ATAPI data                     | 58      | NCS       | ı   | System control chip selection  |

| 12      | HDD11    | I/O | ATAPI data                     | 59      | NWR       | I   | System control wright          |

| 13      | HDD4     | I/O | ATAPI data                     | 60      | NRD       | ı   | System control lead            |

| 14      | HDD10    | I/O | ATAPI data                     | 61      | VDD       |     | Apply 3V                       |

| 15      | 5VDD     |     |                                | 62      | CPUDT7    |     | System control data            |

| 16      | HDD5     | I/O | ATAPI data                     | 63      | CPUDT6    |     | System control data            |

| 17      | HDD9     | I/O | ATAPI data                     | 64      | PVPPDRAM  | 0   | C=10000PF is connected         |

| 18      | VSS      |     |                                |         |           |     | between VSS                    |

| 19      | HDD6     | I/O | ATAPI data                     | 65      | PTESTDRAM |     | VSS connected                  |

| 20      | HDD8     | I/O | ATAPI data                     | 66      | OVDDDRAM  |     |                                |

| 21      | HDD7     | I/O | ATAPI data                     | 67      | PVSSDRAM  |     |                                |

| 22      | 5VDD     |     |                                | 68      | CPUDT5    |     | System control data            |

| 23      | NRESET   | I   | ATAPI reset                    | 69      | CPUDT4    |     | System control data            |

| 24      | MASTER   | I/O | ATAPI master / slave selection | 70      | CPUDT3    |     | System control data            |

| 25      | NINT0    | 0   | System control interruption 0  | 71      | VSS       |     | GND                            |

| 26      | NINT1    | 0   | System control interruption 1  | 72      | CPUDT2    |     | System control data            |

| 27      | WAITODC  | 0   | System control weight control  | 73      | CPUDT1    | I/O | System control data            |

| 28      | NMRST    | 0   | System control reset           | 74      | CPUDT0    | I/O | System control data            |

| 29      | DASPST   | I   | DASP signal initializing       | 75      | CLKOUT1   | 0   | 16.9/11.2/8.45MHz clock        |

| 30      | VDD      |     |                                | 76      | VDD       | -   | Apply 3V                       |

| 31      | OSCO2    | I,O | VSS connection,OPEN            | 77      | TEHLD     | 0   | Mirror gate                    |

| 32      | OSCI2    | I,O | VSS connection, OPEN           | 78      | DTRO      | 0   | Data part frequency control    |

| 33      | UATASEL  | ı   | VSS connection                 | 1       |           |     | switch                         |

| 34      | VSS      |     |                                | 79      | IDGT      | 0   | Part CAPA switch               |

| 35      | PVSSDRAM |     |                                | 80      | BDO       | ı   | RF dropout / BCA data of       |

| 36      | PVDODRAM |     |                                | 1       |           |     | making to binary               |

| 37      | CPUADR17 | ı   | System control address         | 81      | CPDET2    | ı   | Outer side CAPA detection      |

| 38      | CPUADR18 | ı   | System control address         | 82      | CPDET1    | ı   | Side of surroundings on inside |

| 39      | VSS      |     |                                | 83      | VSS       |     | GND                            |

| 40      | CPUADR15 | ı   | System control address         | 84      | MMOD      | I   | VSS connected                  |

| 41      | CPUADR14 | ı   | System control address         | 85      | NRST      | I   | System reset                   |

| 42      | CPUADR13 | I   | System control address         | 86      | VDD       | -   | Apply 3V                       |

| 43      | CPUADR12 | I   | System control address         | 87      | CLKOUT2   | 0   | 16.9MHz clock                  |

| 44      | VDD      |     | System control address         | 88      | PLLOK     | 0   | Frame mark detection           |

| 45      | CPUADR11 | I   | System control address         | 89      | IDOHOLD   | 0   | ID gate for tracking holding   |

| 46      | CPUADR10 | Ī   | System control address         | 90      | JMPINH    | 0   | Jump prohibition               |

| 47      | CPUADR9  | I   | System control address         |         |           |     |                                |